# Thesis work for the degree of Licentiate of Technology Sundsvall 2012

# Maintenance Consideration for Long Life Cycle Embedded System

Xiaozhou Meng

Supervisors: Dr. Benny Thörnberg

Professor Mattias O'Nils

Electronics Design Division, in the Department of Information Technology and Media Mid Sweden University, SE-851 70 Sundsvall, Sweden

ISSN 1652-8948 Mid Sweden University Licentiate Thesis 81

ISBN 978-91-87103-14-8

| Akademisk avhandling som med tillstånd av Mittuniversitetet i Sundsvall framläggs till offentlig granskning för avläggande av teknologie Licentiate examen i elektronik torsdag den 24 Maj 2012, klockan 10:15 i sal O102, Mittuniversitetet Sundsvall. Seminariet kommer att hållas på engelska. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maintenance Consideration for Long Life Cycle Embedded<br>System                                                                                                                                                                                                                                  |

| Xiaozhou Meng<br>© Xiaozhou Meng, 2012                                                                                                                                                                                                                                                            |

Electronics Design Division, in the Department of Information Technology and Media Mid Sweden University, SE-851 70 Sundsvall Sweden

Telephone: +46 (0)60 148592

Printed by Kopieringen Mittuniversitetet, Sundsvall, Sweden, 2012

#### **ABSTRACT**

In this thesis, the work presented is in relation to consideration to the maintenance of a long life cycle embedded system. Various issues can present problems for maintaining a long life cycle embedded system, such as component obsolescence and IP (intellectual property) portability.

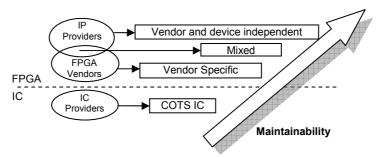

For products including automotive, avionics, military application etc., the desired life cycles for these systems are many times longer than the obsolescence cycle for the electronic components used in the systems. The maintainability is analyzed in relation to long life cycle embedded systems for different design technologies. FPGA platform solutions are proposed in order to ease the system maintenance. Different platform cases are evaluated by analyzing the essence of each case and the consequences of different risk scenarios during system maintenance. This has shown that an FPGA platform with a vendor and device independent soft IP has the highest maintainability.

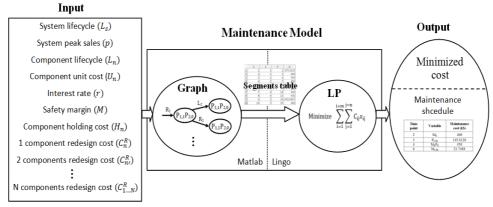

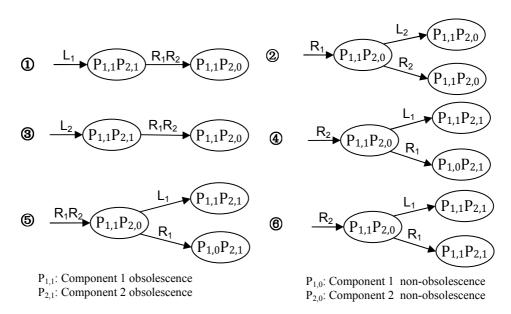

A mathematic model of obsolescence management for long life cycle embedded system maintenance is presented. This model can estimate the minimum management costs for the different system architecture and this consists of two parts. The first is to generate a graph in Matlab which is in the form of state transfer diagram. A segments table is then output from Matlab for further optimization. The second part is to find the lowest cost in the state transfer diagram, which can be viewed as a transshipment problem. Linear programming is used to calculate the minimized management cost and schedule, which is solved by Lingo. A simple Controller Area Network (CAN) controller system case study is shown in order to apply this model. The model is validated by a set of synthetic and experimentally selected values. The results provided by this are a minimized management cost and an optimized management time schedule. Test experiments of the maintenance cost responding to the interest rate and unit cost are implemented. The responses from the experiments meet our expectations.

The reuse of predefined IP can shorten development times and assist the designer to meet time-to-market (TTM) requirements. System migration between devices is unavoidable, especially when it has a long life cycle expectation, so IP portability becomes an important issue for system maintenance. An M-JPEG decoder case study is presented in the thesis. The lack of any clear separation between computation and communication is shown to limit the IP's portability with respect to different communication interfaces. A methodology is proposed to ease the interface modification and interface reuse, thus to increase the portability of an IP. Technology and tool dependent firmware IP components are also shown to limit the IP portability with respect to development tools and FPGA vendors.

#### SAMMANFATTNING

Denna avhandling beskriver de problem som specifikt kan uppstå vid underhåll av produkter med inbyggd elektronik och som har en lång livscykel på marknaden. Att de ingående elektroniska komponenterna ej längre finns att köpa eller att (Intellectual Property) IP-komponenter ej är portabla är några av de problem som kan uppstå.

Livscykeln för elektroniska produkter inom ex. fordon, flyg eller militär industri är oftast många gånger längre än livscykeln för de komponenter som ingår. Svårighetsgraden för underhåll av inbyggd elektronik analyseras med avseende på olika designteknologier. Programmerbara grindmatriser, FPGA förslås vara en kretsteknologi som underlättar underhåll. Olika konstruktionsplattformar utvärderas utifrån ett antal riskscenarion och dess påföljande konsekvenser. Studien visar att FPGA-teknologin med fabrikatoch kretsoberoende mjuka IP-komponenter är den designteknologi som resulterar i lägst svårighetsgrad för produktunderhåll.

En matematisk modell för minimering av kostnader orsakade av åtgärder för produktunderhåll presenteras. Modellen väljer och schemalägger ett antal underhållsåtgärder under tiden för produktens hela förväntade livscykel. På så sätt kan den totala kostnaden för produktens underhåll minimeras. Utifrån parametrar så som kostnader för omkonstruktion, lagerhållning, ränta och de ingående komponenternas förväntade livscykel genereras en tillståndsgraf i Matlab. Linjärprogrammering används därefter för att välja den kombination av underhållsåtgärder som ger lägst kostnad. Vi kan visa att ett enkelt inbyggt system bestående av en mikroprocessor och en periferienhet kan analyseras med den utvecklade modellen.

Återanvändning av IP-komponenter kan korta utvecklingstider för inbyggda elektroniksystem och underlätta för företag att snabbt nå marknader med sina produkter. I de fall produkten har en lång livscykel blir det oundvikligt att någon gång behöva flytta systemet till en ny typ av krets. IP-komponenternas portabilitet blir därför en viktig parameter när svårigheter för underhåll av en produkt skall analyseras. Brist på tydlig separation mellan beskrivning av beräkning och kommunikation begränsar IP-komponenternas portabilitet med avseende på val av kommunikationsinterface. En metodologi föreslås i syfte att underlätta modifiering av IP-komponenternas kommunikationsinterface. Teknologi- och verktygsberoende beskrivningar av IP-komponenter är också begränsande för dess portabilitet med avseende på utvecklingsverktyg och kretsfabrikat.

## **ACKNOWLEDGEMENTS**

This research work would not have been possible without the support of many people. I wish to my express deepest regards and gratitude to my supervisor Dr. Benny Thörnberg who was abundantly helpful and offered invaluable assistance, support and guidance. Deepest gratitude are also due to Prof. Mattias O'Nils and Dr. Najeem Lawal, without whose knowledge and assistance this study would not have been successful.

I am thankful to Fanny Burman and Carolina Blomberg for the administrative support.

Further, I am thankful to my friends and colleagues Abdul Waheed Malik, Khursheed Khursheed, Muhammad Imran, Naeem Ahmad, Mohammad Anzar Alam, Jinlan Gao, Xin Cheng, Omeime Esebamen, Mazhar Hussain and all the colleagues in the department for their discussions and cooperation.

I would also like to express my gratitude to Mid Sweden University (miun), Knowledge Foundation (KK) for their financial and administrative support.

I am forever indebted to my parents for their understanding, endless patience and encouragement when it was most required.

Finally, I wishes to express my love and gratitude to my wife Yue Peng; for her understanding and endless love, through the duration of my studies.

Sundsvall, March 2012

Xiaozhou Meng

# **TABLE OF CONTENTS**

| A | BSTRACT.  |                                                   | III |

|---|-----------|---------------------------------------------------|-----|

| S | AMMANFA   | TTNING                                            | V   |

| Α | CKNOWLE   | DGEMENTS                                          | VII |

| Т | ABLE OF C | CONTENTS                                          | IX  |

|   |           | IONS AND ACRONYMS                                 |     |

|   |           | URES                                              |     |

|   |           |                                                   |     |

| L |           | BLES                                              |     |

| 1 | INTROD    | UCTION                                            | 1   |

|   | 1.1 EM    | BEDDED SYSTEM                                     |     |

|   | 1.1.1     | Embedded system overview                          |     |

|   | 1.1.2     | Design goals for an embedded system               |     |

|   |           | BEDDED SYSTEM HARDWARE PLATFORM                   |     |

|   | 1.2.1     | Bus based embedded system                         |     |

|   | 1.2.2     | COTS IC hardware platforms                        |     |

|   | 1.2.3     | Programmable hardware platforms                   |     |

|   |           | VELOPMENT ENVIRONMENT                             |     |

|   |           | OBLEM DESCRIPTION AND MOTIVATION                  |     |

|   |           | IN CONTRIBUTIONS                                  |     |

|   | 1.6 THE   | ESIS OUTLINE                                      | 6   |

| 2 | MAINTA    | NACE ISSUES FOR EMBEDDED SYSTEM                   | 9   |

|   | 2.1 ELE   | ECTRONIC COMPONENT LIFE CYCLE CONCEPTS            | g   |

|   | 2.2 OB    | SOLESCENCE PROBLEM FOR EMBEDDED SYSTEM            | 11  |

|   |           | HERS MAINTENANCE ISSUES                           |     |

|   |           | NCLUSION                                          |     |

| ^ |           | NNABILITY ANALYSIS OF CAN CONTROLLER SYSTEMS.     |     |

| 3 |           |                                                   |     |

|   |           | N BUS                                             |     |

|   |           | SIGN CASES                                        |     |

|   | 3.2.1     | Case 1: COTS IC based CAN controller system       |     |

|   | 3.2.2     | Case 2: vendor specific FPGA system               |     |

|   | 3.2.3     | Case 3: vendor and device independent FPGA system |     |

|   | 3.2.4     | Case 4: mixed FPGA system                         |     |

|   | 3.3 PR    | OTOTYPE OF FPGA BASED CAN CONTROLLER SYSTEM       |     |

|   | 3.4 Ris   | K ANALYSIS                                        |     |

|   | 3.4.1     | Risk scenarios                                    |     |

|   | 3.4.2     | Consequences                                      |     |

|   |           | SULT                                              |     |

|   |           | INTAINABILITY FOR DIFFERENT DESIGN CASES          |     |

|   | 3.6.1     | COTS IC platform                                  |     |

|   | 3.6.2     | Software issue for maintainability                |     |

|   | 363       | FPGA platform                                     | 26  |

|   | 3.7 Cc         | ONCLUSION                                                       | 27 |

|---|----------------|-----------------------------------------------------------------|----|

| 4 | FPGA I         | P PORTABILITY ANALYSIS                                          | 29 |

|   | 4.1 INT        | FELLECTUAL PROPERTY                                             | 29 |

|   |                | OJECT BACKGROUND                                                |    |

|   |                | JPEG DECODER                                                    |    |

|   |                | PRTABILITY ANALYSIS                                             |    |

|   |                | IALYSIS RESULTS                                                 |    |

|   | 4.5.1          | Portability with respect to FPGA vendor and tool/library        |    |

|   | 4.5.2          | Portability with respect to communication interfaces            |    |

|   |                | FT-IP INTERFACE MODIFICATION METHODOLOGY                        | 34 |

|   | 4.6.1          | IP verification                                                 |    |

|   | 4.6.2          | Interface-based soft IP model                                   |    |

|   | 4.6.3          | Interface modification                                          |    |

|   | 4.6.4          | IP integration                                                  |    |

|   |                | TERFACES MODIFICATION OF M-JPEG DECODER                         | 36 |

|   | 4.7.1          | IP verification                                                 |    |

|   | 4.7.2          | Interface-based soft IP model                                   |    |

|   | 4.7.3          | Interface modification                                          |    |

|   | 4.7.4          | IP integration                                                  |    |

|   | 4.8 Cc         | DNCLUSION                                                       |    |

| 5 |                | ONENT OBSOLESCENCE MANAGEMENT MODEL FOR LONYCLE EMBEDDED SYSTEM |    |

|   |                | DL SOLUTIONS                                                    |    |

|   | 5.1 EC         | Lifetime buy and Last-Time-Buy                                  |    |

|   | 5.1.1<br>5.1.2 | Redesign                                                        |    |

|   | 5.1.2<br>5.1.3 | Others                                                          |    |

|   |                | AINTENANCE MODEL                                                |    |

|   | 5.2.1          | Overview                                                        |    |

|   | 5.2.2          | State transfer diagram                                          |    |

|   | 5.2.3          | Cost estimation                                                 |    |

|   | 5.2.4          | Linear programming                                              |    |

|   | -              | SE STUDY                                                        |    |

|   | 5.3.1          | Experimental system                                             |    |

|   | 5.3.2          | Model validation experiment                                     |    |

|   | 5.3.3          | Model response analysis                                         |    |

|   | 5.3.4          | Result                                                          |    |

|   |                | DNCLUSION                                                       |    |

| 6 | THESIS         | SUMMARY                                                         | 55 |

|   | 6.1 Cc         | ONCLUSION                                                       | 56 |

|   |                | TURE WORKS                                                      |    |

| 7 | SUMMA          | ARY OF PUBLICATIONS                                             | 57 |

|   | 7.1 PA         | PER                                                             | 57 |

|   |                | PER II                                                          |    |

|   |                | PER III                                                         |    |

|   |                | PER IV                                                          |    |

| 7.5   | AUTHORS CONTRIBUTIONS. | 57                           |

|-------|------------------------|------------------------------|

| 8 RE  | FERENCES               | 59                           |

| PAPER | I                      | ERROR! BOOKMARK NOT DEFINED. |

| PAPER | II                     | ERROR! BOOKMARK NOT DEFINED. |

| PAPER | III                    | ERROR! BOOKMARK NOT DEFINED. |

| PAPER | IV                     | ERROR! BOOKMARK NOT DEFINED. |

# **ABBREVIATIONS AND ACRONYMS**

| ADC    | <br>Analog to Digital Convertor                       |

|--------|-------------------------------------------------------|

| AMS    | <br>Analog/Mixed-Signal                               |

| ASIC   | <br>Application Specific Instruction set Processor    |

| BRAM   | <br>Block RAM                                         |

| CAN    | <br>Controller Area Network                           |

| COTS   | <br>Commercial Off-The-Shelf                          |

| CMOS   | <br>Complimentary Metal-Oxide Semiconductor           |

| CPLD   | <br>Complex Programmable Logic Device                 |

| CPU    | <br>Central Processing Unit                           |

| DAC    | <br>Digital to Analog Convertor                       |

| DCR    | <br>Device Control Register                           |

| DMA    | <br>Direct Memory Access                              |

| DRAM   | <br>Dynamic RAM                                       |

| DSP    | <br>Digital Signal Processing                         |

| EDK    | <br>Embedded Development Kit                          |

| EEPROM | <br>Electrically Erasable Programmable Read-Only      |

|        | Memory                                                |

| EIA    | <br>Electronic Industries Association                 |

| EOI    | <br>End of Image                                      |

| EOL    | <br>End of Life                                       |

| FIFO   | <br>First In First Out                                |

| FPGA   | <br>Field Programmable Gate Array                     |

| FSL    | <br>Fast Simplex Link                                 |

| HDL    | <br>Hardware Description Language                     |

| HDMI   | <br>High-Definition Multimedia Interface              |

| IC     | <br>Integrated Circuits                               |

| IEEE   | <br>Institute of Electrical and Electronics Engineers |

| IP     | <br>Intellectual Property                             |

| ISA    | <br>Industry Standard Architecture                    |

| JPEG   | <br>Joint Photographic Experts Group                  |

| JTAG   | <br>Joint Test Action Group                           |

| LGPL   | <br>GNU Lesser General Public License                 |

| LP     | <br>Linear Programming                                |

| LTB    | <br>Last Time Buy                                     |

| MCU    | <br>Micro-Controller Unit                             |

| MDM    | <br>MicroBlaze Debug Module                           |

| MJPEG  | <br>Motion Joint Photographic Experts Group           |

| MMU    | <br>Memory Management Unit                            |

| NPI    | <br>Native Port Interface                             |

| OPB    | <br>On-chip Peripheral Bus                            |

|        |                                                       |

PC ..... Personal Computer

PCI Peripheral Component Interconnect

PLB Processor Local Bus

PLC Product Life Cycle

PLD ...... Programmable Logic Device

PROM ...... Programmable Read-Only Memory

RAM ..... Random Access Memory

RF ...... Radio Frequency

RGB ..... Red Green Blue

RISC ...... Reduced Instruction Set Computing

ROM ...... Read Only Memory

RTL ...... Register Transfer Level

SDRAM ...... Synchronous Dynamic Random Access Memory

SOC ..... System on Chip

SPI Serial Peripheral Interface

SRAM Static Random Access Memory

TFT ...... Thin-Film Transistor TTM ...... Time to Market

UART ...... Universal Asynchronous Receiver/Transmitter

USB ...... Universal Serial Bus VGA Video Graphics Array

# **LIST OF FIGURES**

| Figure 1-1. Block diagram of embedded system                             | 2         |

|--------------------------------------------------------------------------|-----------|

| Figure 1-2. System architecture of bus based FPGA system                 | 3         |

| Figure 1-3. Typical embedded system design environment                   | 5         |

| Figure 2-1. Standardized life cycle curve for a device/technology grou   | p9        |

| Figure 3-1. Block diagram of COTS based CAN controller system            | 16        |

| Figure 3-2. System architecture of Xilinx specific FPGA system           | 16        |

| Figure 3-3. Architecture of Microblaze soft microprocessor               | 17        |

| Figure 3-4. Architecture of OpenRISC 1200                                | 18        |

| Figure 3-5. System architecture of OpenCores based FPGA system           | 19        |

| Figure 3-6. System architecture of Xilinx and OpenCores mixed FPG.       | A system  |

|                                                                          | 19        |

| Figure 3-7. FPGA based CAN controller system prototype                   | 20        |

| Figure 3-8. Risk analysis for different cases                            | 21        |

| Figure 3-9. System maintainability model for different design technology | ogies 24  |

| Figure 4-1. IP portability issue for system designers                    | 29        |

| Figure 4-2. Architecture of the real-time display of multiple video stre | ams 30    |

| Figure 4-3. Block diagram of the decoder project                         | 31        |

| Figure 4-4. Internal data flow graph of the M-JPEG decoder               |           |

| Figure 4-5. A generalized interface-based soft IP model                  | 35        |

| Figure 4-6. IPC design with a dummy function in the computation blo      | ck36      |

| Figure 4-7. Interface design with dummy functions in the computatio      | nal block |

|                                                                          | 36        |

| Figure 4-8. Block diagram of complete SOC including the updated de       | ecoder IP |

|                                                                          |           |

| Figure 4-9. Interface-based soft IP model for an M-JPEG decoder          |           |

| Figure 5-1. Maintenance model overview                                   |           |

| Figure 5-2. State transfer diagram                                       | 42        |

| Figure 5-3. State transfer path duplication                              |           |

| Figure 5-4. CAN controller system architecture                           |           |

| Figure 5-5. CAN controller system state transfer graph generated by I    |           |

| Figure 5-6. Final CAN controller system state transfer graph             |           |

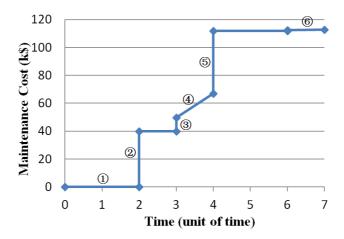

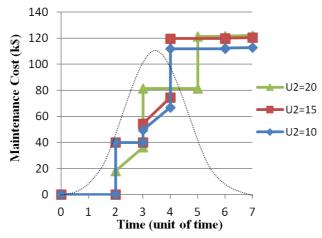

| Figure 5-7. Maintenance cost VS Time curve                               |           |

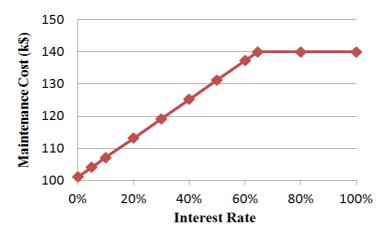

| Figure 5-8. Maintenance cost VS Interest rate curve                      | 51        |

| Figure 5-9 Maintenance cost VS Time comparison curve                     | 52        |

# LIST OF TABLES

| Table 3-1. Consequences of different risk scenarios                          | 24 |

|------------------------------------------------------------------------------|----|

| Table 4-1. Portability analysis with respect to FPGA vendor and tool/library | 33 |

| Table 5-1. Input parameter                                                   | 46 |

| Table 5-2. Maintenance schedule                                              | 50 |

| Table 5-3. Maintenance schedule for different unit price                     | 51 |

| Table 7-1. Authors' contributions                                            | 58 |

## **LIST OF PAPERS**

This thesis is mainly based on the following four papers, herein referred to by their Roman numerals:

# Paper I Embedded System Design with Maintenance Consideration

Xiaozhou Meng, Benny Thörnberg, Najeem Lawal 34th International Convention on Information and Communication Technology, Electronics and Microelectronics, Opatija, Croatia, May 23-27, 2011

## Paper II Soft-IP Interface Modification Methodology

Xiaozhou Meng, Benny Thörnberg, Najeem Lawal Proc of 2011 International Conference on Information and Electronics Engineering, Bankok, Thailand, May 28-29, 2011

# Paper III Portability analysis of an M-JPEG decoder IP from OpenCores

Xiaozhou Meng, Benny Thörnberg, Najeem Lawal Proc. of 6th IEEE International Symposium on Industrial Embedded Systems, Vasteras, Sweden, Jun 15-17, 2011

# Paper IV Component Obsolescence Management Model for Long Life Cycle Embedded System

Xiaozhou Meng, Benny Thörnberg, Leif Olsson Submitted to IEEE Autotestcon 2012, Anheim, California, Sep 10-13. 2012

Related papers not included into this thesis:

# Real-time Machine Vision System Using FPGA and Soft-core Processor

Abdul Waheed Malik, Benny Thörnberg, Xiaozhou Meng, Muhammad Imran

Accepted for publication in proceeding of Real-Time Image and Video Processing conference, SPIE Photonics Europe, April 15-19, 2012

#### 1 INTRODUCTION

#### 1.1 EMBEDDED SYSTEM

The embedding of microprocessors into equipment and consumer appliances started before the appearance of the PC (Personal Computer) and this process consumes the majority of microprocessors that are made today. In this way, embedded microprocessors are more deeply ingrained into everyday life than any other electronic circuit. For instance, in a well-equipped car, nearly every aspect has some form of electronic control associated with it and thus there is the need for a microprocessor within an embedded system. [1]

# 1.1.1 Embedded system overview

An embedded system is a kind of computer system with either one or a few dedicated specific functions. It is often embedded as part of a complete device including hardware and mechanical parts.

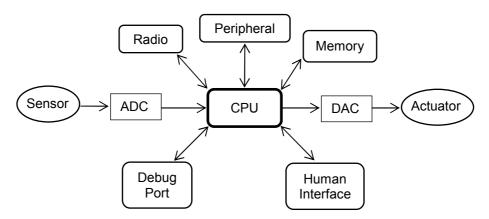

- An embedded system is controlled by one or more main processing cores such as microprocessor or digital signal processors (DSP), described in Figure 1-1. Microprocessors come in many different levels of sophistication and are usually classified by their word size [2].

- ➤ An 8-bit microprocessor is designed for low-cost applications.

- ➤ A 16-bit microprocessor is often used for more sophisticated applications that may require either longer word lengths or off-chip I/O and memory.

- ➤ A 32-bit RISC (Reduced Instruction Set Computing) microprocessor offers very high performance for computation-intensive applications.

- Embedded systems usually contain a memory chip. The memory can be either on-chip or off-chip. [3]

- ➤ Internal RAM (Random Access Memory) in a microprocessor is for register.

- ➤ Internal ROM (Read Only Memory) is for program

- External RAM is for the temporary data and stack

- Internal caches (in some microprocessor)

- ➤ EEPROM (Electrically Erasable Programmable Read-Only Memory) or flash memory is for data saving

- ➤ External ROM or PROM (Programmable Read-Only Memory) is for software

- > RAM memory buffers at the interface ports

- Embedded system can communicate via peripherals, e.g. RS-232, Ethernet, CAN (Controller Area Network) bus.

- Radio transceiver can be integrated into the system. E.g. RF (Radio Frequency) transmitter, Bluetooth transmitter.

- Analogue ADC (Analog to Digital Convertor) converts an analogue signal from a sensor to a digital signal for data processing by the embedded system. Also, DAC (Digital to Analog Convertor) can convert a digital signal to an analogue signal for the actuator.

- An embedded system usually contains one or more debug ports for system debugging.

- Human interface such as the TFT (Thin-Film Transistor) monitor, in which the keyboard is the communication channel between a human and the embedded system. E.g. TFT monitor, keyboard.

- Others hardware unit such as timers, interrupt handler etc. and are not shown in the figure.

Figure 1-1. Block diagram of embedded system

A microcontroller (MCU) is a single chip containing a microprocessor, memory, timers, interrupt controller, and peripheral for different requirement etc. MCU is used in embedded system for automatic control or communication.

Software is also an important part for embedded system, however in this thesis we will focus on hardware part.

Embedded systems are widely used in commercial electronic, industry systems, avionics etc. They can be divided into several application types:

# General purpose system:

- Functions are similar to those for a PC but in an embedded package.

- Video game console, set-top boxes, tablet

#### Control system:

- Real-time system

- Vehicle engines control system, flight control system

Signal processing system:

- Large data stream and significant computation

- Video decoder, radar

Communication system:

- Information switching and transmission

- Telephone system, network router

# 1.1.2 Design goals for an embedded system

A system design process has several important goals:

- Function: Mobile phone, Vehicle control etc.

- Performance: Clock frequency, response time etc.

- Manufacturing cost: Important for a consumer product to have a low retail price.

- Power consumption: Especially important for handheld devices.

- TTM: The profitable market life is time limited.

- Design cost: Development environment and engineering costs.

- Quality: Reliability, usability etc.

- Others: Maintainability, security.

## 1.2 EMBEDDED SYSTEM HARDWARE PLATFORM

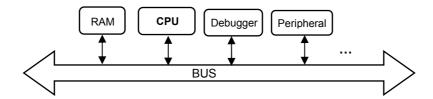

The hardware architecture of the embedded system can be formed as a bus based system, see Fig.1-2. There could be different hardware technology platforms for an embedded system, including Application-Specific Integrated Circuit (ASIC), Field Programmable Gate Array (FPGA).

# 1.2.1 Bus based embedded system

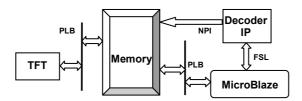

Figure 1-2. System architecture of bus based FPGA system

In this thesis, the embedded system hardware architecture is considered as a bus based system. The bus is the mechanism by which the CPU communicates with others devices in the system [2]. The bus forms the backbone of the hardware system. One of the major roles of the bus is to provide an interface in relation to the memory and other devices. Each component requires interface protocol logic to connect to the bus.

# 1.2.2 COTS IC hardware platforms

COTS is short for Commercial Off-The-Shelf, which means products that are ready-made and available for sale to the general public. A modern embedded system designer would prefer to use COTS IC to implement embedded system, such as MCU, DDR-SDRAM etc. These will provide the best performance and lowest power consumption since their functions and performance are analyzed before their fabrication.

# 1.2.3 Programmable hardware platforms

A programmable logic device or PLD is an electronic component used to build reconfigurable digital circuits. A PLD has an undefined function at the time of manufacture. The function can be defined and programmed by the user (designer) such as FPGA or CPLD (Complex Programmable Logic Device). There are several basic process technology types for FPGA including Flash , Anitfuse , EEPROM, SRAM. An antifuse based FPGA is one-time programmable, while the others are re-programmable. In this thesis, the FPGAs mentioned are those of the re-programmable type.

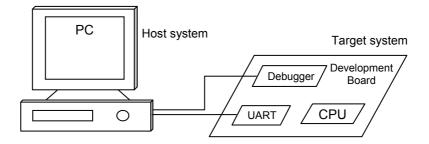

# 1.3 DEVELOPMENT ENVIRONMENT

A typical embedded system design environment is shown in Fig.1-3. The software and hardware (e.g. FPGA) development is implemented in a PC, known as a host system which is illustrated in Fig.1-3. The hardware on which the code will finally run is known as the target system. The target system connects to the host system via a UART (Universal Asynchronous Receiver/Transmitter), debugger or Ethernet etc.

The main tasks of the host system include:

- Program hardware for the target (FPGA)

- Load software programs into the target

- Start and stop program execution on the target

- Examine memory and registers on the target

- Receive debugging information from the target

Figure 1-3. Typical embedded system design environment

#### 1.4 PROBLEM DESCRIPTION AND MOTIVATION

Some products are not as capable of adjusting to leading-edge technology as others and to catching the development pace of consumer products. For products such as automotive, avionics, military application etc., the desired life cycle for these systems is significantly longer than the life cycle for the electronic components used in the systems. The life cycle in this thesis refers to the product field life. It is the time period for which the product is available on the market. Component obsolescence problems occur in all systems with a life cycle longer than that of one or more of their components. No publication yet offers an obsolescence management solution in relation to controlling the system maintenance costs.

The reuse of predefined Intellectual Property (IP) can lead to great success in system design and can assist the designer in meeting the TTM requirements. It is true that using IPs based FPGA device can mitigate the component obsolescence problem. However, the designer will still encounter problems if this is not used correctly. The lack of any clear separation between computation and communication will limit the IP's portability with respect to different communication interfaces. Technology and tool dependent firmware IP will limit the IP's portability with respect to development tools and FPGA vendors.

In addition to obsolescence, a system will require re-engineering if its requirements change over time or if it becomes necessary to change the specifications. The availability of newer and better architectures (processors, interconnections and interface blocks) can provide the motivation for a reengineering of a product. System migration between devices during the system life cycle is unavoidable.

Based on these considerations, it is important that the IP has a high portability in order to maintain a long life cycle embedded system.

In this thesis, the maintenance issues including component obsolescence and IP portability etc. are discussed. Suggestions and a mathematic model are proposed in order to ease the maintenance problem for a long life cycle embedded system.

#### 1.5 Main contributions

In this thesis, maintenance issues regarding to component obsolescence and IP portability are analyzed. A mathematic model for component obsolescence management is proposed.

- I. Maintenance issues for an embedded system are presented. An analysis is conducted in relation to the maintainability of long life cycle embedded systems for different design technologies. The result shows that an FPGA platform with a vendor and device independent soft IP provides the highest maintainability.

- II. A soft IP interface modification methodology for systems on FPGA is suggested. The methodology will ease the interface modification and interface reuse for an FPGA soft IP.

- III. Maintenance issues associated with the IPs portability for the embedded FPGA system are highlighted. The lack of any clear separation between computation and communication is shown to limit the IP's portability with respect to different communication interfaces. Technology and tool dependent firmware specifications within a soft IP are also shown to limit the IP portability with respect to development tools and FPGA vendors.

- IV. A mathematic model for a life cycle analysis of the long life cycle embedded system maintenance is proposed. This model is able to estimate the minimized maintenance cost caused by component obsolescence for different system architectures. An optimized maintenance schedule will also be provided by the model. It can offer maintenance strategy guidance to those designers who encounter a components obsolescence problem.

# 1.6 THESIS OUTLINE

Chapter 1 provides the introduction, chapter 2 addresses the maintenance issues for the embedded system, chapter 3 focuses on the maintainability analysis of the CAN controller system, chapter 4 presents a portability analysis of an FPGA IP, chapter 5 describes a component obsolescence management model for the long life cycle embedded system, chapter 6 concludes the thesis summary while chapter

7 presents a publications summary. Papers which are basis for this research work are listed at the conclusion part.

#### 2 MAINTAINACE ISSUES FOR EMBEDDED SYSTEM

Modern embedded system designers consider various metrics during the design process, including performance, cost, power etc. However, one issue is often missing from this list, namely maintainability. Due to the rapid development in electronic technology, obsolescence and upgrade are inevitable for the majority of embedded systems which may create a variety of problems when maintaining a long life cycle system.

# 2.1 ELECTRONIC COMPONENT LIFE CYCLE CONCEPTS

The electronics industry is one of the fastest growing sectors of the world economy. Those new electronic components with faster speed, smaller size and lower power consumption will quickly dominate the market. Therefore, the occasion might arise in which electronic components which are the component parts of a product have a shorter life cycle than the actual life cycle of the product.

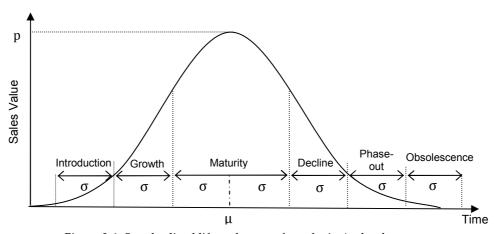

Paper [4] described the product life cycle for the following curve:

Gaussian distributions have been used by the Electronic Industries Association (EIA) as their standardized product life cycle (PLC) curve [5]. The equation of the life cycle curve is

$$f(x) = pe^{(-(x-\mu)^2/2\sigma^2)}$$

(1.1)

where f(x) gives values for the sales revenue of the device/technology group (or number of units shipped, or the percentage market demand), x is the year, and f(x) is defined by the mean  $\mu$ , which denotes the point in time of the sales-peak of the curve and the standard deviation  $\sigma$ . The factor p is the sales peak, the number of units shipped, or the percentage demand.

Figure 2-1. Standardized life cycle curve for a device/technology group

An electronic component life cycle can be divided into several stages: introduction, growth, maturity, decline, phase-out and obsolescence, as shown in Fig.2-1. A more in-depth explanation can be found in [6].

## A. Introduction Stage

The introduction stage is the first stage of a product life cycle. The production costs are usually high because of the initial incurred design costs and low yield, frequent modifications and low or unpredictable production volumes.

## B. Growth Stage

In the growth stage, the product is accepted by the market. The volume of sales increases gradually which brings about a price reduction.

# C. Maturity Stage

The maturity stage is usually characterized by high-volume sales. Competitors with lower production cost may enter the market and thus, at this stage, the product will have the lowest costs throughout the entire life cycle.

# D. Decline Stage

The decline stage indicates both decreasing demand and profit. During the decline stage, only a few specialized manufacturers remain in the market.

# E. Phase-out Stage

During phase-out stage, a manufacturer may set a date for which the production of the part will cease. Usually, the manufacturer issues a discontinuance notice to customers, provides a last-time buy date, and suggests alternative parts or aftermarket manufacturers.

## F. Discontinuance and Obsolescence

Discontinuance occurs when the manufacturer ceases to produce the components. The components may still be available in the market if the production line or stocks were bought by an aftermarket source. Obsolescence occurs at a technology level, while discontinuance occurs for a part number or manufacturer specific level.

There are some commercial databases containing component lifecycle forecast data, such as CAPS Expert from PartMiner [7]. A data mining based algorithm [8] is also proposed to improve their predictive capabilities.

## 2.2 OBSOLESCENCE PROBLEM FOR EMBEDDED SYSTEM

Obsolescence or end of life (EOL) is the final state of a product's life cycle when a vendor will no longer produce, sell and sustain it (i.e. no longer provided by the vendor). The growing use of COTS components and equipment increases the risk of obsolescence. The reasons for obsolescence could be technological, market, planned or environmental etc.

If a product is not popular in the market and becomes unprofitable, the manufacturer then has to commit the facilities and equipment to producing another product that results in greater profits. According to Moore's law, the number of transistors on a chip doubles every 18 to 24 months: poor planning with regards to parts obsolescence causes companies to spend progressively more in order to deal with the effects of aging systems [8]. Intel is relatively famous for its rapidly developing technology and the result of this is the rather rapid obsolescence of their products. It demonstrates a unique capability for engineering major product improvements and releasing these products into the market every 18 to 24 months. The new product will rapidly dominate the market, based on its increased performance, while still maintaining a similar price to that of its predecessor. It is possible to divide obsolescence into several types for embedded systems:

- Peripheral interface obsolete: The peripheral interface standard is developing. A new standard will rapidly enter the mainstream based on its improved specifications. For instance, the USB (Universal Serial Bus) has become the most popular peripheral interface standard for consumer products during the past few years. The earlier IEEE 1284 parallel interface is no longer able to be supported in most devices. Thus, it becomes a possibility that long life cycle systems will suffer from the problem of interface mismatch because of these modern peripherals.

- Communication bus obsolete: In this case, the communication bus is considered as an on-board or on-chip bus, which is the link between each component in the system. For example, it is not possible to support the previous Industry Standard Architecture (ISA) bus which is replaced by the Peripheral Component Interconnect (PCI) bus. For a hardware component, backward compatibility is not always guaranteed unless it incorporates an additional hardware bridge between two buses. A System-on-chip (SOC) design can also suffer from the obsolescence associated with the communication bus. For example, the On-chip Peripheral Bus (OPB) has been replaced by the Processor Local Bus (PLB) [10] for the Xilinx FPGA on-chip bus.

- Component obsolete: A component is a product provided by the vendor, which for the majority, contains some unique properties and cannot be replaced by a product from other vendors. Component obsolescence is a severe case since it frequently occurs. Industry experts have estimated that over 200 000 components from over 100 manufacturers became obsolete in the year 2000 [11].

- *Others:* Obsolescence issues such as obsolete development tools and test systems etc. must all be faced by designers.

In the commercial markets, electronics components in consumer electronics such as PCs or portable applications, for instance, are updated very rapidly, while in automotive, avionics, military application etc., the desired life cycle for these systems is many times longer than the obsolescence cycle for the electronic components used in the systems. For avionics and defense applications, systems face obsolescence even before they enter into service (due to the long design, manufacturing and test cycles).

It is often the case that only a part of the system is actually obsolete or requiring modification. Unfortunately, the replacement or modification is usually as difficult as designing an entire system because the system has been developed as a single entity, with much interdependence between its hardware and software [12].

Obsolete technology impacts on a company in many ways. It impacts their costs in conducting their business and hence their profits, as well as their day-to-day operations. Management must be aware of the impact of technology obsolescence on all aspects of their business, and factor this into their decision processes [13].

## 2.3 OTHERS MAINTENANCE ISSUES

The availability of newer and better architectures (processors, interconnections and interface blocks) can provide the motivation for the reengineering of a product. In the commercial arena, manufacturers must re-engineer their products in order to provide those new features required by their customers, to incorporate newer technologies and standards, or to reduce costs and increase value [14].

Lower prices or better circuit technology could offer the opportunity for designers to replace the legacy components or even an entire system, so that they can reduce costs and increase value. However, it has not proved to be easy to enable either migration or replacement to occur within the different technologies as this will involve costly hardware and software redesigns.

It is a self evident truth that the customer always wants more. Manufacturers must re-engineer their products in order to provide new features required by the customers, to incorporate newer technologies and standards. Exciting new technologies can result in a better form and fit for a specification. Functions will require to be changed as will the bugs contained within the system and these require that the legacy system has to be re-engineered [14]. This is always both costly and time consuming.

#### 2.4 CONCLUSION

This chapter has introduced electronic component life cycle concepts. Various problems in relation to maintaining a long life cycle embedded system are discussed, including obsolescence, function change requirement or technology migration etc. A more detailed analysis and a case study will be presented in subsequent chapters.

# 3 MAINTAINABILITY ANALYSIS OF CAN CONTROLLER SYSTEMS

CAN [15] is an industrial bus standard designed to allow microcontrollers and devices to communicate with each other. In this section, four types of CAN controller systems architecture are described. The maintainability in relation to these experimental systems was to be analyzed.

#### 3.1 CAN BUS

The CAN bus was designed for automotive electronics and was first used in production cars in 1991. CAN is very widely used in vehicle and other industry applications. CAN runs at rate of 1Mb/s over a twisted pair connection of 40m. The bus protocol supports multiple masters on the bus.

The devices that are connected by a CAN network are typically sensors, actuators, and other control devices. These devices are not connected directly to the bus, but through a host processor and a CAN controller. Each CAN node requires a host processor, a CAN controller and a transceiver.

#### 3.2 DESIGN CASES

The project started from a CAN controller system used in industrial construction machinery. In such a case, cost, performance and power consumption are not critical issues. However, this type of long life cycle system requires greater consideration in relation to maintainability.

The microprocessor (or MCU) and the CAN controller are two key components for this system. A peripheral of RS-232 is used for sensor reading.

Two major design platform methods are mentioned, namely the COTS IC platform and the FPGA platform. The FPGA system mentioned in this chapter is an IP based design system. A wide range of choices exists for the COTS microcontrollers and CAN controllers IC from different vendors within the marketplace.

However, for the FPGA platform, the soft microprocessors are divided into two categories:

- Vendor dependent soft microprocessors: Such types of soft microprocessors are usually provided by the FPGA vendors, so it is not possible to implement them on any other vendor's devices. E.g. Xilinx MicroBlaze and Altera Nios II.

- Vendor independent soft microprocessors: Unlike the vendor dependent soft microprocessors, these have no restrictions and can be implemented on any vendors' devices. E.g. ARM Cortex-M1 and OpenRISC from OpenCores.

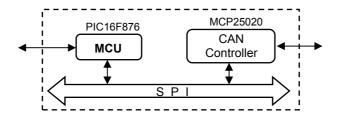

## 3.2.1 Case 1: COTS IC based CAN controller system

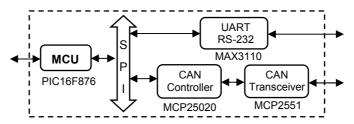

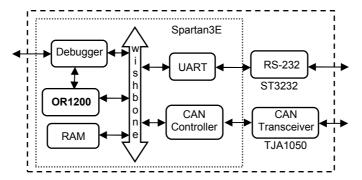

For the traditional COTS IC CAN controller system, an MCU was implemented onto the board. The UART controller and the physical interface circuit RS-232 were integrated as one chip for the peripheral interface. A CAN controller and its physical interface circuit CAN transceiver were implemented on board for the CAN bus protocol. The system board architecture with its relevant components can be seen in Fig. 3-1.

Figure 3-1. Block diagram of COTS based CAN controller system

# 3.2.2 Case 2: vendor specific FPGA system

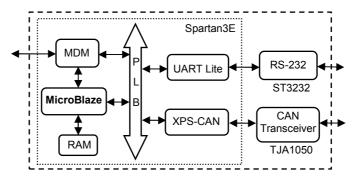

A vendor specific design case based on the Xilinx Spartan3E FPGA is shown in Fig. 3-2. The MicroBlaze [16] is a soft processor core designed for Xilinx FPGAs, which can be implemented and configured by Xilinx EDK (Embedded Development Kit), as shown in Fig. 3-3. In the system, a MicroBlaze soft processor controls the UART lite and XPS-CAN via the PLB. The Xilinx 128-bit PLB v4.6 provides the bus infrastructure for connecting an optional number of PLB masters and slaves into an overall PLB system. It consists of a bus control unit, a watchdog timer, separate address, write, and read data path units, as well as an optional DCR (Device Control Register) slave interface to provide access to its

Figure 3-2. System architecture of Xilinx specific FPGA system

Figure 3-3. Architecture of Microblaze soft microprocessor

bus error status registers [17].

The MicroBlaze Debug Module (MDM) is used for system debugging. The development tools, FPGA devices and IPs are all provided by Xilinx. It is a relatively simple task to perform system development since the majority of the IPs are verified and can be plug-and-play. The whole design and verification process can be executed with a Xilinx tool set. The RS-232 (ST3232) and CAN transceiver (TJA1050) physical interface circuits are also integrated on board.

# 3.2.3 Case 3: vendor and device independent FPGA system

A vendor and device independent system is a "soft" system which can be implemented on any FPGA device. The IP could be open-source licensed or provided by third party IP providers.

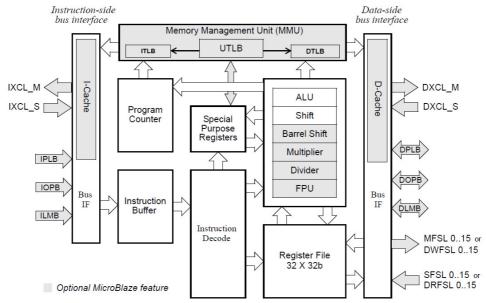

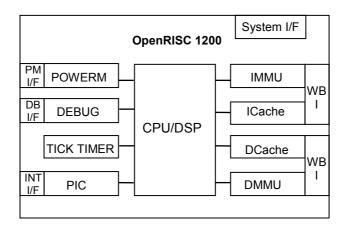

Such a case is based on OpenCores soft IPs. The OpenRISC 1200 (OR1200) is a 32-bit scalar RISC with Harvard micro-architecture, 5 stage integer pipeline, virtual memory support (MMU) and basic DSP capabilities. OR1200 is licensed under a GNU Lesser General Public License (LGPL). The processor has already been verified as running on many vendors' devices and can be downloaded free and can be modified by any individual. Its architecture is shown in Fig. 3-4. The soft microprocessor is described using the Verilog HDL (Hardware Description Language). As an open source core, the design is fully public and can be downloaded and modified by any individual.

Figure 3-4. Architecture of OpenRISC 1200

The CAN controller system based on the OpenRISC 1200 is shown in Fig. 3-5. The board structure is the same as in case 2, while the FPGA on-chip architecture is different.

Every IP in the system is open source licensed in addition to being vendor and device independent. They communicate with each other via a wishbone bus, which is an open source hardware computer bus intended to allow communication between the parts of an integrated circuit communicate with each other. The aim is to allow the connection of differing cores to each other inside a chip. The Wishbone Bus is used by many designs in the OpenCores project. There are two types of Wishbone interconnects, namely the shared bus and crossbar switch. A shared bus interconnect only allows one master to communicate with one slave at the same time, while a crossbar switch may allow N masters to connect to N slaves at the same time, according to the number of implemented buses. In this particular implementation, shared bus architecture is used, which has similar features to those of a PLB bus. A debugger is used for debugging and software downloading. Different JTAG (Joint Test Action Group) cables can be used on different vendor devices and the entire system can be synthesized by using any synthesis tool. The GNU toolchain [18] which is running on a PC, including a compiler, simulator, debugger etc, is used to support the C software development as well as system debugging.

Figure 3-5. System architecture of OpenCores based FPGA system

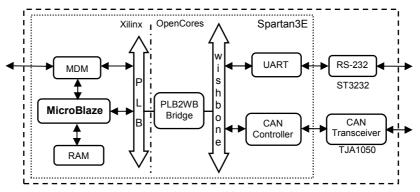

# 3.2.4 Case 4: mixed FPGA system

This solution is comprised of a mixture of vendors specifics and an OpenCores platform. The board structure is the same as in case 2 and is shown in Fig. 3-6. A bridge IP is incorporated between the Xilinx PLB and the OpenCores Wishbone bus. The open-source licensed soft IPs, such as the CAN controller and the UART, can then be integrated into the system as a peripheral core for the Xilinx system. The software application is running on Microblaze microprocessor. All of the design and verification processes can be conducted in a Xilinx development environment.

Figure 3-6. System architecture of Xilinx and OpenCores mixed FPGA system

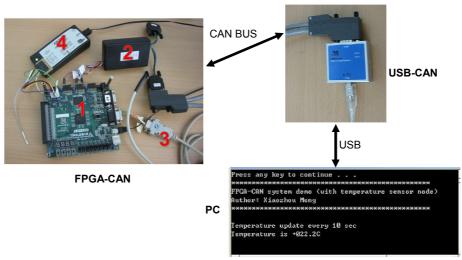

# 3.3 PROTOTYPE OF FPGA BASED CAN CONTROLLER SYSTEM

A simple FPGA-CAN system demonstration is implemented. It works as a CAN node with a temperature sensor. The microprocessor, CAN controller and UART controller IP are implemented on the FPGA. The experimental system setup is described as follow (also marked in Fig. 3-7):

1. Digilent Nexys2 [19] board with Xilinx Spartan-3E FPGA.

- 2. The CAN transceiver (TJA1050) in the black box is the interface circuit between the CAN protocol controller and the physical bus. It connects to FPGA via Pmod ports.

- 3. The temperature sensor transmits temperature values through an RS-232 port on the FPGA board.

- 4. Xilinx platform cable USB is used for downloading and debugging.

- 5. USB-CAN is the interface controller between the CAN bus and the USB. The data then can be transmitted or received by the PC via a USB port.

Figure 3-7. FPGA based CAN controller system prototype

The UART controller (OpenCores) can receive (interrupt based) the temperature data from the temperature sensor via the RS-232. The temperature data is then transmitted to the CAN controller (OpenCores). The CAN controller transmits the data to the CAN bus via a CAN transceiver (TJA1050). The temperature data is received by the USB-CAN and is displayed on the screen by the software running on the PC.

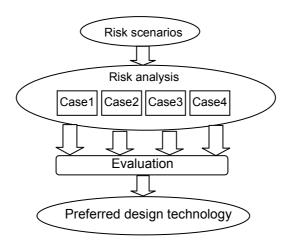

#### 3.4 RISK ANALYSIS

Figure 3-8. Risk analysis for different cases

A risk analysis is taken for all the cases described in section 3.1. A number of potential risk scenarios are identified. No probability is attached to the occurrence of each risk, but the consequences for the maintenance work are classified and evaluated, as shown in Fig. 3-8.

# 3.4.1 Risk scenarios

For the different platform cases presented in section 3.2, the system maintainability is evaluated by analyzing several potential risk scenarios. These scenarios have been developed according to the general problem issues discussed in section 2.2.

- *Microprocessor obsolescence:* Microprocessor is the heart of an embedded system. If it becomes obsolete, then there could be serious consequences.

- *Peripheral interface obsolescence:* A peripheral interface standard can be obsolete. The RS-232 interface in the system has the risk of obsolescence, including a UART controller chip, the physical interface circuit and connector.

- Communication bus obsolescence: The communication bus has a connection with every component in the system. Its obsolescence will soon lead to the obsolescence of all associated components.

- Better circuit technology migration: Better performance, lower price or being friendlier towards the environment would force the system to migrate to a new circuit technology.

- FPGA vendor device migration: Vendor portability is a special issue for the FPGA system. For example, if the FPGA vendor stops providing the devices (obsolescence), in this situation, the system is forced to migrate from one vendor device to another.

• Function change requirement: For different requirements, add, delete or modification of functions are inevitable. For example, some systems might require an Ethernet interface for data transportation.

#### 3.4.2 Consequences

Some of the consequences with regards to the risk scenarios are classified:

- Major board redesign: This work is to redesign the board, including replacing or

adding components, modifying the on-board bus system etc., which is costly

and time consuming and can almost be equivalent to designing a new board.

- Minor board redesign: The redesign of a minor part of the board, including replacing or adding physical interface circuits, redefining the pins for chips, changing the connector etc., which require significantly lower design efforts as compared to those associated with a major board redesign.

- *Driver redesign:* This is the redesigning of the software drivers' work in order to be consistent with hardware changes.

- *Interface modification*: Modify the soft IPs' communication bus interface protocol or add an interface converter.

- *Vendor restriction:* Vendor restriction is specified for an FPGA platform. It means that the FPGA devices can be changed, but this is restricted to the same vendor.

- *Vendor independent:* In contrast with vendor restriction, it does not have any restriction regarding the vendors. Any vendor device could be used.

- *Major system redesign:* It means that there is a whole redesign of the FPGA system, including the on-chip hardware and software driver redesign.

- *Minor system redesign:* Redesign parts of an FPGA system, including parts of the on-chip hardware and software driver redesign.

#### 3.5 RESULT

Table 3-1 presents the results of the risk analysis for the design cases defined in section 3.1. The following is the explanation of table 3-1 for each of the risk scenarios:

- Microprocessor obsolescence: For a COTS product based platform, if the MCU becomes obsolete, the entire system will become obsolete. It results in a major board redesign and driver redesign for a new MCU system. While the FPGA microprocessor is described as a synthesizable soft code, such a special form completely eliminates the risk of microprocessor obsolescence. The legacy IP can still be implemented on a recent FPGA device, which can solve the component obsolete issue described in section 2.2.1.

- *Peripheral interface obsolescence:* The RS-232 serial interface in the system has the risk of obsolescence. If the MCU on the COTS platform does not support the

new peripheral interface standard, it should be replaced or a new interface controller should be integrated together with a physical interface circuit. Both situations will lead to a major board redesign. While for the FPGA platform, the interface controller can be changed by replacing a soft controller IP on-chip. The physical interface circuit (voltage converter etc.) and connector must also be changed which is a significantly easier task. A software driver redesign is necessary in order to adapt the new interface controller to the system. This will ease the peripheral interface obsolete issue of section 2.2.1.

- Communication bus obsolescence: For the COTS platform, the whole system has to

be redesigned since every component which is associated with the bus is

obsolete. The FPGA soft IP does not have any risk of obsolescence, but new IPs

will face interface mismatch problems with an old communication bus.

Interface modification is required if the new IPs are integrated into the system,

which will ease the communication bus obsolescence describe in section 2.2.1.

- Better circuit technology migration: It is difficult for the COTS IC platform to benefit from better circuit technology requiring a major board and driver redesign. However, all the "soft" systems on the FPGA proposed in section V have the capability of accommodating new technology, only requiring minor board redesigns to redefine the pins for the new FPGA chip. However, a technology migration with regards to cases 2 and 4 is restricted to using the same vendor's device. Case 3 is the best choice regarding the maintenance issue described in section 2.2.2 because of its device independency.

- FPGA Vendor device migration: Vendor portability is an issue which is only relevant for FPGA systems. As has been mentioned previously, case 2 is a vendor specific solution and thus it is not possible to migrate it to other vendors' devices. If the vendor ceases to provide the devices, e.g. vendor bankruptcy, the only choice is to redesign a whole new system for another vendor's device. There is a better situation associated with case 4 as parts of the system are vendor independent and with the assistance of a new bus bridge, these parts could be migrated to other vendors' device. The design effort as compared to that for case 2 is significantly lower. For example, the Avalon to wishbone bus bridge IP could be used if the system is migrated to the Altera's device. Case 3 is a totally vendor independent system and thus offers the best portability from the FPGA platform cases and it would be easy to implement the vendor device migration.

- Function change: The function must be changed for any new function requirement or for removing bugs in the current component or system. It is a costly task for a COTS platform, because it results in a major board redesign. Due to FPGA's reconfigurabilty, the function in the form of a soft IP can be added, deleted or modified on-chip. In some situations, a physical circuit is required, such as an Ethernet controller. Some function changes do not even

require a board redesign but only a modification on-chip, if the FPGA is sufficiently large to accommodate the function, such as a video decoder.

Table 3-1. Consequences of different risk scenarios

| Risks                | C                      | Case         |                |                |                       |

|----------------------|------------------------|--------------|----------------|----------------|-----------------------|

| KISKS                | Consequences           | 1a           | 2 <sup>b</sup> | 3 <sup>c</sup> | <b>4</b> <sup>d</sup> |

| Microprocessor       | Major board redesign   | $\sqrt{}$    | -              | -              | -                     |

| obsolescence         | Driver redesign        | $\sqrt{}$    | -              | -              | -                     |

| Peripheral interface | Major board redesign   | √            | -              | -              | -                     |

| obsolescence         | Minor board redesign   | -            | √              | $\checkmark$   |                       |

| obsolescence         | Driver redesign        | $\checkmark$ |                | $\checkmark$   |                       |

| Communication bus    | Major board redesign   | $\checkmark$ | -              | -              | 1                     |

| obsolescence         | Interface modification | -            | √              | $\checkmark$   |                       |

| Better circuit       | Major board redesign   | √            | -              | -              | -                     |

|                      | Minor board redesign   | -            |                | $\checkmark$   |                       |

|                      | Driver redesign        | $\checkmark$ | -              | -              | -                     |

| technology migration | Vendor restriction     | N/A          |                | -              |                       |

|                      | Vendor independent     | N/A          | -              | <b>√</b>       | 1                     |

| FPGA vendor device   | Major system redesign  | N/A          | √              | -              | -                     |

|                      | Minor system redesign  | N/A          | -              | -              | $\checkmark$          |

| migration            | Minor board redesign   | N/A          | √              | $\checkmark$   | √                     |

| Eurotian abanga      | Major board redesign   | √            | -              | -              | -                     |

| Function change      | Minor board redesign   | -            | $\checkmark$   | $\checkmark$   | $\checkmark$          |

| requirement          | Driver redesign        | $\checkmark$ | √              | $\checkmark$   |                       |

a. COTS IC based CAN controller system

d. Mixed FPGA system

Figure 3-9. System maintainability model for different design technologies

# 3.6 MAINTAINABILITY FOR DIFFERENT DESIGN CASES

According to the evaluation in section 3.5, Fig. 3-9 can be used to encapsulate the conclusion for the case study.

b. Vendor specific FPGA system

c. Vendor and device independent FPGA system

# 3.6.1 COTS IC platform

COTS IC solution has no reconfigurability and portability. The MCU and CAN controller are in the fixed hard form provided by the IC providers. The platform defines its specific drivers and software applications. After the completion and release of the system design, it becomes difficult to make any further changes. Therefore, it always requires a major board and driver redesign as shown in table 3-1, the implication of which is that this will involve high maintenance costs. However, the benefits of the COTS IC are its mature technology and market. COTS IC design technology is now the dominant design method for an embedded system. Compared to the FPGA platform, it is more attractive with respect to higher performance, lower power consumption and cost.

### 3.6.2 Software issue for maintainability

Although software development and related tools are not included in the risk analysis, they also represent an unavoidable part in the present day embedded systems' development.

The software application of an embedded system is usually programmed in a high level language (e.g. C), which always contains some processor dependent code. Even if it is a non-processor-specific code, the device drivers and device management, initialization and locator modules and initial boot-up record data require modifications when the hardware changes [20]. The majority of the currently available software written for embedded systems is almost 100% target dependents. Any change to the hardware requires a change in the software [21]. If the microprocessor is replaced by a different one, the software has to be consistently modified. The development environment, such as the compiler and library, can also be different. Such software modification and environment change will result in a system re-verification, which is time consuming. Depending upon the volume of the code, a redesign can cost hundreds of man-years of time, much of which will be devoted to validation and testing [22]. For this issue, the portable code [12] is proposed, which allows compiled software to be executed on any platform without change thus reducing the cost of hardware obsolescence.

Using an embedded operating system can also mitigate the system migration problem. For example, embedded Linux brings vendor independence. Vendors of all embedded Linux distributions have more or less the same business model. The distributions are variations of the same theme. They all have the same and common basic components such as Linux kernel, libraries, basic utilities, and the like [23].

### 3.6.3 FPGA platform

The FPGA system is described using a high level language and is implemented on a single chip. If sufficient space is reserved on the chip, a system function could easily be changed using EDA tools. Sometimes, the function requires only small changes of the physical circuit and connectors as thus a minor board redesign, as is shown in table 3-1. Thus the embedded system built on the FPGA platform is very promising when maintenance issues are taken into consideration.

# 3.6.3.1 Vender specific system

Vendor specific design technology is possibly the most widely used on an FPGA platform. Provision of the IPs for the system is by the FPGA vendors. IPs, such as this, are of reliable quality and it is very easy to integrate them into the system. Designers can obtain adequate support and guarantees. The system might be portable within the same vendor's devices. However, such system design technology is unable to eliminate the risk that a vendor might cease to provide the devices (obsolescence). The reason for using a mixed solution is that it has better portability and is associated with the device independent parts. A designer can make an effort to integrate the OpenCores parts to other vendors systems by using a different bus bridge. Such mixed platforms benefit from vendor specific as well as vendor and device independent IPs, which can provide a compromised alternative for an embedded system design.

# 3.6.3.2 Vendor and device independent system

The FPGA platform implemented with vendor and device independent soft IPs is a preferred solution from the viewpoint of system maintenance, since it can solve all the maintenance problem issues described in section 2.2. The whole system, including the hardware and software, can be accommodated into any vendor device with any technology. The software application and GNU toolchain can be used on a new system device when performing the system migration. This thus eliminates the risk of device obsolescence from providers and it is also possible to benefit from the use of new circuit technology or lower cost hardware. Functions can also be modified for specific customer's requirements. Therefore, such a method could be compared to the traditional manner for a COTS IC based embedded system design technology and the system on an FPGA, in combination with soft IPs has significantly higher maintainability according to the results shown in table 3-1.

It is well known that FPGA's circuit technology and performance are not always growing as fast as a COTS IC component, but this could be tolerated by control, monitoring or communication systems, which are manufactured in low volumes [24]. Many of these systems do not require the newest state of the art

technology and would be in use, preferably, for more than 10 years, such as is the case for the CAN controller system.

The soft IP market is, at present, not sufficiently mature and for this OpenCores based platform, the quality of the open source IP is not satisfactory, since the designer can obtain very limited guarantee from providers. Because there is a lack of intensive verification, our experience is that IPs always contain bugs. However, it is to be expected that in the future, the high reliability vendor and device independent soft IP could be delivered by third party IP providers. Such IPs will become very good resources for designing a long life cycle embedded system.

### 3.7 CONCLUSION

A CAN controller system case study is present in this chapter. Various potential risks and their consequences for a long life cycle embedded system are discussed. It was proposed that an FPGA platform be used to replace the COTS IC platform for the system design. Different CAN controller system platforms have been evaluated using a number of risk scenarios. The results show that an FPGA platform with vendor and device independent soft IP has the highest maintainability.

#### 4 FPGA IP PORTABILITY ANALYSIS

In last section, we proposed the use of an FPGA platform implemented with vendor and device independent soft IPs. This technique can increase the maintainability of an embedded system. In this section, the portability issue for an M-JPEG decoder will be analyzed and discussed.

#### 4.1 INTELLECTUAL PROPERTY

Due to the rapid development of silicon technology, the capacity and performance of FPGAs has improved significantly every year. This allows the designers to build more complex SOCs. In a SOC design, a shorter product life cycle means a shorter time to profit from sales. It is widely recognized that the reuse and sharing of IPs is becoming fundamental to closing the deep sub-micron design gap for successful SOC design [25]. The semiconductor IP industry is over 15 years old but the reuse of IPs still contains many challenges for IP providers, system designers, IP business and IP tool developers [26].

A reusable IP [27] can be a digital IP or an analog/mixed-signal (AMS) IP which is in the form of a processor, memory, decoder, mixed-signal converter, etc. Digital IP is the most popular form for design reuse in present day industry [28]. They are divided into three categories: soft, firm and hard [29]. A soft IP is a hardware specification at the register transfer level (RTL) and this specification involves synthesizable code written in HDL. It is a more suitable form of digital IP, since HDL can be written in a technology-independent manner and synthesized to gate level. Its advantages include flexibility, portability and reusability [30]. A firm IP is in the form of a parameterized netlist and a hard IP is a technology-specific layout. For FPGA system design, the IP usually refers to either a soft or firm IP.

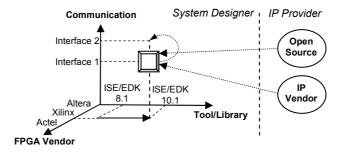

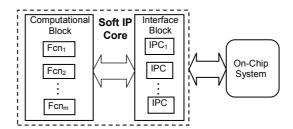

System designers usually obtain IPs, FPGA devices, library and tools from providers. In the majority of cases, they have a very limited knowledge with reference to the structural content of the adopted IP, so it must be considered to be a black box [30]. If an IP for FPGAs is truly portable, it must easily adapt to

Figure 4-1. IP portability issue for system designers

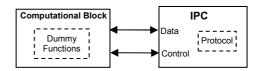

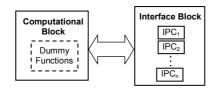

different communication interfaces, being portable between different FPGA vendors and devices and having no dependencies with regards to the tool set used for the system design. This is illustrated in Fig. 4-1. Firm IPs for FPGAs are usually more or less technology dependent netlists which are also dependent on the used tool set.

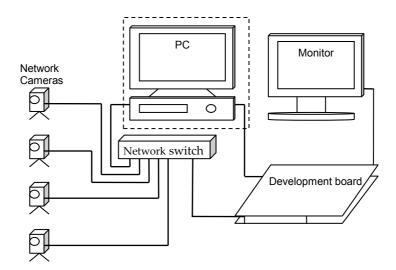

# 4.2 PROJECT BACKGROUND

The aim of this work is to implement a real-time video processing system on an FPGA platform. The video system receives a video stream from several network cameras and manipulates them into a single video stream to be displayed on a single monitor. The system will be integrated into an industrial system of construction machinery. In order to develop the system, a host development computer, an FPGA board, a display monitor and network cameras are required. Fig. 4-2 depicts the real-time video processing experimental system. On the FPGA a video decoder, VGA controller and a soft microprocessor running Linux operating system were implemented. The host computer also acts as the console for the target board in relation to monitoring and recording the results through a UART interface or a telnet protocol.

Figure 4-2. Architecture of the real-time display of multiple video streams

#### 4.3 M-JPEG DECODER

JPEG, or Joint Photographic Experts Group, is a standardized image compression mechanism. The lossy compression method takes advantage of the visual capabilities of the human eye. This kind of file can be split into two areas, namely the headers and the compressed scan data. The headers contain the information about the compressed data (size, format and so on) as well as the

quantization tables and Huffman tables. This standard defines many different techniques used to compress, decompress and store image data. Whereas an M-JPEG is an informal name for multimedia formats, only the result of applying a JPEG to individual frames of a video sequence is called the M-JPEG.

M-JPEG compression format uses standard JPEG still images for video streaming. These images are displayed and updated at a rate which is sufficient to create a video stream. Although this method demands many bandwidths, it provides excellent image quality and can provide access to every individual image contained in the stream.

This project implemented an M-JPEG decoder project [31] that was a free download from OpenCores [32]. The decoder IP will be integrated into an industrial system of construction machinery which has long life cycle expectancy. It is used as a test case for the portability analysis described in section 4.4.

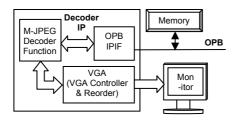

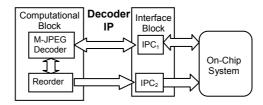

The M-JPEG decoder project was originally developed using ISE/EDK 8.1 on the Xilinx Virtex II pro FPGA. Fig. 4-3 shows the architecture of the decoder system. Three main blocks are involved: *M-JPEG Decoder Function, OPB IPIF* and *VGA Controller&Reorder*. The *Decoder IP* behaves as a master on the OPB enabling the decoder to retrieve compressed JPEG data from *Memory*.

*OPB IPIF* is the OPB interface protocol. The *M-JPEG Decoder Function* decodes the compressed JPEG data and outputs the uncompressed RGB data in a sequence corresponding to a series of Minimum Coded Units (MCU). This uncompressed RGB data is output directly to the *VGA Controller&Reorder* and further as an analog VGA signal to the *Monitor*.

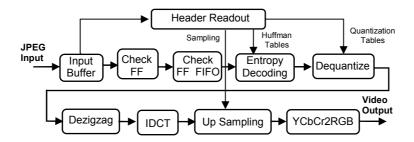

The internal data flow of the *M-JPEG Decoder Function* is further illustrated in Fig. 4-4. Compressed data enters the decoder at the *Input Buffer* and decompressed data is output from *YCbCr2RGB* (YCbCr to RGB color converter). Check FF is a function to check the end of image (EOI) marker.

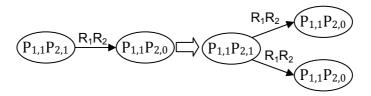

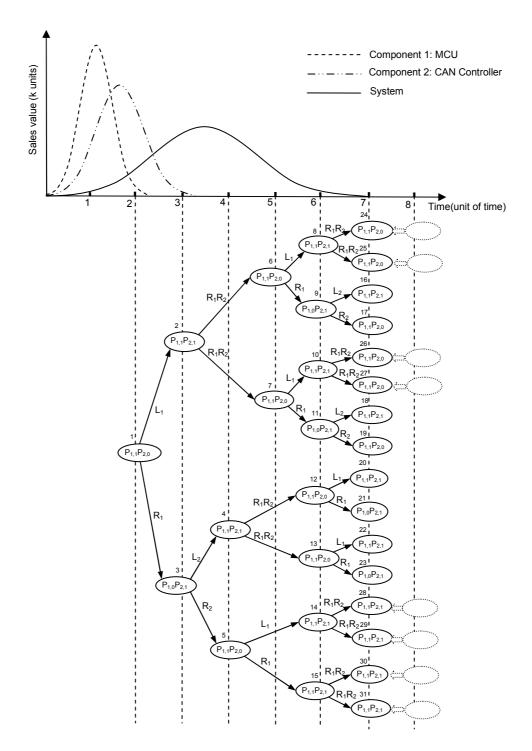

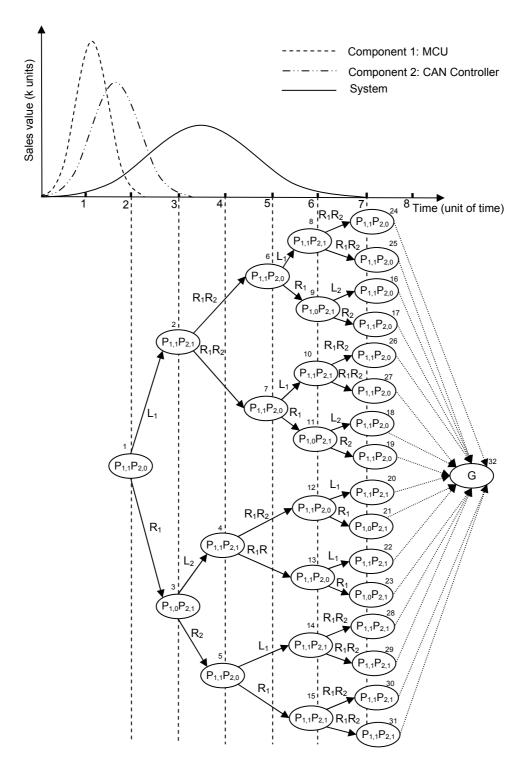

Figure 4-3. Block diagram of the decoder project