# Institutionen för datavetenskap

Department of Computer and Information Science

#### Final thesis

# **GPU-accelleration of image rendering and sorting algorithms with the OpenCL framework**

by

## Anders Söderholm & Justus Sörman

LIU-IDA/LITH-EX-G—15/064—SE

2016-02-03

# Linköpings universitet

#### **Final Thesis**

# GPU-accelleration of image rendering and sorting algorithms with the OpenCL framework

by

## Anders Söderholm & Justus Sörman

LIU-IDA/LITH-EX-G—15/064—SE

2016-02-03

Supervisor: Unmesh Bordoloi Examiner: Unmesh Bordoloi

#### Abstract

Today's computer systems often contains several different processing units aside from the CPU. Among these the GPU is a very common processing unit with an immense compute power that is available in almost all computer systems. How do we make use of this processing power that lies within our machines? One answer is the OpenCL framework that is designed for just this, to open up the possibilities of using all the different types of processing units in a computer system. This thesis will discuss the advantages and disadvantages of using the integrated GPU available in a basic workstation computer for computation of image processing and sorting algorithms. These tasks are computationally intensive and the authors will analyze if an integrated GPU is up to the task of accelerating the processing of these algorithms. The OpenCL framework makes it possible to run one implementation on different processing units, to provide perspective we will benchmark our implementations on both the GPU and the CPU and compare the results. A heterogeneous approach that combines the two above mentioned processing units will also be tested and discussed. The OpenCL framework is analyzed from a development perspective and what advantages and disadvantages it brings to the development process will be presented.

# Contents

| 1        | Intr | oducti        | ion                              | 1  |

|----------|------|---------------|----------------------------------|----|

|          | 1.1  | Motiva        | ation                            | 1  |

|          | 1.2  | Aim           |                                  | 1  |

|          | 1.3  | Resear        | rch questions                    | 1  |

|          | 1.4  | Delimi        | itations                         | 2  |

|          |      | 1.4.1         | Sorting                          | 2  |

|          |      | 1.4.2         | Image processing                 | 2  |

| _        | _    | •             |                                  |    |

| <b>2</b> |      | kgrour        |                                  | 3  |

|          | 2.1  |               | vare limitations                 |    |

|          | 2.2  |               | ng for performance               |    |

|          | 2.3  | _             | utationally intensive algorithms |    |

|          |      | 2.3.1         | Sorting                          |    |

|          |      | 2.3.2         | Image processing                 | 4  |

| 3        | The  | orv           |                                  | 5  |

| J        | 3.1  |               | vare Differences                 |    |

|          | 0.1  | 3.1.1         | CPU                              |    |

|          |      | 3.1.2         | GPU                              |    |

|          |      | 3.1.2         | Integrated VS discrete           |    |

|          | 3.2  | -             | el computing                     |    |

|          | 0.2  | 3.2.1         | Multithreading                   |    |

|          |      | 3.2.2         | Specialized hardware             |    |

|          |      | 3.2.3         | Clusters/Supercomputers          |    |

|          | 3.3  |               | el problems                      |    |

|          | 0.0  | 3.3.1         | Data parallel                    |    |

|          |      | 3.3.2         | Task parallel                    |    |

|          |      | 3.3.3         | Embarrassingly parallel          |    |

|          | 3.4  |               |                                  |    |

|          | 0.1  | 3.4.1         | Model                            |    |

|          |      | 3.4.2         | Platform                         |    |

|          |      | 3.4.3         | Context                          |    |

|          |      | 3.4.4         | Device                           |    |

|          |      | 3.4.5         | Command queue                    |    |

|          |      | 3.4.6         | Memory                           |    |

|          |      | 3.4.7         | Events                           |    |

|          | 3.5  |               | mance optimizations              |    |

|          | 5.5  | 3.5.1         | Memory management                |    |

|          |      | 3.5.1 $3.5.2$ | Workgroups and work-items        |    |

|          |      | 3.5.2 $3.5.3$ | Algorithm design                 |    |

|          |      | 3.5.4         | Conclusion                       |    |

|          |      | J.J.4         | COMCIDION                        | 14 |

| 4 | Me  | ethod 13                                         |

|---|-----|--------------------------------------------------|

|   | 4.1 | Algorithm selection                              |

|   |     | 4.1.1 Sorting algorithm                          |

|   |     | 4.1.2 Image processing algorithm                 |

|   | 4.2 | The hardware                                     |

|   |     | 4.2.1 Intel i7-4790 CPU                          |

|   |     | 4.2.2 Intel HD Graphics 4600 GPU                 |

|   | 4.3 | The software                                     |

|   | 4.4 | Implementation                                   |

|   |     | 4.4.1 Merge sort                                 |

|   |     | 4.4.1.1 Recursive                                |

|   |     | 4.4.1.2 Iterative with swap                      |

|   |     | 4.4.1.3 Parallel implementation                  |

|   |     | 4.4.1.4 Parallel implementation optimization     |

|   |     | 4.4.2 Image processing                           |

|   |     | 4.4.2.1 The basics of image convolution          |

|   |     | 4.4.2.2 Parallel image convolution               |

|   |     |                                                  |

| 5 | Res | m sults                                          |

|   | 5.1 | Merge sort                                       |

|   |     | 5.1.1 Sorting benchmark                          |

|   |     | 5.1.2 Sequential merge sort benchmark            |

|   | 5.2 | Image convolution                                |

|   |     | 5.2.1 The benchmarking                           |

|   |     | 5.2.2 Conventional sequential CPU implementation |

|   |     | 5.2.3 multi-core implementations                 |

|   |     | 5.2.4 General results                            |

|   |     |                                                  |

| 6 | Dis | scussion 32                                      |

|   | 6.1 | Heterogeneous computation                        |

|   | 6.2 | Results                                          |

|   |     | 6.2.1 Merge sort                                 |

|   |     | 6.2.2 Image convolution                          |

|   |     | 6.2.2.1 Optimizations                            |

|   |     | 6.2.2.2 Results                                  |

|   |     | 6.2.3 Caching in local/private memory            |

|   | 6.3 | Method                                           |

|   | 6.4 | The work in a wider context                      |

|   | 6.5 | The OpenCL framework                             |

|   |     | 6.5.1 Operating system timeouts                  |

|   |     |                                                  |

| 7 | Cor | nclusions 40                                     |

|   | 7.1 | Merge sort                                       |

|   | 7.2 | Image convolution                                |

|   | 7.3 | Future work                                      |

|   | 7.4 | Final thoughts                                   |

| 8 | Glo | ossary 43                                        |

| 9 |     | ferences 44                                      |

| Append          | dices                                                               | 46 |

|-----------------|---------------------------------------------------------------------|----|

| A               | Source code of the basic image convolution kernel                   | 46 |

| В               | Source code of the Merge kernel with chunking                       | 48 |

| $^{\mathrm{C}}$ | Source code of the copy kernel                                      | 49 |

| D               | Source code of the Merge kernel with cooperation                    | 49 |

| $\mathbf{E}$    | Source code of the Copy kernel with cooperation                     | 51 |

| $\mathbf{F}$    | Table of run times in milliseconds for different merge sort kernels | 52 |

|                 | 9                                                                   |    |

# List of Figures

| 1  | OpenCL model abstraction                                                                 | 9  |

|----|------------------------------------------------------------------------------------------|----|

| 2  | OpenCL memory hierarchy                                                                  | 10 |

| 3  | A sharpness filter of varying size applied to an image (public domain image used)        | 14 |

| 4  | Recursive merge dividing sequence                                                        | 16 |

| 5  | Iterative merge sort with swap                                                           | 17 |

| 6  | 5x5 box blur filter applied to an image (public domain image used)                       | 22 |

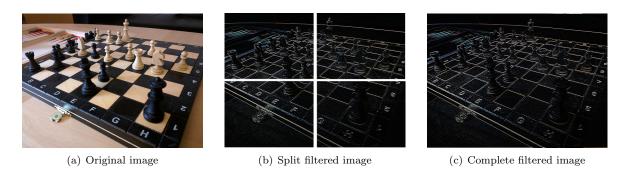

| 7  | Convolution performed on a very large resolution image (original photo by Justus Sörman) | 24 |

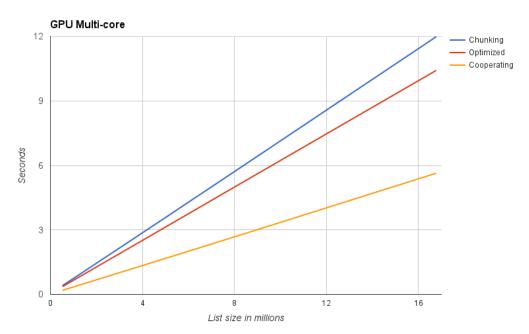

| 8  | GPU multi-core execution times with different list sizes                                 | 26 |

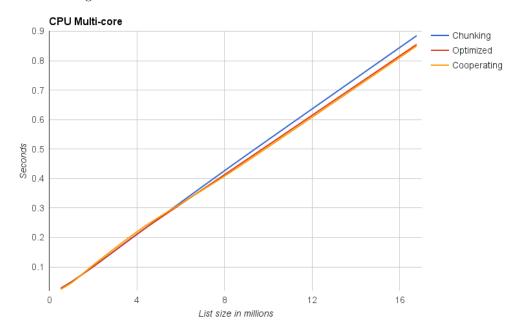

| 9  | CPU multi-core execution times with different list sizes                                 | 26 |

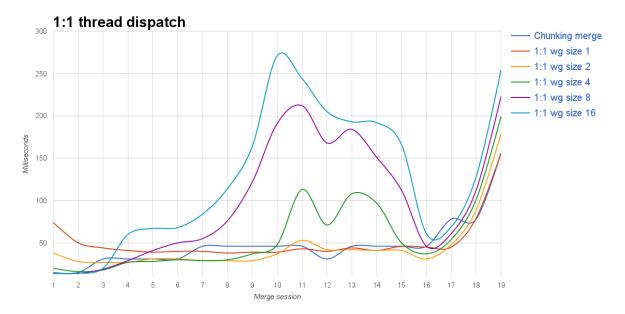

| 10 | Performance test with 1 to 1 thread execution with different workgroup sizes             | 27 |

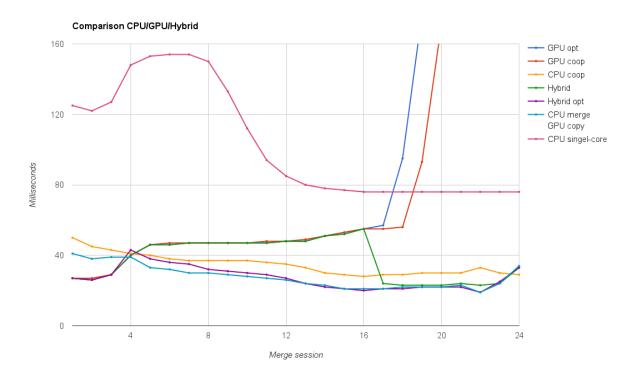

| 11 | Comparison of CPU,GPU and Hybrid execution times in the different merge sessions         | 28 |

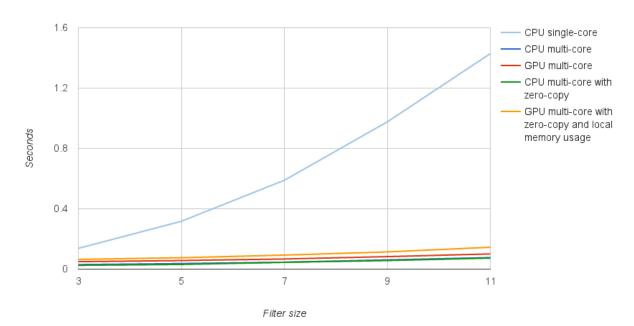

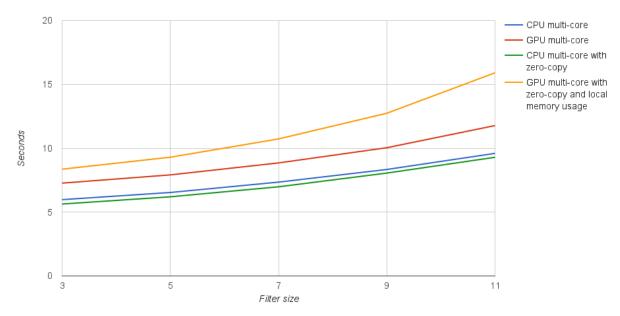

| 12 | Average execution times of varying filter sizes on a 480p resolution image               | 31 |

| 13 | Average execution times of varying filter sizes on a 8K resolution image                 | 31 |

|    |                                                                                          |    |

# Listings

| 1 | Basic parallel merge sort pseudocode                       | 18 |

|---|------------------------------------------------------------|----|

| 2 | Chunking parallel merge sort with external copy pseudocode | 19 |

| 3 | Parallel copy to the swap buffer pseudocode                | 20 |

| 4 | Basic image convolution pseudocode                         | 21 |

|   | High resolution image splitting pseudocode                 |    |

# List of Tables

| 1 | Sequential CPU execution times with varying filter sizes applied to images of resolution |    |

|---|------------------------------------------------------------------------------------------|----|

|   | ranging from 480p to 4K                                                                  | 29 |

| 2 | Execution times in seconds on multi-core CPU without zero-copy                           | 30 |

| 3 | Execution times in seconds on multi-core CPU with zero-copy                              | 30 |

| 4 | Sequential CPU execution times in seconds with varying filter sizes applied to 8K images | 30 |

#### 1 Introduction

This thesis report is the culmination of a bachelor thesis work on GPU-acceleration with the OpenCL framework, at Linköping University. In this thesis the authors will examine the potential benefits of applying GPU-acceleration to common types of algorithms with a focus on performance when using a lower end GPU, the Intel HD Graphics 4600. This is in effort to determine and analyze how significant, if at all the gains in terms of performance are in a commodity desktop computer. The discussion section of this report will also contain an analysis of common hurdles and best practices that should be considered before one chooses to apply GPU-acceleration to a development project.

#### 1.1 Motivation

As software development advances and programs require more and more computational capabilities the hardware side of things and more specifically the CPU has been struggling to keep up. In terms of clock frequency hardware designers has gotten closer to the threshold of what is realistically feasible on a single processor core, prompting the rise of multi-core processors [1]. All the while in commercial settings a significant source of processing power goes unused, the GPU. If more software developers made efficient use of the GPUs available in modern computers it would likely be possible to greatly increase computational performance when running everyday programs. Increased performance which in turn will lead to more advanced software as well as a better user experience.

#### 1.2 Aim

The purpose of this thesis is to provide a proof of concept, that is showing that there is a significant increase in computational performance to be had by applying GPU-acceleration to commonly used algorithms which are computationally demanding. The intention is to find and select appropriate algorithms that normally has a singlethreaded sequential implementation and develop our own versions, GPU-accelerated multithreaded versions. This report will provide a detailed analysis of the results as the different versions are compared to each other both in terms of performance and difficulty of implementation.

#### 1.3 Research questions

• Can GPU-acceleration be used to increase computational performance of merge sort algorithms when using an integrated GPU available in a commodity desktop computer?

It has already been well established that for specific types of algorithms which lends themselves to be parallelized to a considerable degree GPU-acceleration will provide performance improvements. A topic which has not yet received much attention from researchers is the effect in terms of performance when applying GPU-acceleration to algorithms that while parallelizeable might not be so to an optimal degree. The same holds true for the question of to which extent a common office workstation with an integrated GPU benefits from GPU-acceleration.

• Can GPU-acceleration be used to increase computational performance for image processing algorithms when using the integrated GPU available in a commodity desktop computer?

Image processing algorithms tend to be very suitable for parallel execution and can often benefit from being run on a highly parallel processing unit like a GPU. It is already known that using a high-end GPU to perform tedious filter processing or similar algorithms is beneficial but is an integrated GPU up to the task.

• When does the potential benefits of utilizing the GPU for general purpose computation warrant the increased complexity introduced to the development process?

While many algorithms has at least some minor potential for increased performance when implemented with GPU-acceleration some can not be parallelized or doing so would come with such a great amount of overhead that any gain in performance would immediately be lost. When determining the added value of GPU-acceleration one also needs to account for the added complexity that multi-core programming in general and GPU-acceleration in particular introduces to the software development process.

#### 1.4 Delimitations

This report and the analyses herein will be limited to specific algorithms selected for the purpose of this research. While the algorithms in question will be selected based on qualifications believed to allow for extrapolation, variance in terms of how efficiently a given algorithm can be parallelized will still exist. The authors of this report will make use of GPU-acceleration via the OpenCL framework to implement two distinct type of computationally intensive algorithms, sorting and image processing algorithm(s).

#### 1.4.1 Sorting

The results and conclusions of the sorting algorithm found in both the discussion and the results section will be focused on how our GPU-accelerated sorting compares to our sequential implementation. The authors does not intend to compare the implementation to any existing GPU-accelerated implementations.

#### 1.4.2 Image processing

Much like the sorting delimitations, in the image processing part of the result section the focus will be on comparing a GPU-accelerated image convolution algorithm to our sequential implementation. The type of image processing that will be performed will be limited to image convolution with filters.

#### 2 Background

This report is written as part of a bachelor thesis work at Linköping University at the Department of Computer and Information Science(IDA). The work was conducted at Mindroad AB in Linköping, Mjärdevi.

#### 2.1 Hardware limitations

As has already been mentioned in the introductory section of this report, hardware designers are rapidly approaching the limits of the processing power that can be harnessed from a single core [1]. In fact, when talking about what is actually feasible in a home or office computer in terms of heat dissipation and component size the aforementioned limit has already been reached. Up through the late 1990s processor chip performance increased by roughly 60 percent annually, about 40 percent in the early 2000s and down to about 20 percent by the year 2004 [1]. This steadily rapid decline in processing power gained for the amount of time and resources spent developing new chips led CPU manufacturers down the path of multi-core processors.

With multi-core CPUs comes the potential for increased performance, however not all programs and their underlying implementation algorithms lend themselves well to being parallelized [2]. One of the more prominent challenges facing software developers in the years to come will be to efficiently implement their programs, taking advantage of all resources available to them. However an important aspect of software development is being able to recognize when not to make excessive use of multithreading and GPU-acceleration, as doing so could result in performance decrease instead of performance gain [2].

#### 2.2 Craving for performance

With the great advances in single core computational performance that was had all the way up through the 1990s consumers came to expect a certain amount of performance gain when purchasing new hardware [2]. This consumer expectation coupled with previous years performance gains led to a very competitive market where increased performance by any means necessary became the standard [1].

#### 2.3 Computationally intensive algorithms

The barrier for how fast a human can calculate advanced mathematical problems was reached a long time ago, computational hardware was needed to progress beyond this limitation. An historic example of using computer algorithms to solve problems that required so much computation that they could not be solved manually is the code breaking that occurred during the second world war [3]. This involved cracking ciphers produced by the infamous enigma machine, a task that would not have been possible without using early computers to sift through the millions of possible combinations. Since then computers have evolved and their computational power increased enormously but even more calculation heavy problems emerged as endless possibilities were discovered when employing this new type of hardware.

#### **2.3.1** Sorting

A recurring problem in computer science is taking a list of unordered elements and generating a sorted list containing those same elements [6]. While this could appear to be an relatively simple task when the list contains a limited number of elements, creating an algorithm that remains efficient even as the list grows in size is quite challenging. There are many types of sorting algorithms available, all different from each other but there are some common principles that are followed.

One of the simpler sorting algorithms is bubble sort [7] which iterates from the beginning of the list and pushes the larger elements back in the list by swapping the elements. If we find that the

element we are comparing with is larger than the one we are currently pushing back we stop pushing the element forward and start pushing the larger element instead. This type of sorting algorithm is called an "exchanging algorithm" because it exchanges an element in the list every iteration if needed. Another type of sorting algorithm which is very similar is the insertion type of sorting algorithm. Instead of continuously swapping elements it will iterate over the list and find the most suitable place for an element and insert it at that place. The selection type of sorting is also quite similar. It iterates over the list, finds the smallest element and puts it at the beginning of the list. This process is repeated with the second smallest element and so on until the list is sorted.

The Divide and conquer [7] method on the other hand differs from the previously mentioned methods in that it does not iterate over the list. It will instead repeatedly split the list up into several smaller lists until the sorting problem becomes trivial, then it will gather the sorted pieces to form bigger and bigger sorted pieces until we have a complete sorted list. The last common type of sorting algorithms are the so called distribution sorting algorithms, they are usually not meant to sort a list by themselves but they can be used to speed up another sorting algorithm by dividing the work into smaller problems. The divide and conquer principle is the currently the most popular sorting method because it is a lot faster than the other sorting methods mentioned above [7], although it is much more complex to implement than for example a simple insertion sort algorithm.

#### 2.3.2 Image processing

Image processing is computationally heavy because the datasets that needs to be iterated over are often quite large [4]. When processing an image we often need to know information about each individual pixel as well as the pixels surrounding it. The image manipulation performance problem is a non-trivial one because the amount of pixels that needs to be iterated over can grow to an enormous amount rather quickly. Luckily these kind of problems are usually very parallelizable but they are still computationally heavy even if parallelized [5].

#### 3 Theory

In this chapter the authors attempts to provide an overview of parallel computing, parallelizable algorithms and the OpenCL framework as well as a brief look at the CPU and GPU. All of these are important concepts to understand in order to appreciate the findings and analysis portions of this report later discussed in the section 6.

#### 3.1 Hardware Differences

Some combinations of hardware might perform better than other combinations depending on the type of workloads involved. The reason for this is that the architectural design will differ from vendor to vendor and even between product lines from the same vendor. Some hardware is designed to work efficiently with large datasets, performing the same instructions on the whole set. Others are optimized for smaller datasets, being able to perform more advanced instructions on them very rapidly.

#### 3.1.1 CPU

The CPU is a processing unit using the Single Instruction Multiple Data (SIMD) [8] architecture, this means that the processing unit can perform a single instruction on multiple data inputs. This type of processor is often very fast when it comes to performing sequential instructions, it is not uncommon to have clock frequencies of over three gigahertz(GHz). The drawback of the CPU design is that it is a general purpose processor, i.e. it should be able to perform many different kinds of processing fairly well. The downside of such a general purpose processing unit is that it likely will not perform as well as optimized hardware even if it running at a faster clock frequency [9]. On the other hand however it is very easy to develop for due to its versatile performance.

#### 3.1.2 GPU

The other major type of processing unit is the GPU, which uses the Multiple Instruction Multiple Data (MIMD) [8] architecture instead of the SIMD employed by the CPU. This architecture can perform multiple instructions over multiple data inputs during a single clock cycle. Processors with this type of architectural design are usually called vector-processors because they are optimized to work with vectorized data structures. The clock frequency of this type of processor is generally not as fast as that of a SIMD processor, typically about five hundred to one thousand megahertz(MHz) depending on the manufacturer. The GPU is not as general purpose as the CPU but will often perform very well in its dedicated areas, these consists of handling large datasets and performing parallel tasks. The parallelization level that can be achieved on a GPU is far greater than that of the CPU and herein lies the strength of GPU-acceleration. A caveat of this being that poorly parallelized algorithms will often be slower on the GPU than a sequential implementation of the same algorithm on the CPU.

#### 3.1.3 Integrated VS discrete

GPUs comes in two form factors, integrated and discrete. The integrated GPU is usually placed inside the CPU die to form an APU [10]. It should be noted that while APU is the proper term for this type of hardware where the CPU and GPU exists on the same die, some vendors, most notably Intel will still refer to this type of product simply as a CPU. The smaller integrated GPU is typically not meant to be particularly powerful, instead they are designed for low power consumption and to be small enough to fit on the same die space as the CPU. On the other hand the discrete GPU has the whole die to itself and can therefore be designed to be able to do more advanced and faster calculations compared to an integrated GPU.

The type of memory used also differ between the two [10], the integrated GPU is primarily using the systems own memory resources and will therefore often have a larger albeit not as fast a memory pool as the discrete GPU to work with. The discrete GPU is more often than not supplied with specialized high bandwidth, low latency memory. This memory is expensive and that is the reason for the integrated GPU memory pool not being as big as the system memory. When developing software one needs to be aware of one's target audience and what type of system this group will use to run the program. This is because the optimizations and design of the program differ a lot depending on what hardware the end user has in their machines.

#### 3.2 Parallel computing

The term "Moore's law" was coined in 1965 and describes the advancements in computational performance and how it will double every two years. Up until the late 1990s this performance increase came in the form of putting more transistor onto a single chip [1]. As it turns out however it is not feasible to keep on adding more transistors forever. When hardware manufacturers began to push against the limits of how much performance could be had from a single core multi-core development really caught on. This trend lead to the ubiquitous adoption of parallel computing we see today and the massive increase in compute power available.

There are two main methods for utilizing multi-core processors, the first is having a Message Passing Interface (MPI) [8], which is very scalable, allowing the program to distribute the workload over several different machines. This is because the messages are passed between the connected computers via a network interface that is very easy to scale up and distribute, the computers does not even have to be in the same buildings to be able to cooperate efficiently with each other. The second method is the Shared Memory Architecture (SMA) [8], this method shares some of the data between the threads running in the system. The data is shared via a global memory which all threads can access. This method does not scale as well when using multiple interconnected systems [8].

#### 3.2.1 Multithreading

To get greater performance out of a multi-core processor a programmer can make use of multiple threads to perform different operations. One of the problems inherent to multithreading is two or more threads manipulating the same data at the same time. This is solved by means of concurrency control which is crucial for any application using more than one thread [8, 10]. To implement concurrency control a software developer places locks and semaphores around data that several threads will want to access as this could potentially cause problems if these threads were to access the same data simultaneously.

#### 3.2.2 Specialized hardware

The general purpose CPU is as its name indicates made for general purpose computations, which means that it is not specialized to only do one thing like for example an accelerator card specialized for physics. Therefore it will often not perform as well as a dedicated hardware solution like a Nvidia Tesla card [11] when performing computation for large scale physics simulations. These massive parallel calculations would take a much longer time to execute on the CPU. Some of these dedicated hardware cards can accelerate all manner of scientific applications, from protein folding to advanced physics simulations.

#### 3.2.3 Clusters/Supercomputers

When a single machines compute power is not enough, not even if the system contains multiple powerful cores, a cluster can be made to boost the performance. A cluster is a group of computers [8] connected via a network that allows them to communicate with each other and thereby form a supercomputer

that consists of multiple compute cores and that has a tremendous amount of primary memory. Due to the separate nature of the systems a message passing interface is required to allow parallel programs to utilize all the available compute power[8].

As an example a cluster can easily perform massive weather simulations where the map is divided into sections and one computer in the cluster might have one or more sections of the map that it is responsible for. The computers then send their results to its neighbors and depending on what their response is decide how the weather should change in its own section for the next iteration of the process.

#### 3.3 Parallel problems

Solving problems faster without upgrading one's hardware is possible. You can sometimes split a larger problem down into several smaller problems which can then be solved concurrently instead of sequentially. This is what is referred to as a parallel problem, but not all problems are as inherently parallel as others. Some problems can not even be effectively parallelized due to the subtasks involved being strongly dependent on information about each other [10]. There are two main groups of parallel problems, data parallel problems and task parallel problems [10].

#### 3.3.1 Data parallel

These types of algorithms can be executed in parallel due to how the data that is iterated over is structured. The data has to be structured in a way so that each parallel process does not write to another processes data without them being synchronized. Examples of algorithms that are generally data parallel in nature are image processing algorithms and vector math algorithms. One of the hurdles associated with these types of problems are memory constraints [10]. In fact when implementing efficient data parallel algorithms one will often find that so many operations can be done in parallel that the memory bandwidth is the limiting factor.

#### 3.3.2 Task parallel

When an application run more than one algorithm and these algorithms do not rely on shared data, these tasks can be run in parallel to achieve better performance. The problems with these types of algorithms is that they usually need to be synchronized with each other at some point [10]. This is where load balancing comes into play. Load balancing refers to the act of actively distributing the workload over the available resources in an effort to avoid bottlenecking the performance. This means that the order in which the tasks are being run is a limiting factor in regards to performance [2, 10]. Finding the right sequence in which to run the tasks for maximum performance is left to the developer optimizing the implementation.

#### 3.3.3 Embarrassingly parallel

Some algorithms are referred to as being embarrassingly parallel, the embarrassing part in these algorithms comes from the fact that they are well suited to a parallel implementation and does not necessarily relate to the amount of developer time spent implementing the algorithm [2, 10]. Generally what makes an algorithm embarrassingly parallel is a very limited need for communication between processes.

When we have a problem that could be solved with an embarrassingly parallel algorithm the new limiting factor is the supporting hardware [2]. In this case one need to consider how large a portion of the problem that is allocated to each process so that the hardware can work at an optimal level, if the portion is to big the level of parallelization is to low and we can not fully utilize the hardware. On the other hand if the portion is to small there will be overhead caused by the excessive scheduling and launching of threads[10].

#### 3.4 OpenCL

The need for a common standard of how to handle heterogeneous systems were needed as it became increasingly common to have multiple processing elements in a single computer [1, 10]. The development of OpenCL [12] began in June 2008 by the Khronos group and representatives from CPU, GPU and embedded-processor companies [12]. About 14 months later in August of 2009 version 1.0 of the OpenCL framework was released for public usage. The standard is meant to make development of programs that utilizes heterogeneous systems easier. The concept of the OpenCL framework was conceived by Apple who has retained the rights to the OpenCL trademark. Today's systems contain all sorts of different hardware, ranging from GPUs to field programmable gate arrays(FPGAs), hardware that often is not utilized to its fullest. The framework API is based on the C99 standard but wrappers exists for many other popular programming languages like C++, Python and Java [12].

As of today, the 1.2 version has gained widespread support among several major hardware vendors such as AMD, Nvidia and Intel, with most devices released by said vendors being compatible either with it or the previous version 1.1. Driver support for a new version is sometimes released a little slow. Currently OpenCL version 2.1 is released but support for this version is still lacking. Version 2.0 is supported by AMD, which are at the forefront when it comes to having OpenCL compatibility for their hardware. Intel now supports OpenCL version 1.2 on most of their new devices and has some prototype drivers for version 2.0 while Nvidia is only supporting version 1.1 on most devices and version 1.2 on some newly released devices.

#### 3.4.1 Model

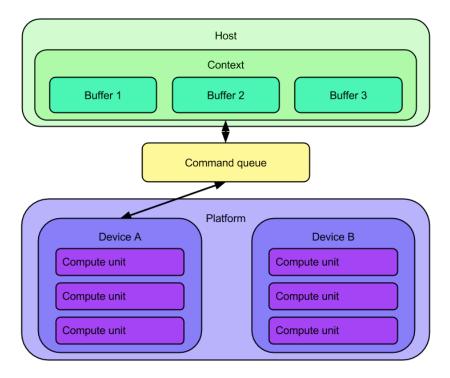

The OpenCL model provides a visualization of the computer system [10, 12]. In this visualization the CPU is referred to as the host, the coordinator of the computer system. The other hardware components in the system are devices, like graphics cards or other forms of dedicated accelerator cards. Each device has one or many compute units which can run a workgroup. Each of these workgroups consists of several work-items and each work-item represents the thread that actually executes on the device. The compute units contain one or many processing elements which the work-items utilizes. The source code for the operations performed by a work-item is called a kernel. This kernel code is compiled at runtime, while this runtime compilation does add some overhead to the application, it gains the ability to dynamically adapt to its environment and the same application can run efficiently on different types of hardware. An abstraction of this model is shown in figure 1.

#### 3.4.2 Platform

OpenCL is a framework for enabling multi-core acceleration of CPUs, GPUs and other types of accelerators. While there is a defined C-style language API available when developing software that makes use of this framework the backend implementations of these API calls are left up to each individual hardware vendor [5, 10, 13]. A platform in the simplest sense is this vendor specific implementation of the OpenCL framework and it is through this layer that the host will communicate with the available devices. Because of this all platforms may not be compatible with all devices, this is especially true for devices manufactured by a vendor other than the platform developer [10]. Once the correct platform for the device one wishes to target has been selected it will be used in the creation of a context.

#### 3.4.3 Context

This structure is the bridge between the host and the device in terms of memory [10, 13]. Here we can manipulate what data is allocated on the device and also get information about the current configuration of the devices in the context. Setting up the kernel arguments and output memory is also done in this

Figure 1: OpenCL model abstraction

structure. The context can be configured in several different ways. If we have several devices in the system we can create a context for all of them at the same time if they are in the same platform otherwise this is impossible to do. The other choice is to have different contexts for each of the different devices. Having either a single or multiple contexts is dependent on the design of the kernels and how they are run. If we need the CPU and GPU to cooperate we create a context containing both these devices[10] if it is possible. To have them in the same context often makes the development process easier because now we do not need to move data between the two if we were to share data.

#### 3.4.4 Device

In OpenCL a device is the physical hardware represented as an abstract data structure [10, 13]. The information in this structure includes but is not limited to, the number of compute units it contains, the prefered workgroup size multiple and the maximum number of work-items per workgroup it supports. A device is primarily used to initialize the command queue and context. The information contained in this structure can used by programmers to optimize the algorithm for specific hardware [10, 13].

#### 3.4.5 Command queue

To utilize the devices accessible in a given context we need a separate command queue for every device in the context [10, 13]. With this structure we can queue up kernels to be executed as well as setting the allocated buffers in the context to contain data of our choosing or send commands to the device to activate different features such as out-of-order execution if the device supports this feature. The benefit of performing out-of-order execution is that it improves load balancing by maximizing the utilization of the GPUs functional units. The drawback of out-of-order execution being that the developer manually

has to ensure that operation dependencies are satisfied before execution [10]. When the execution of a kernel is completed we can then retrieve the data from the buffers to which it was allocated.

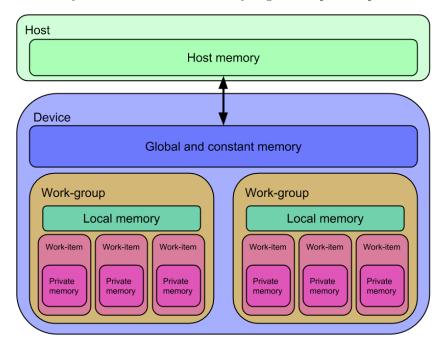

#### **3.4.6** Memory

There are four different types of memory in OpenCL [10, 13, 14]. These four types are global, constant, local and private memory, this memory hierarchy and its connection to the host memory is illustrated in figure 2. All these types are found in different locations on the hardware and are handled in different ways. First is the global memory which is the shared memory buffer that all work-items are able to access. This memory is the slowest in terms of access speed but just because it is the slowest of the four does not mean it should not be used. Big data structures can be saved in this memory as well as data that needs to be shared between all the work-items. Second is the constant memory which is a special type of global memory. The data stored there can as the name indicates only be read from and not written to. In some hardware declaring a data structure as a constant will allow caching of the data and speedups may be gained compared to only using standard global memory.

Local memory, the third type, is much smaller than the global memory and is only shared between work-items in the same workgroup. The benefit of using this memory is speed, it is much faster than the global memory. The problem here is that if the workgroup uses too much of this memory it will be cached in the global memory and will therefore lose most of the speed that we were trying to gain by using it. The fourth and final type of memory is the private memory which is used exclusively by the work-item itself. This memory can not be shared in any way and usually consists of several different registers close to the physical core. Much like local memory, private memory is quite limited in terms of size, a work-item attempting to use more memory than is available will result in a loss of performance due to data being cached to global memory instead. Because of this the kernel should not use an excessive amount of private memory as this could have a severely negative impact on performance [10].

Figure 2: OpenCL memory hierarchy

#### **3.4.7** Events

Events in OpenCL is a feature that allows the developer to ensure proper synchronization for operation execution [10, 13]. When one of several different enqueue commands is issued via a command queue an event is created, after the enqueued operation has been carried out the event will call back to inform that the operation has been completed. The OpenCL enqueue commands all take an optional parameter of event type. Utilizing this parameter when issuing commands via the command queue we can inform the host that the issued command is dependent on another operation and should not be executed before the callback from that operations event has received. This method of synchronization is referred to as event chaining and should primarily be used when the command queue is set to run out-of-order executions.

#### 3.5 Performance optimizations

Implementing an algorithm with OpenCL is often not particularly difficult but making it run fast and efficiently in a manner that utilizes the available hardware resources to its full potential is another matter. There are currently several vendors with many different pieces of computational hardware available on the market. All of which prefers different types of optimizations be it in how they handle memory operations or in what data type is used in calculations.

#### 3.5.1 Memory management

The first problem a developer faces when implement an algorithm in OpenCL is choosing how to handle the memory access patterns of the algorithm. The hardware might prefer reads of a specific size and pattern to perform at peak capacity. In order to utilize the memory efficiently, techniques such as data padding were useless junk data is interspersed together with the real data in order to ensure optimal read access might be used. Such techniques are very hardware dependent but should be considered if the application is only targeted to run on specific hardware. If one manages to find the ideal implementation for the targeted system, a substantial speedup may be gained. Using data types that are vectorized can also boost performance [10]. The memory bus is often capable of transferring large amounts of data as long as it is contiguous. The positioning of the data is also important, if you can use a memory module closer to the core then it is usually better to move data to it and use it from there if the data is to be accessed many times. Otherwise it will just bog the performance down. Another thing that is crucial to remember is that if we have a discrete GPU we do not want to use the systems own memory due to it being slower compared to the accelerator cards dedicated memory. However if the GPU is integrated within the CPU we can perform a so-called zero-copy [13] and thereby not creating an extra instance of the data in memory just for the GPU, minimizing the startup and teardown time of the operation.

#### 3.5.2 Workgroups and work-items

Problem number two is determining an optimal workgroup size. The hardware manufacturer will recommend a preferred workgroup size multiple for all OpenCL compatible products. While this workgroup size is unlikely to be the optimal one for any given algorithm it will often perform decently well regardless of what hardware and kernel program you might be using. There are instances where the default preferred workgroup size multiple will greatly underperform [15], in these cases the design of the algorithm being used is most likely the main cause of this. The hardware usually performs well when using a workgroup size close to the recommended one, one power up or down usually results in a minor increase or decrease in performance. Setting the workgroup size to be at or close to the available minimum or maximum is usually a bad idea as this will often cause the algorithm run slow or not at all depending on the implementation [14].

#### 3.5.3 Algorithm design

The third and final problem is the design of the algorithm itself. When first writing the loops and statements the code might look good on the screen but the compiler could have trouble optimizing the algorithm for the hardware [16]. The performance might be decent but if one more thoroughly inspects the degree to which the ALUs are utilized, one sometimes realize that the processing unit is only using a fraction of the compute power at its disposal. This could mean that the algorithm is memory bound and an alternative implementation, possibly using manual loop unrolling might be preferable [10]. The choice here is to either alter the way memory is handled or rethink how the algorithm works on the data. Changing to a more preferable data type like a vectorized one might be beneficial as doing so makes better use of the wide memory bus that is often available for data transfer between the global and local memory. Thereby having more data for the ALUs to process which will often lead to a higher utilization level of the device [10, 13].

#### 3.5.4 Conclusion

Writing a parallel algorithm using OpenCL is often not exceedingly hard depending on the problem. To write an algorithm that utilizes the hardware's resources in an effective way requires extensive knowledge of the hardware used and many of the features in OpenCL. Although depending on the algorithm the most common way to have the algorithm run fast is just to choose a good workgroup size that will perform well on the targeted hardware.

Some other things to consider when designing an algorithm is that IF statements should be used with care because the GPU is not as good at handling branch misses as the CPU because of the lower clock frequency and therefore the penalty is much bigger [10]. A branch miss is when the processing unit makes a faulty guess on what code is supposed to be executed which happens often with IF statements. There are some other things that one should keep in mind as well and that is to unroll loops if possible, store small variables in local or private memory if possible because it is much faster than the global memory.

#### 4 Method

In this section the authors will describe in detail the approach taken both in the algorithm selection process as well as in the implementation of said algorithms. A rundown of the hardware utilized for the implementation and benchmarking as they pertain to this thesis work will also be provided.

#### 4.1 Algorithm selection

In order to provide a varied and representative analyses of GPU-acceleration on traditionally sequentially executed algorithms two distinctly different types of algorithms have been selected. The first type is a sorting algorithm, this type of algorithm was chosen as the sorting of data is a common problem in software development and computer science in general as many algorithms will make use of and depend on an efficient sorting component. At the behest of the company for which these analyses are carried out at least one of the selected algorithms should relate to either signal or image processing. Therefore the second type of algorithm chosen relates to image processing. The reason for this being that this type of algorithm is expected to provide significant performance improvements if implemented in parallel [4] even on an integrated GPU.

#### 4.1.1 Sorting algorithm

Finding a sorting algorithm that could not only be parallelized but also stands to benefit from a parallel implementation was the first task of the selection process. Finding sorting algorithms that could be parallelized proved not to be particularly difficult. Almost all divide and conquer type algorithms can be parallelized in some manner but finding an efficient way to maximize the number of concurrent threads working on the same list is more challenging.

The first algorithms that were considered were bucket sort and merge sort [6, 7]. Bucket sort was considered a good fit for parallelization due to its distributed nature. The algorithm employs a distribution type of sorting which as the name implies distributes the list into smaller lists that can then later be sorted more efficiently. Bucket sort is usually implemented together with another sorting algorithm that sorts the buckets (the smaller lists), because it is less efficient when implemented by itself as it consumes too much memory due to recursion. Merge sort is a divide and conquer type of sorting algorithm. The essence of how it functions is dividing the list into equally sized smaller pieces until the sorting becomes trivial e.g. the pieces are split to the point where they only contain a single element. Then the algorithm starts to merge the elements in a tree like structure starting with the two first elements in the list. These two elements now form a small list of sorted elements. It will do the same to the next two elements in the list and merge them together to form a list of four elements, and so on until the list is completely sorted.

The problem with parallelizing the bucket sorting algorithm is the insertion into buckets. These buckets can only be accessed by one thread at a time, there may be many buckets and there needs to be synchronization when inserting into them. This will hinder the performance of the algorithm substantially. Merge sort on the other hand is a better fit for parallelization. As already mentioned the algorithm is a divide and conquer type algorithm which works by splitting the problem into smaller chunks that are easier to solve. Each of these small chunks can be run concurrently and thereby we can achieve a high level of parallelism.

During the literature study as we came to understand the pros and cons of the algorithms we concluded that bucket sort was not an ideal algorithm to parallelize. We turned our attention instead to merge sort that while more challenging to implement showed more potential for parallelism. There are already existing parallel merge sort algorithms, a prominent example of which is bitonic merge sort [17]. Bitonic merge sort is a parallel sorting algorithm that uses a fixed comparison network to sort the list,

otherwise the sorting algorithm is very similar to the standard merge sort algorithm. In the end the standard merge sorting algorithm was selected to be implemented because of the time spent on the prior study of the algorithm and thought that had gone into it when trying to figure out how to utilize the memory properly when parallelizing the algorithm.

#### 4.1.2 Image processing algorithm

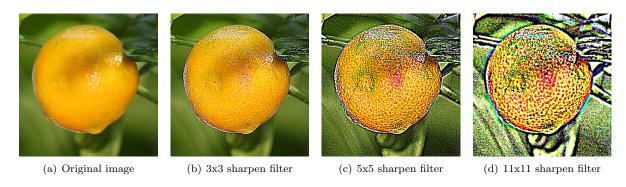

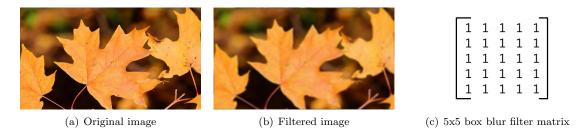

The type of image processing algorithm select is with image convolution with filters [10, 18], a form of image processing that lends itself very well to being parallelized. The reason this type of algorithm is so well suited for a parallel implementation is that operations are performed on each individual pixel of the image and only limited information about the surrounding pixel values are needed. How limited is decided by the size of the filter matrix employed, for certain types of filters a simple 3x3 matrix will suffice, for others either a fixed larger masking matrix or one of varying size may be preferable. Oftentimes using a larger size filter can enhance the desired effect. This is illustrated in figure 3 where a sharpness filter of varying size is applied to an image.

Figure 3: A sharpness filter of varying size applied to an image (public domain image used)

The size of the filter used in combination with the resolution of the image it is applied to will determine the execution time of the algorithm. With the image resolution determining the amount of pixels and the filter size how many operations per pixel need to be performed.

The effect of the filters will also depend on the resolution of the image to which it is applied, a 3x3 box blur filter matrix will provide a slight uniform blurring of a 480p resolution image that is even more subtle than the effect shown in figure 6. Using the same filter on a 4K resolution image will make for a much more minute effect meaning that with some types of filters the filter size needs to increase in step with the image resolution. For other types of filters such as edge detection the application of a small filter on a large resolution image will still yield the expected result.

#### 4.2 The hardware

In order to provide the reader with the requisite information needed to either replicate the findings presented in section 5 or to facilitate drawing their own conclusions, the authors will give a brief rundown of the systems used for this thesis work.

#### 4.2.1 Intel i7-4790 CPU

The Intel i7-4790 CPU [19] is one of the fourth generation i7 processors from Intel. This model is a desktop variant with a locked clock frequency of 3.6 GHz but can boost up to 4.0 GHz when needed,

although not all cores at once due to thermal limitations. The stepping schema of the processor is 2/3/4/4 which represents how many extra multiples the cores can boost compared to the Front-Side Bus(FSB). The first number represents how many extra multiples all cores can have, the second is how many half of the cores can have i.e. 4 cores on this particular processor, the rest of the schema follows the same pattern. The processor is equipped with 4 physical cores and Intel's Hyper-Threading Technology so the core count the user actually sees are 8. The memory configuration on the chip is an 8 megabytes of level 3 cache that is shared across all cores. The level 2 and level 1 cache is separate to each physical core with a size of 256 kilobytes and 32 kilobytes respectively. The level 2 cache is the cache that OpenCL sees as the local memory of each compute core and the first and third level is only handled by the hardware itself.

The OpenCL implementation for this processor sees 8 compute cores that has a maximum number of 8192 work-items in a workgroup per compute core [20]. The recommended workgroup size multiple is 128, which is quite high compared to that of discrete graphic cards.

#### 4.2.2 Intel HD Graphics 4600 GPU

The Intel HD Graphics 4600 GPU [19, 21] is an integrated graphics processor designed to be a low power unit that runs at a clock frequency of 350 MHz. The processor will dynamically boost its clock frequency when needed, up to 1.2 GHz. Thereby making the chip perform better when needed while at the same time keeping power consumption to a minimum during low utilization. The are a total of 20 compute units in the GPU and each compute unit contains two Floating-Point Units(FPUs) which can perform one addition and one multiplication concurrently. The FPU handles both integers and floating-point values equally efficient. The SIMD width is the number of concurrent instructions that can be performed on GPUs. The Intel HD Graphics 4600 has a SIMD width of 4 but Intel has implemented an advanced SMT architecture that allows for dynamic scaling up to a width of 32. The memory on the GPU is divided into three levels of cache that is accessed via a 128 bit wide bus which makes transfers of 64 byte data reads and writes in a single clock cycle possible. The first and second levels of cache the programmer has no control over as they just cache data that is often accessed. The third level of cache is a 256 kilobyte cache that stores data for each separate slice. A slice is a subdivision of the GPU's total compute units which is a group containing 10 compute units. The Intel HD Graphics 4600 as a whole contains two slices and other models can have up to 4 slices. These two slices share a common cache of 64 kilobytes per slice making for 128 kilobytes of common storage for the Intel HD Graphics 4600 model. The hardware supports up to 7 threads per compute unit which means that for each slice there is support for up to 70 hardware threads to be run concurrently. So on the whole chip 140 threads can execute concurrently. Each hardware thread can run up to 32 different software threads e.g. work-items in OpenCL this enables us to run a total number of 4480 work-items concurrently.

Taking all these specifications into consideration when implementing the algorithm is vital as they impose a number of limitations on our implementation. The first limitation is the memory size, a good data fit is crucial so that the cache can work as optimally as possible without needing to bounce data to a higher level of memory. Because of this each workgroup should not use more than 256 kilobytes of local memory. The transport of data back and forth from global to local memory can also be made more efficiently by moving data 64 bytes at a time. Workgroup size needs to be carefully selected, a workgroup size of 32 would likely be preferable due to the hardware limitations and the multithreading capabilities of each compute unit. Although depending on the design of the algorithm this number could be adjusted to better fit the implementation. The last limitation to consider is to ensure that there are enough work-items executing concurrently. Using a number of work-items that is a multiple to the number of hardware threads is likely a good choice to ensure an even load across all cores. So the workload needs to big enough and heavily parallelized to be run efficiently.

#### 4.3 The software

The algorithms that were selected for this thesis work and which implementations are described in this report was developed on machines running the Windows 7 operating system with all essential updates released until this point in time installed.

The C/C++ compiler used during the development of the aforementioned applications is the 64-bit MinGW compiler version 4.9.2 with posix threads [22].

Intel's OpenCL Code Builder[23] version 1.4.0.25 64-bit version was used extensively to compile and analyze the performance of the kernel code. The reason behind using a third-party program to compile and test kernel code is that an OpenCL application always builds its kernels during runtime, meaning that a kernel either executes or it does not, with no way for the developer to know why it did not. This proved very useful for catching common mistakes such as syntax errors and to verify that the kernels behaved as expected during execution time.

The implementation of the image convolution algorithm makes use two third-party libraries, CImg [24] and Image Magic [25] in order to facilitate loading of file formats such as jpg and png into memory as well as enabling the writing of the processed images to disk.

#### 4.4 Implementation

In this section the authors will describe in detail how the selected algorithms functions and how they were implemented with the OpenCL framework. When applicable several different versions of the algorithm will be brought forward to have its pros and cons examined together with an explanation of why it was deemed either suitable or unsuitable for a parallel implementation.

#### 4.4.1 Merge sort

The main principle behind merge sort is that we divide the sorting problem into smaller parts until the sorting problem is trivial to solve, i.e. the small sublists are of size one and then the sublist is sorted by definition. When we have many smaller lists we can now merge them in pairs in a tree like structure and put the smallest element of each merging pair first. Doing this for all the pairs will result in an sorted list. The implementation of this can be done in several different ways, below are some examples of how we implement the merge sort algorithm.

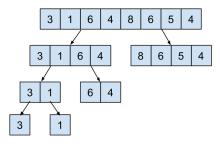

#### 4.4.1.1 Recursive

One of the simplest and probably most naïve way to implement a sequential merge sort is by utilizing recursion. To implement this we need two different functions, the first function divides the list into smaller sublists if the sublists are not of size 1 because then they are considered to already be sorted. We divide the list into left and right tree branches with their own memory pools as demonstrated in figure 4.

When we have divided down to the bottom of the tree and we have sorted sublists of length 1 we need to merge them. Here comes the second function of the implementation, this function merges two sublists together. The merging is pretty straight forward, we allocate a result list that has space for both of the lists and goes through both lists and picks the smallest element in each list and inserts it into the

Figure 4: Recursive merge dividing sequence

result list. Continue this procedure until one of the lists are empty and then insert the rest into the resulting list. Then due to the recursion we will bounce up the whole tree of functions and after the last bounce we have a sorted list.

The implementation of the recursive method is not hard to follow or to implement if you are familiar with how recursion works. The main downside to the algorithm is that it uses a lot of extra memory compared to the amount of memory needed for the original list. The constant allocation of new memory space will take some time and the utilization of the CPU will not be very high because this algorithm is mostly bound by the speed of the installed main memory on the system and how the operating system allocates memory to the process. Also some overhead will occur as a result of the many nested function calls.

#### 4.4.1.2 Iterative with swap

An iterative version that utilizes nested loops instead of recursion is usually beneficial because it avoids the overhead of multiple function calls caused by a recursive algorithm. Also an iterative algorithm is much easier to parallelize than a recursive algorithm.

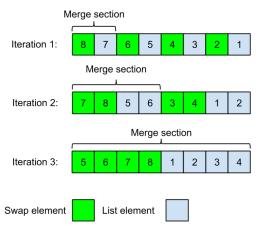

Figure 5: Iterative merge sort with swap

Now we will describe an iterative version of merge sort. In this iterative version we maintain a swap buffer that is used for storing the first half of all the merge sections. A merge section is a part of the list that is going to be merged into one bigger sorted section as shown in figure 5. It consists of two smaller individually sorted equally sized lists.

**Step 1:** The algorithm copies the elements in the first half of the merge section and puts the them into the swap buffer at the same index they had in the original list. Then the same procedure is done for all the others merge sections in the list.

Step 2: After the copying is finished we begin with the first merge section and merge the element from the swap buffer with the second half the merge section. This process is repeated until there are no merge sections left to merge.

Step 3: Then this process is repeated but the length of the merge sections are now doubled. This loop is run until the procedure has been performed with a merge section that has the same length as the complete list at which point the whole list is sorted.

By using this swap buffer instead of repeatedly allocating new memory for the merge sections the performance will increase and the memory usage decrease significantly. Although implementing the swap buffer rather than just allocating new memory is a little challenging, having the memory set up in this way will facilitate the implementation of the parallel algorithm.

#### 4.4.1.3 Parallel implementation

By using the iterative version with swap as a base for the parallel version we can distribute all the merge section operations over the dispatched work-items. Thereby having a parallel algorithm where all merge sections are merged in parallel instead of sequentially. The merge section that a work-item is supposed to work with is calculated by having its thread id multiplied by two. A check is performed and if the offset corresponds to the index of the first element in a merge section we will perform a merge otherwise the thread will terminate its execution and do nothing this merge session. This is to ensure that only one thread merges the section.

The swap buffer is implement in the same manner as in the iterative version but we now can directly get the offset that we are supposed to work by using the one we just calculated. When the first half of

the merge section is copied to the swap buffer we can start to merge the sections together. This is also fairly simple just like the swapping due to the already designated offset. Then after we have merged, all work-items needs to be synchronized to be able to begin the next run of swapping and merging with a greater length of the merge section. How the kernel is implemented is shown in listing 1.

```

basic merging kernel()

{

if(my position is first in the merge section)

{

copy first half of the merge section to swap buffer

while(sublists are not empty)

{

merge the sublists and insert into the list

}

while(swap buffer is not empty)

{

put rest into the list

}

}

}

```

Listing 1: Basic parallel merge sort pseudocode

This was the first implementation of our parallel merge sort. The problem that we encountered was that the kernel execution time can not exceed two seconds otherwise the Timeout Detection and Recovery (TDR)[26] daemon process will reset the drivers for the GPU and our kernel will halt its execution. Because of this we need to divide the later merge sessions into smaller chunks. The maximum number of merges that were allowed to be performed without hindering the performance of the earlier merge sessions but still prevent the halting of the later ones needed to be calculated. This was done by measuring the time each merge session took when performed with the basic implementation. After some measuring we decided to set the maximum number of elements that could be merged in a single chunk to 1/128 of the total list size. The merge chunk then took a little under half a second to be performed. This allows us to perform the merging within the time limit imposed by the TDR even on lower end hardware.

This solved the calculation part of the problem, during the first iteration of every chunk session we copied all the needed data to the swap and this took a considerable amount of time and we constantly hit the execution time limit even when having a relatively small merge size. The final version of the implementation takes the copy problem into account by using a separate kernel that only is used for copying the needed elements to the swap buffer. This can be done in parallel by having knowledge of the thread id and the current length of the merge sections. By doing this we minimize the time spent copying, also the kernel execution time goes down as it does not need to handle the copying. This enabled us to use a larger the chunk size, this will increase the performance by not having to save the state of the sorting as many times. The pseudocode of the final version is shown in listing 2.

One benefit with having the implementation in OpenCL is that we are not confined to only use the GPU. It is also possible to use the CPU in parallel, although the parallelism in this implementation is too fine-grained for the CPU to execute efficiently in the first merge sessions, but this implementation will work on both processing units.

```

chunking merge kernel with external copy()

{

if(my position is first in the merge vector)

{

if(we are in a chunk)

{

get where we stopped last time

}

while(swap buffer is not empty)

{

merge the sublists and insert into the list

}

while(we have not inserted the chunk size number of elements from swap)

{

put elements of swap into list

}

save our state in the sorting process

}

}

```

Listing 2: Chunking parallel merge sort with external copy pseudocode

#### 4.4.1.4 Parallel implementation optimization

The choice of workgroup size is one of the first optimizations that should be done when the kernel code is finished, Intel recommends a workgroup size of 32 for the Intel HD Graphics 4600 which should be a good starting point. Although after some testing with the workgroup sizes we found that 32 runs well compared to most other sizes, a workgroup size of 16 runs faster with the implementation of our merge sort kernel on this specific hardware. The copy kernel on the other hand did not run as well with a workgroup size of 16 but performed very well with a workgroup size of 32. The execution time of the copy kernel is very short compared to that of the merge kernel so optimizing this kernel is not a priority as the impact will not be very significant.

The copy kernel is a solution that takes care of the problem with halting kernels caused by the sheer amount of copying that had to be done during the later merges. It is also a minor accidental optimization as it increases the parallelism of the copy sequence. The most basic merge kernel handled the copying to the swap buffer per work-item that were going to execute a merge. The copy sequence quickly became a bottleneck but it was not that hard to parallelize the copy across all work-items. The only catch is that the copying needs to be synchronized across all work-items and the only way to do this is to queue up multiple kernels where all work-items are synchronized between the executing threads as there is no way to synchronize between workgroups. The number of threads dispatched for this kernel is equal to half the size of the original list. The kernel copies two elements from the list to the swap if the thread's id is within the first sublist in a merge section. Thereby the kernel is running highly parallel and when a whole workgroup is within a sublist they combined copy 64 bytes of contiguous data which is what the hardware prefers, this will result in an efficient and fast copy. Pseudocode for this kernel implementation is shown in listing 3.

```

copying kernel()

{

if(my position is in first part of the merge vector)

{

copy 2 elements from the list to the swap buffer

}

}

```

Listing 3: Parallel copy to the swap buffer pseudocode

Most of the execution time spent in the merge sort is in the last few merge sessions when we can not utilize the whole GPU to its full extent, about 7% of the total execution time is spent when the GPU is performing at its peak and the remaining 93% is when it is underutilized. These numbers were calculated from the execution times presented in appendix F. This underutilization is the implementation's main bottleneck and it is a problem that as to be solved if the GPU is to competitively compete with the CPU. One possible solution is the use of cooperative merging in the later merge sessions. This would mean that the GPU would be utilized to a higher degree and this would greatly improve performance. The cooperation can be done in several different ways, some more complex than others. A version of cooperative merging has been described in [27]. In this thesis we implement a slightly modified version of this algorithm, below we will describe our implementation and the modifications made as well as briefly explain the standard cooperative merge sort algorithm.

The algorithm described in [27] works by splitting up the list into equally sized chunks that are then sorted. Then we use binary search to find where the splitting elements can be inserted into the other list and save that position. When we have done this for the complete list we have pairs of small sublists that can be individually sorted, with this algorithm many threads can concurrently operate on one merge section. The problem is that it is hard to understand and too complex to implement for this project. Our modified cooperating merge only uses two threads in one merge section instead of many. By having this simplification we can get a merge kernel that merges the two sublists from both the front and the back concurrently. The two threads will merge until they have processed half of the merge section each.

This optimization raised the degree of parallelism in the kernel which in turn lead to a huge performance increase. The copy kernel also needed to have some modifications done to it in order to be used with the cooperation kernel. The copy kernel is now copying the whole list to the swap buffer because of concurrency issues introduced by the cooperation. This is a problem in the multithreaded merging of the cooperation algorithm as there will be two threads writing to and reading from the list at the same time during the merge. By having the entire list in the swap buffer both threads can safely write to their own half of the merge section while remaining sure that the data read from the swap buffer is not modified by the other thread.

To conclude the optimization of the kernels the choice of workgroup size can largely dependent on the hardware and how the algorithm is designed. The use of local or private memory is in most cases be a good way to minimize the amount of reads and writes to global memory. The biggest improvement that can be achieved in most cases is to raise the degree of parallelism if it is possible.

#### 4.4.2 Image processing

Using image convolution with filters we can manipulate an image using a constant algorithm to achieve a plethora of different outcomes based almost entirely on the filter being applied. Because of this potential diversity almost all modern image manipulation software these days allows the user to apply these types of filters to their images, this allows the users to instantly and drastically alter their images in a uniform manner. To demonstrate this technique we present an image passed through a 5x5 box blur filter in figure 6.

#### 4.4.2.1 The basics of image convolution

There are a multitude of ways to store images in memory depending on the basic format used, which kinds of compression techniques are applied etc. As image compression and storage is not the focus of this report the following explanation of image convolution with filters will assume that images are stored as an array containing pixels with each pixel containing a red, a blue and a green color value ranging from 0 to 255.

```

for(each pixel)

{

red = 0;

green = 0;

blue = 0;

for(each pixel in the filter matrix)

{

red += filterPixel.red * correspondingFilterValue;

blue += filterPixel.blue * correspondingFilterValue;

green += filterPixel.green * correspondingFilterValue;

}

newPixel.red = red;

newPixel.green = green;

newPixel.blue = blue;

}

```

Listing 4: Basic image convolution pseudocode

As described in listing 4 above, to perform a basic image convolution one iterates over every single pixel of an image and for every iteration the red, green and blue color values of the pixels surrounding it are aggregated and will be used as the color values of the corresponding pixel for the new filtered image. This, the act of calculating a new color value based on the value given in a filter matrix multiplied by the corresponding surrounding pixels color values is the essence of image convolution with filters [28].

What quickly becomes apparent after one understands the basics of this algorithm is that a straightforward sequential implementation will be done with four nested for loops, rarely a sign of a quickly executing algorithm. An observant reader comfortable with multi-core programming might also soon realize that the pixels for the new filtered image need not be calculated in sequence to produce the same result, which is why this type of algorithm lends itself so well to a GPU-accelerated approach.

For the sake of simplicity there are some notable omissions and simplification in this section that would need to be accounted for in an actual implementation of this algorithm. Among these we find such things as:

- Image constraints, how do we calculate the color values of pixels that are outside the image boundaries i.e. pixels that do not exists.

- Newly calculated color values that exceeds the minimum(0) or maximum(255) allowed color values.

- The brightness of the new pixels and by extension the whole new image will depending on the filter used often be significantly higher or lower than the original image.

The image boundaries problem is most efficiently dealt with in one of two ways, either you implement a check to see if the currently selected pixel in the filter is outside of the image before its color values are added to the calculation of the new pixel. We then either ignore these nonexistent pixels or use the color values of the next closest pixel e.g. a pixel with the position x=5 y=-2 would return the value of