## Institutionen för systemteknik Department of Electrical Engineering

#### Examensarbete

### Direct Digital Frequency Synthesis in Field-Programmable Gate Arrays

Examensarbete utfört i Elektroniska System vid Tekniska högskolan i Linköping

#### Petter Källström

$\label{eq:Linkoping2010} \mbox{LinH-ISY-EX--}10/4403--\mbox{SE}$   $\mbox{Link\"{o}ping 2010}$

Department of Electrical Engineering Linköpings universitet SE-581 83 Linköping, Sweden Linköpings tekniska högskola Linköpings universitet 581 83 Linköping

### Direct Digital Frequency Synthesis in Field-Programmable Gate Arrays

Examensarbete utfört i Elektroniska System vid Tekniska högskolan i Linköping av

Petter Källström

LiTH-ISY-EX--10/4403--SE

Handledare: Oscar Gustafsson

ISY, Linköpings universitet

Examinator: Oscar Gustafsson

ISY, Linköpings universitet

Linköping, 19 April, 2010

## Avdelning, Institution Division, Department

Electronic Systems Department of Electrical Engineering Linköpings universitet

| Datu | 1 |

|------|---|

| Date |   |

2010-04-19

| FAISKA HÖGSKOLT                                      |                                                              | E-581 83 Linköping, Swed                                                                                    | len                                                                                                                                                               |                                                                   |

|------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Språk<br>Language                                    |                                                              | Rapporttyp<br>Report category                                                                               | ISBN<br>—                                                                                                                                                         |                                                                   |

| □ Svenska/Swed ⊠ Engelska/Eng                        |                                                              | ☐ Licentiatavhandling ☐ Examensarbete ☐ C-uppsats ☐ D-uppsats ☐ Övrig rapport ☐                             | ISRN LiTH-ISY-EX10/ Serietitel och serienu: Title of series, numberin                                                                                             | mmer ISSN                                                         |

| URL för elekt: http://www.es.isy. http://urn.kb.se/r | .liu.se                                                      | version<br>urn:nbn:se:liu:diva-56550                                                                        |                                                                                                                                                                   |                                                                   |

| T;+10                                                | rect Digi                                                    |                                                                                                             | in Field-Programmable G                                                                                                                                           | ate Arrays                                                        |

| ger<br>VH<br>tar                                     | is thesis<br>nerates a<br>HDL, suit<br>get is Fi<br>Focus in | Phase to Sine Amplitude<br>table for Direct Digital 1<br>eld Programmable Gate<br>1 this report is how an F | atlab program that suggest<br>e Converter (PSAC) in the<br>Frequency Synthesis (DDI<br>Arrays (FPGAs).<br>PGA works, different met<br>alities vs the hardware res | e hardware language<br>FS). Main hardware<br>hods for sine ampli- |

| Nyckelord<br>Keywords PS                             | AC, DD                                                       | FS, FPGA, Matlab, Freq                                                                                      | uency Synthesis                                                                                                                                                   |                                                                   |

### Abstract

This thesis is about creation of a Matlab program that suggests and automatically generates a Phase to Sine Amplitude Converter (PSAC) in the hardware language VHDL, suitable for Direct Digital Frequency Synthesis (DDFS). Main hardware target is Field Programmable Gate Arrays (FPGAs).

Focus in this report is how an FPGA works, different methods for sine amplitude generation and their signal qualities vs the hardware resources they use.

## Sammanfattning

Detta exjobb handlar om att skapa ett Matlab-program som föreslår och implementerar en sinusgenerator i hårdvaruspråket VHDL, avsedd för digital frekvenssyntes (DDFS). Ämnad hårdvara för implementeringen är en fältprogrammerbar grindmatris (FPGA).

Fokus i denna rapport ligger på hur en FPGA är uppbyggd, olika metoder för sinusgenerering och vilka kvaliteter på sinusvågen de ger och vilka resurser i hårdvaran de använder.

# Acknowledgments

I would like to thank my supervisor and examiner Oscar Gustafsson, and Daniel Källming for a good opponent. I would also want to thank Kent Palmkvist and a few others for technical support and advices during the thesis. The entire ES corridor, Mikael Karlsson, Emanuel Eliasson, Kaveh Azizi and the Bertramm group have also been very supportive and have kept me in a good mood - thank you all.

# Contents

| 1        | Intr              | $^{ m coduction}$                          |

|----------|-------------------|--------------------------------------------|

|          | 1.1               | Background                                 |

|          |                   | 1.1.1 DDFS                                 |

|          | 1.2               | Purpose                                    |

|          |                   | 1.2.1 Quality vs Resource Problem          |

|          | 1.3               | This Document                              |

|          | 1.4               | Project Approach and Overview              |

|          |                   | 1.4.1 Implementation Language              |

|          |                   | 1.4.2 Finding Existing Methods             |

|          |                   | 1.4.3 Target Architectures                 |

|          |                   | 1.4.4 Modeling and Analysis                |

|          |                   | 1.4.5 VHDL Implementation                  |

|          |                   | 1.4.6 Suggester                            |

|          | 1.5               | Limitations                                |

|          | 1.6               | Notations and Abbreviations                |

|          | 1.0               | Notations and Additions                    |

| <b>2</b> | Met               | thods 5                                    |

| _        | 2.1               | Symmetry Using Range Divider               |

|          | 2.2               | ROM/LUT                                    |

|          | $\frac{2.2}{2.3}$ | Decomposition                              |

|          | 2.0               | 2.3.1 Polynomial Interpolation Alternative |

|          |                   | 2.3.2 Phase Truncation Alternative         |

|          |                   | 2.3.3 Hutchinson's Approach                |

|          |                   | 11                                         |

|          |                   | * *                                        |

|          |                   | r i                                        |

|          | 0.4               | 2.3.6 Curticăpean's Approach               |

|          | 2.4               | CORDIC                                     |

|          |                   | 2.4.1 Janiszewskis Hybrid                  |

|          | 2.5               | Sine Compression                           |

|          |                   | 2.5.1 Very Coarse Approximations           |

|          | 2.6               | Complex Rotation                           |

| 0        | TT.               | 1 A 1 1 1                                  |

| 3        |                   | get Architectures 15                       |

|          | 3.1               | Common FPGA Architecture                   |

|          | 3.2               | Altera                                     |

|          | 3.3               | Xilinx                                     |

| 4        | ъ. т              | 1.1                                        |

| 4        |                   | deling 19                                  |

|          | 4.1               | Quality Units                              |

|          | 4.2               | Frequency Control Word Effects             |

|          | 4.3               | Rounding Noise Analysis                    |

|          |                   | 4.3.1 Methods                              |

|          | 4.4               | Algorithm Verification                     |

|          |                   | 4.4.1 ROM/Polynomial                       |

|          |                   | 4.4.2 Other Decomposition Solutions        |

|          |                   | 4.4.3 CORDIC                               |

|          |                   | 4.4.4 Sine Compression                     |

|          |                   | 4.4.5 Method Codes                         |

x Contents

|              | 4.5   | Truncation Noise Analysis              |   |

|--------------|-------|----------------------------------------|---|

|              |       | 4.5.1 Polynomial                       |   |

|              |       | 4.5.2 Other Decomposition Solutions    |   |

|              | 1 C   | 4.5.3 Sine Compression                 |   |

|              | 4.6   | Conclusion                             | 5 |

| 5            | Imp   | plementations 31                       | L |

|              | 5.1   | ROM 33                                 | 1 |

|              |       | 5.1.1 The Function create_rom          |   |

|              |       | 5.1.2 The VHDL Implementation          |   |

|              | 5.2   | SURD Implementation                    |   |

|              | 5.3   | Polynomials                            |   |

|              |       | 5.3.1 The Function psac_polynomial_rom |   |

|              |       | 5.3.2 The Function psac_polynomial     |   |

|              |       | 5.3.3 The Function create_polynomial   |   |

|              | 5.4   | Sunderland's                           |   |

|              | 5.4   | 5.4.1 The Function psac sunderland rom |   |

|              |       | 5.4.2 The Function psac_sunderland     |   |

|              |       | 5.4.3 The Function create sunderland   |   |

|              |       | 5.4.4 The VHDL Implementation          |   |

|              | 5.5   | Test Bench                             | 5 |

|              |       | 5.5.1 The Function create_testbench    | 5 |

|              |       | 5.5.2 The VHDL Solution                | ó |

|              | 5.6   | Automatic Generation/Verification      |   |

|              |       | 5.6.1 The Function test_psac           | ó |

| 6            | Sug   | gester 37                              | 7 |

| •            | 6.1   | The Properties                         |   |

|              | 6.2   | Cost Model                             |   |

|              | 6.3   | Algorithm                              |   |

|              |       |                                        |   |

| 7            | Res   | ult 39                                 | ) |

| 8            | Con   | aclusions And Possible Improvements 41 | 1 |

| Ü            | 8.1   | Conclusions                            |   |

|              | 8.2   | Suggested Improvements                 | 1 |

|              |       |                                        | _ |

| Bi           | bliog | graphy 45                              | 3 |

| $\mathbf{A}$ | Wh    | at is?                                 | 5 |

| В            | 0110  | ality and Resource Tables 47           | 7 |

| D            | -     | ROM/Polynomial                         |   |

|              | B.2   | Other Decompositions                   |   |

|              | 2.2   | B.2.1 The F and Method Groupings       |   |

|              |       | B.2.2 The Quality Groupings            |   |

|              | В.3   | Sine Compression                       | _ |

| ~            |       | •                                      |   |

| C            | Poly  | ynomial VHDL Example 58                | 3 |

### Chapter 1

### Introduction

This chapter will discuss the project and this report, and introduce some terms that can be good to know in the thesis.

### 1.1 Background

Digital electronics become more and more widely used compared to analogue electronics. Many tasks that have earlier been implemented with analogue circuits are today more suitable - one way or another - to be replaced by digital technology.

One area that grows fast is for instance wireless communication, where information is sent as radio waves. This requires that a sine wave is generated that can carry the information. This sine is comparably simple to generate in analogue electronics, and rather complicated to calculate for digital circuits, why the analogue method still is in use. The analogue method has two drawbacks; it is hard to control the frequency exactly, and the generated signal may be hard to manipulate.

You can use a microprocessor to calculate the sine, but this report will focus on the ASIC<sup>1</sup> implementation - that is how to program logics that calculate the sine, rather than how to program the instructions that is executed by the microprocessor in order to calculate the sine.

The main target for the ASIC is to use an FPGA - Field Programmable Gate Array, that is an electrical chip with such programmable logic. This will be further described in chapter 3, "Target Architecture".

#### 1.1.1 DDFS

The term DDFS stands for Direct Digital Frequency Synthesis, and in this context means a way to produce a sine wave with a given frequency. The method also use a clock signal that defines the time between one calculation and the next. The clock signals typically flips between '0' and '1' at a frequency of  $f_{clk}$ , for instance 300 MHz.

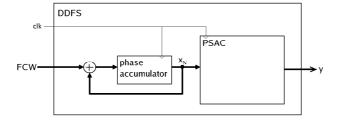

The DDFS usually contains a counter that counts from 0 to something big, and then restarts, and counts up with a number – the Frequency's Control Word (FCW). The content of the counter is treated as a phase (angle, here called  $x_N$ ), and is then sent to a Phase to Sine Amplitude Converter (PSAC) that calculates a sine value, y, for the phase. See figure 1.1 for an illustration.

This sine value will then over time have the shape of a sine wave with the exact frequency that was given to the DDFS.

Figure 1.1. Illustrations of the basic DDFS structure

$<sup>^{1}</sup>$ Application Specific Integrated Circuit, a method of customizing the hardware to a specific need

2 Introduction

#### 1.2 Purpose

This thesis aims to develop a method for automatic generation of the PSACs for FPGAs, for different PSAC methods, including a way of suggesting a suitable PSAC method for different types of FPGAs and for different requirements. The purpose of this is to simplify the creation of the PSACs for FPGA developers.

#### 1.2.1 Quality vs Resource Problem

One of the main problems with a manual implementation is that the user may have different requirements on the signal. It can for instance be suitable to lower the quality on the signal in order to save some resources. Problems like this can be time wasting to solve manually, and this project includes a solution for that (see chapter 6, "Suggester").

#### 1.3 This Document

This documents is mainly intended for those with a basic knowledge in digital technology and a basic knowledge in math. For those who are not familiar with all terms and expressions, appendix A, "What is...?" contains a list of abbreviations/concepts and a short explanation.

#### 1.4 Project Approach and Overview

Before the project was started there were some things to decide. First of all which language the project should be implemented in, but also how to split up the project in sub tasks.

This section introduce each of those sub tasks, which more or less corresponds to the chapters in this report.

#### 1.4.1 Implementation Language

The first thing to do was to decide in which programming language the system should be built. There were three main alternatives: Matlab from The Mathwork Inc, Microsoft Excel and any high level language, like C++ or Java.

| Language | Benefit                                                                                        | Drawbacks                                       |

|----------|------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Matlab   | Very good support for mathematic analysis, convenient file I/O, widely used for similar tasks. | Everyone doesn't have Matlab.                   |

| Excel    | Easy to create good graphical user interface, and to store much data.                          | Hard to do an FFT in Visual Basic.              |

| C++      | Widely known.                                                                                  | Not very suitable for this kind of calculations |

Table 1.1. Benefits and drawbacks for different implementation languages

The choice fell on Matlab, mostly because of the mathematical intensity of the program.

#### 1.4.2 Finding Existing Methods

The first thing to do was to elaborate what else had already been done on the topic. The most interesting and suitable methods were then chosen for futher analysis.

In this task it is good to have read up on the FPGA architectures, to easier know which methods are interesting, and which one can be omitted at once. However, when studying the FPGAs it is good to know the methods, to know what to look for. Therefore this task is put before the FPGA architecture study.

Many methods have one or more parameters, the most obvious one is the decomposition of the phase bits, which can be done in N+1 ways (if the phase is N bits wide). In this report, and in the Matlab implementation, the word *configuration* is used to describe a specific method and its different parameters. More about this in chapter 2, "Methods".

1.5 Limitations 3

#### 1.4.3 Target Architectures

The main target is FPGAs, and the *suggest* functionality<sup>2</sup> should have a good knowledge about the different FPGA types and architectures, why a study of the most common FPGA types is required.

#### 1.4.4 Modeling and Analysis

The chosen methods are verified and analyzed in Matlab. The worst methods are discarded from the project. In order to analyze the resources needed for the methods, this task should be performed after the FPGA architecture study.

#### 1.4.5 VHDL Implementation

The main purpose with the project is to create a PSAC. In practice that means that one or more files with VHDL-code<sup>3</sup> are generated.

There are several other hardware describing languages as well, but the requirements specify a VHDL generator.

The Matlab implementation should be able to generate VHDL implementations for the given methods, in all possible configurations, plus testbenches that verify the functionality.

This task must of course be performed after the method modeling. This task is covered in chapter 5.

#### 1.4.6 Suggester

One of the more tricky parts of the project is to write an algorithm that checks for the best implementation according to given preferences/limitations and a given FPGA architecture.

This task must also be performed after the method modeling. In order to get a better model of the resources that are used, this task is placed after the VHDL implementation.

#### 1.5 Limitations

The main limitation of this master thesis is the time of 800 hour, including time to present and defend the work and the time to hold the place of an opponent. Within this time limit the thesis aims to be as good as possible, according to some prioritation.

The main effects are a reduced subset of algorithms/methods, a limited extension of configurations within the methods, and a restriction to only test the code for Matlab in Unix, in difference to Windows and/or Octave<sup>4</sup>. It also affects the suggester function, both in efficiency and in complexity. More about the limitations in the respective chapters.

#### 1.6 Notations and Abbreviations

This is only a short list of the most important abbreviations. See Appendix A - "What is...?" for a complete list of abbreviations, notations and descriptions.

${

m d} {

m B}$  - decibel, a logarithmic scale for comparing relative difference.

dBc - dB relative to the carrier, measured as the difference in power.

FCW - Frequency Control Word

**LUT** - Look Up Table, or function generator.

ModelSim - A program from Mentor Graphics aimed to compile and simulate for instance VHDL code.

**PSAC** - Phase to Sine Amplitude Converter, a sine function.

SFDR - Spurious Free Dynamic Range, a way to measure signal purity.

SINAD - Signal to Noise And Distortion ratio, a way to measure signal purity.

$<sup>^2 \</sup>mathrm{Suggests}$  a suitable configuration - see 1.4.6

$<sup>^{3}</sup>$ the VHDL code describes how the FPGA should be programmed to realize the intended behaviors

<sup>&</sup>lt;sup>4</sup>Octave is an open source variant of Matlab

4 Introduction

- $\mathbf{SNR}\,$  Signal to Noise Ratio, a way to measure signal purity.

- ${\bf SURD}$  Symmetry Using Range Divider. A phrase within this thesis for a way to reduce the input range to the PSAC.

VHDL - A Hardware Description Language, describes how the information flows and is treated in the FPGA.

### Chapter 2

### Methods

There are of course a number of ways to compute a sine wave.

The authors Langlois et al. has summarized a large number of DDFS techniques[1], which is the main source of methods in this thesis.

#### Some notations:

- $N\,$  Number of bits in phase. The two MSBs are not used more than in the SURD.

- C Coarse, some of the most significant bits from the phase (except the two used by the SURD).

- F Fine, some of the least significant bits from the phase.

- D Some bits between C and F in Sunderland's method. D is just a suitable letter between C and F.

- W Number of bits in amplitude. The MSB is not used more than in the SURD.

- K Number of coefficients in polynomial solutions.

- **SURD** Symmetry Using Range Divider. A method that uses the symmetry of the sine to reduce the phase with two bits.

- x The first 90° of the phase.

$x_{N,Q,C,D,F}$  - The phase containing the N, C, D resp. F bits.  $x_Q$  is the two bits used by SURD.

Those notations will be futher described in their respective sections below.

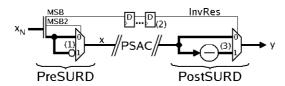

### 2.1 Symmetry Using Range Divider

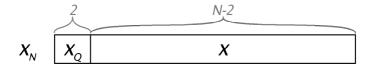

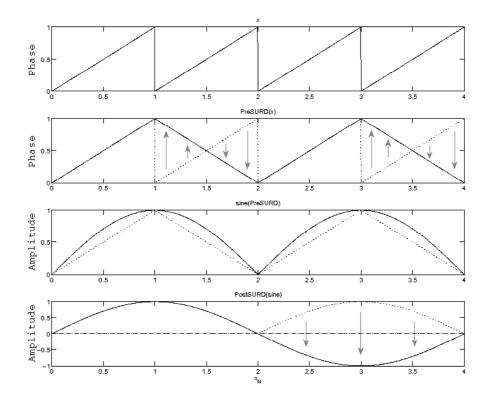

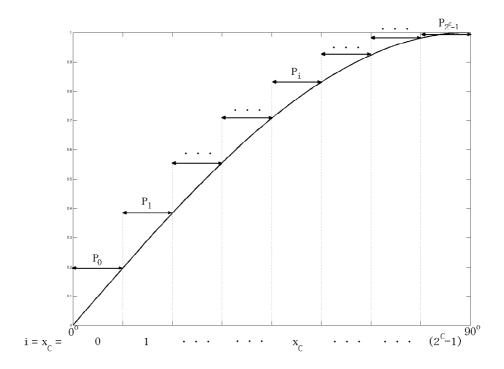

The Symmetry Using Range Divider (SURD) decreases input phase from range  $0-360^{\circ}$  to either  $0-90^{\circ}$ , for algorithms returning only sine, or  $0-45^{\circ}$  for quadrature algorithms, returning both sine and cosine, by using the symmetry in the sine wave. This method is used as a wrapper function around other algorithms, minimizing the input range to the functions and compensating the output result from the function. All discussions and illustrations here will assume the  $0-90^{\circ}$  version, for simplicity reasons. See figure 2.1 for the phase decomposition, or figure 2.2 for the phase and amplitude effects. Equation 2.1 illustrate the math behind the SURD.

$$\sin(90^{\circ} \cdot x_N) = \sin(90^{\circ} \cdot (x_Q + x)) = \begin{cases} \sin(90^{\circ} \cdot x), & x_Q = 0 \ (0^{\circ}) \\ \sin(90^{\circ} \cdot (1 - x)), & x_Q = 1 \ (90^{\circ}) \\ -\sin(90^{\circ} \cdot x), & x_Q = 2 \ (180^{\circ}) \\ -\sin(90^{\circ} \cdot (1 - x)), & x_Q = 3 \ (270^{\circ}) \end{cases}$$

(2.1)

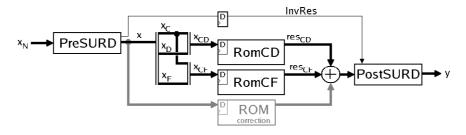

The SURD is divided into the two parts PreSURD and PostSURD, where PreSURD handles the phases phase inversion (1-x), and PostSURD inverts the result, if needed.

The values  $x_N$  are in equation 2.1 meant to be a number 0 to 4  $(0 \le x_N < 4)$ , which implies that  $x_Q$  (that are the 2 MSBs of  $x_N$ ) are an integer with value 0, 1, 2 or 3. x is then the fraction part,  $0 \le x < 1$ .

Note that  $x_N$  is just a series of ones and zeros, and that this representation uses a decimal point between the  $x_Q$  and x fields. The sine approximation function may set the decimal point somewhere else for a suitable representation.

Because of the great benefits with SURD (see table 2.1), it is used in all implementations.

6 Methods

Figure 2.1. SURD decomposition

Figure 2.2. The SURD signal effects.

| Benefits   | The other algorithms can be designed with a very much smaller           |

|------------|-------------------------------------------------------------------------|

|            | memories.                                                               |

| Drawbacks  | In those cases there is a ROM dedicated for this task and it is         |

|            | big enough to fit the entire 0–360°, than that may be slightly          |

|            | faster.                                                                 |

| Other      | This method does not affect the precision of the result, but will       |

| properties | increase the $t_{CO}$ and $t_{SU}$ with the time of one adder resp. one |

|            | inverter, and will use slightly more logic resources. Depending         |

|            | on which other algorithm that is used it will however save loads        |

|            | of ROMS and/or FAs.                                                     |

Table 2.1. Some properties for SURD

### $2.2 \quad \text{ROM/LUT}$

The ROM/LUT method uses a big look up table, or better known as ROM, to store the entire function. See table 2.2.

$$\sin(x) = R[x], \tag{2.2}$$

where R is the ROM and x is used as the address.

This method has high priority according to the requirements. Langlois[1] mention it.

2.3 Decomposition 7

| Benefits   | Works fast, very simple.                                    |

|------------|-------------------------------------------------------------|

| Drawbacks  | Grows exponentially with input width.                       |

| Other      | Exact result (as exact as possible with actual word width). |

| properties | Suitable for simulator and FPGAs with big ROMs and/or high  |

|            | performance requirements.                                   |

Table 2.2. Some properties for ROM implementation

#### 2.3 Decomposition

Another method than the ROM solution may be "decomposition solutions" (or "bipartite solutions"), discussed as follows.

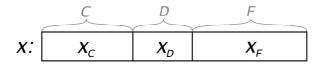

Split the N-2 input bits into C (Coarse) MSB and F (Fine) LSB, where N=2+C+F (the 2 MSBs are reserved for the SURD). Let  $x=x_C+x_F$  be the values stored by the C and F bits, as illustrated in figure 2.3. Or, in the Sunderland's approach case (see section 2.3.4 below), let N be 2+C+D+F and  $x=x_C+x_D+x_F$  in a similar way. See figure 2.3 and 2.4.

Figure 2.3. Decomposition of quartile phase into two fields

Figure 2.4. Decomposition of quartile phase into three fields

For example, if N = 11, C = 4, F = 5 and  $x_N = 11000011111$ , then  $x_Q = 11$ ,  $x_C = 0000$  and  $x_F = 11111$ .

#### 2.3.1 Polynomial Interpolation Alternative

Split the phase into  $2^C$  parts, and calculate each part as a polynomial, according to figure 2.5. Because you will use all coefficients for a certain polynomial in the same time ( $\pm$  a few clock cycles), you can read out all the coefficients for that polynomial in the same time. Therefore, you can use a ROM with  $2^C$  lines and store the K coefficients side by side in it, one polynomial per ROM line. This way you only need one ROM (which may however require several ROMs if the total required number of bits does not fit into one ROM).

When using K coefficients you get a (K-1):th grade polynomials. The "x" in the polynomials are the F fraction bits,  $x_F$ , according to equations 2.3.

$$\sin(x_C + x_F) \approx R_1[x_C], & K = 1

\sin(x_C + x_F) \approx R_1[x_C] \cdot x_F + R_2[x_C], & K = 2

\sin(x_C + x_F) \approx (R_1[x_C] \cdot x_F + R_2[x_C]) \cdot x_F + R_3[x_C], & K = 3

\sin(x_C + x_F) \approx (\dots(R_1[x_C] \cdot x_F + R_2[x_C]) \dots + R_{K-1}[x_C]) \cdot x_F + R_K[x_C], & K \ge 4,$$

(2.3)

where  $R_k[x_C]$  is coefficient k for polynomial  $x_C$ .

The coefficients on a line is used for a (K-1):th grade polynomial applied on the F truncated bits. This allows C to be small if K is fairly big without loosing too much quality. In table 2.3 the quality terms SINAD and SFDR are used, those will be described in section 4.1, Modelling -  $Quality\ Units$ .

Worth mentioning is that a high K requires complex calculations, which will cause a high latency and/or a huge restriction of the clock frequency.

The last coefficient in the ROM  $(R_K)$  will always be W-1 bits wide, because it must store the "offset" position for that polynomial, which will be within the range  $[0, 2^{W-1})$ . The previous coefficients will shrink with roughly C bits per coefficient.

8 Methods

Figure 2.5. Polynomial decomposition illustration

| K     | С     | Benefit                                 | Drawbacks                                               |

|-------|-------|-----------------------------------------|---------------------------------------------------------|

| Big   | Big   | Exact value (except noise in W's LSBs). | Much memory and many (rather small) multipliers needed. |

| Big   | Small | Few ROMs are needed.                    | Many and big multipliers are required. Low SFDR.        |

| Small | Big   | Few and small mults are required.       | Much memory is required.<br>Low SINAD.                  |

| Small | Small | Resources effective, easy to calculate. | Rough approximation. Very low SFDR and SINAD.           |

Table 2.3. Some properties for polynomial solution

One of the big implementation problems with polynomials is to create the coefficients, and which approach to use. In table 2.4 some methods are mentioned, which will be analyzed futher in chapter 4.

| Least Square  | $Minimize average error \Rightarrow maximize SFDR (in general)$                           |

|---------------|-------------------------------------------------------------------------------------------|

| Chebyshev     | A kind of interpolation where the interpolation points have been chosen to minimize the   |

|               | maximum error $\Rightarrow$ maximize ENOB $\Rightarrow$ maximize SINAD (in general).      |

| Interpolation | Like Chebyshev interpolation, but "stretch out" the points so there are one point in each |

|               | edge of the ranges.                                                                       |

| TaylorLeft    | Taylor series from a point in the left edge of the F interval.                            |

| TaylorMid     | Taylor series from a point in the middle of the F interval.                               |

| Truncation    | Just pick the left most value in each range. Requires that K=1.                           |

| ROM           | The ROM solution (section 2.2) is a truncation special case where F=0.                    |

Table 2.4. Some methods for polynomial coefficients

An explanation to the Chebyshev points: They are placed within each polynomial ranges in the same way as the values  $\cos(\frac{90^{\circ}+i\cdot180^{\circ}}{K}), i=0..K-1$  are placed in the range (-1,1).

2.3 Decomposition 9

#### 2.3.2 Phase Truncation Alternative

Truncate the input to the C MSB in order to save some ROM. This is a special case of polynomial interpolation where K=1.

This method can be seen either as a way of reducing the ROM size as mentioned (by reducing the phase bus to the memory), or it can be seen as taking a ROM solution and increase the phase accumulator width with F bits in order to increase the frequency precision, but without giving the extra bits to the ROM – see table 2.5.

| $\sin(x_C + x_F) \approx \sin(x_C) = R[x_C] \tag{2.4}$ | .4) | ) |

|--------------------------------------------------------|-----|---|

|--------------------------------------------------------|-----|---|

| View      | Truncated phase bus | Increased phase accumulator  |

|-----------|---------------------|------------------------------|

| Benefits  | Smaller ROM.        | Higher frequency resolution. |

| Drawbacks | Much more noise.    | More noise.                  |

Table 2.5. Some properties for phase truncation

#### 2.3.3 Hutchinson's Approach

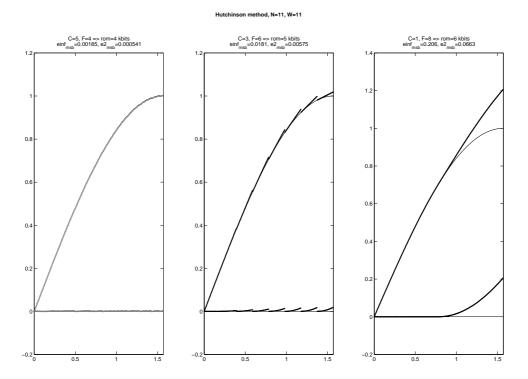

Hutchinson  $et\ al.[2]$  suggested a trigonometric approximation. This approach[1] uses the approximation  $\sin(x) = \sin(x_C + x_F) = \sin(x_C)\cos(x_F) + \sin(x_F)\cos(x_C) \approx \sin(x_C) + \sin(x_F)\cos(x_C)$  which is without multiplication, since  $\sin(x_F)\cos(x_C)$  is precalculated and stored in a separate ROM - a ROM that will be as high as the pure ROM solution, but around W-F bits wide instead of W-1 bits. In figure 2.6 the 3 graphs illustrate a solution where C is 5, 3 and 1. The einf and e2 values are the maximum and average errors for the values, the terms will be better described in section 4.1. See also table 2.6.

Figure 2.6. Hutchinsons implementation examples

The method can be improved by setting the content of ROM 2 to a "correction" to ROM 1.  $R_2[x] = \sin(x) - R_1[x_C]$ , rather than Hutchinsons original assignment  $R_2[x] = \sin(x_F)\cos(x_C)$ . This improvement does not affect the implementation cost of the algorithm, but removes the algorithmic error. This variant is in this thesis called *Hutchinson's 2*, and it will be futher analyzed in chapter 4, *Modelling*, page 19.

10 Methods

| Benefit   | Very simple and quick.                            |  |

|-----------|---------------------------------------------------|--|

| Drawbacks | Requires very much memory, and is rather inexact. |  |

Table 2.6. Some properties for Hutchinsons approach

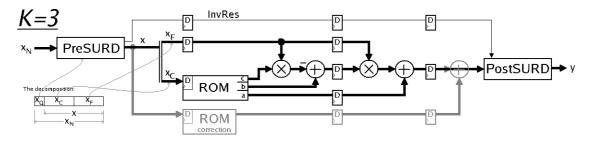

#### 2.3.4 Sunderland's Approach

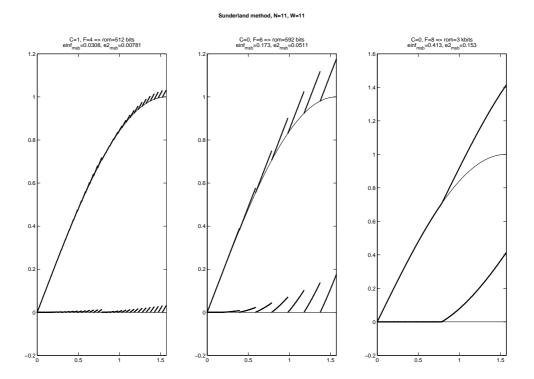

An extended version of Hutchinson's method was suggested by Sunderland *et al.*[3], where they divide the N-2 input bits into 3 fields:

$$\sin(x) = \sin(x_C + x_D + x_F)$$

$$= \sin(x_C + x_D) \cdot \cos(x_F) + \cos(x_C + x_D) \cdot \sin(x_F)$$

$$= \sin(x_C + x_D) \cdot \cos(x_F) + \cos(x_C) \cdot \cos(x_D) \cdot \sin(x_F) - \sin(x_C) \cdot \sin(x_D) \cdot \sin(x_F)$$

$$\approx \sin(x_C + x_D) + \cos(x_C) \cdot \sin(x_F)$$

(2.6)

and so

$$\sin(x) = R_1[x_{C+D}] + R_2[x_{C+F}]$$

$$R_1[x_{C+D}] = \sin(x_C + x_D)$$

$$R_2[x_{C+F}] = \cos(x_C) \cdot \sin(x_F)$$

(2.7)

where  $x_{C+D}$  is the  $x_C$  and  $x_D$  bits concatenated together, and corresponding for the  $x_{C+F}$  bits.

Figure 2.7. Sunderlands implementation examples

| Benefit    | Very simple to implement in VHDL.                              |  |

|------------|----------------------------------------------------------------|--|

| Drawbacks  | Rather bad precision.                                          |  |

| Other      | Due to the triple decomposition of the phase, this method have |  |

| properties | very many configurations when $N$ is big.                      |  |

Table 2.7. Some properties for Sunderlands method

2.4 CORDIC

#### 2.3.5 Nicolas' Approach

Nicholas et. al. [4] suggested that the ROM contents in Sunderland's approach should be changed and optimized according to some goal (e.g. high SFDR). Due to time limitation this optimization will not be investigated.

#### 2.3.6 Curticăpean's Approach

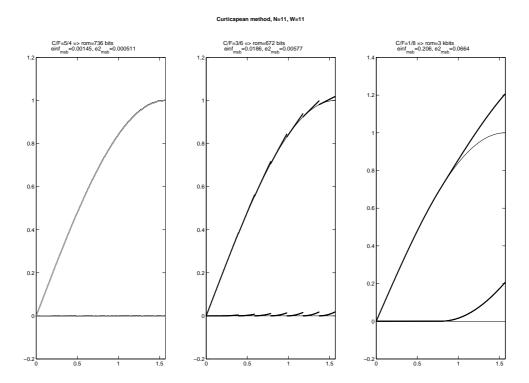

Curticăpean et al.[5] suggested an improvement to Hutchinson's approach, that stores  $\sin(x_F)$  and  $\cos(x_C)$  in one ROM each and multiplies them together. See table 2.8 and figure 2.8.

$$\sin(x) \approx R_1[x_C] + R_2[x_C] \cdot R_3[x_F]$$

(2.8)

where  $R_1$  and  $R_2$  can be stored side by side in one Rom (because both are addressed with  $x_C$ ).

Figure 2.8. Curticăpeans implementation examples

| Benefit   | Saves some ROM.          |

|-----------|--------------------------|

| Drawbacks | Cost one multiplication. |

Table 2.8. Some properties for Curticăpeans method, relative Hutchinson's

#### 2.4 CORDIC

The CORDIC algorithm is a very resource efficient and "exact" method for sine calculation, it requires no multiplication and very little ROM. It does, however, require N-2 comparison with corresponding additions/subtractions, that must be executed after each others, which gives either a slow clock or a very large latency.

CORDIC stands for **Co**ordinate **Ro**tation **Di**gital **C**omputer, and is a set of algorithms based on the idea to process the input with smaller and smaller steps toward the zero, and at the same time process the output with some corresponding operations. In each step there is a binary decision, like "increase or decrease" which affect the following operations on the (modified) input and output values. After a predefined number of steps, the output is ready. The CORDIC sine method is carefully described on for instance Wikipedia[6].

This method has medium priority according to specification.

12 Methods

| Benefit   | No multiplication, very limited ROM. |

|-----------|--------------------------------------|

| Drawbacks | Takes long time.                     |

Table 2.9. Some properties for CORDIC

#### 2.4.1 Janiszewskis Hybrid

Look up the first C bits in a LUT, and feed that to step K..W of the CORDIC. Due to the drawback in table 2.10, this method will not be implemented.

| Benefit  | Faster than CORDIC, smaller than LUT                   |  |

|----------|--------------------------------------------------------|--|

| Drawback | Still not as fast as for instance polynomial solution. |  |

Table 2.10. Some properties for Janiszewskis hybrid

#### 2.5 Sine Compression

Calculate a rough estimation to the sine somehow, and include a ROM that contains the errors. This ROM will be as high as the pure ROM solution, but much thinner.

As estimation it is convenient to use any of the methods discussed in Decomposition above, or a "very coarse approximation" (see below). Some drawbacks and benefits are shown in table 2.11.

| Benefit   | You get an "exact" solution (errors $\leq \frac{1}{2}LSB$ ) |

|-----------|-------------------------------------------------------------|

| Drawbacks | The extra ROM needs to be $2^{N-2}$ rows high.              |

Table 2.11. Some properties for sine compression

This compressed ROM may then and now be called a "correction ROM" to the approximating function.

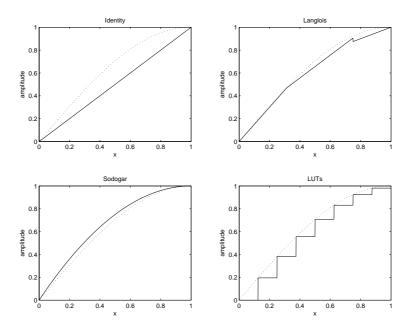

#### 2.5.1 Very Coarse Approximations

Some extremely simple approximations is worth mentioning. All approximating  $\sin(90^{\circ} \cdot x)$ , where  $0 \le x < 1$ .

The cost of using those approximation is the cost of the approximations themselves plus one adder, where you add the approximated value to the compressed ROM output. The cost of one register for storing the approximation may be needed. See figure 2.9 for illustrations.

Due to time limitations, those methods will not be implemented.

#### **Identity Approximation**

The simplest one.

$$\sin(x) \approx x. \tag{2.9}$$

This can be shown to save 2 bits of ROM width, which holds even if x is truncated to 5 bits.

#### Langlois Approximation

Named after Langlois and Al-Khalili[7].

$$\sin(x) \approx \begin{cases} \frac{3}{2}x, & 0 \le x < \frac{5}{16} \\ \frac{5}{32} + x, & \frac{5}{16} \le x < \frac{3}{4} \\ \frac{1+x}{2}, & \frac{3}{4} \le x < 1 \end{cases}$$

(2.10)

This will save 4 bits of ROM width. All segments in this solution uses at most one adder and no other logic.

#### Sodogar Approximation

Named after Sodogar and Lahiji[8].

$$\sin(x) \approx x(2-x), \quad 0 \le x < 2.$$

(2.11)

The subtraction is done using a simple inverse of all bits in x since  $0 \le x < 2$  causes 2 - x to be equal -x, and the negation of x can be approximated to bitwise inverse in this case. The formula is valid for  $0 \le x < 2$ , but the interesting part is  $0 \le x < 1$  due to the SURD.

The error here is  $<\frac{1}{16}$ , which means we save 4 bits of ROM width.

#### LUT Approximation

As will be described in chapter 3, "Target", the FPGAs are to a high degree built up of very small memories, so called LUTs. These have typically 4 or 6 address bits, say L input bits, and just one output bit. If you feed the L MSBs of  $x_C$  to some LUTs, the LUT outputs can act as an approximation, and will save L-1 bits from the ROM, assuming at least L LUTs are used. Except the Identity matrix, that do not require any LUTs at all, the other "very coarse approximation" methods will require at least as many LUTs as precision uses for the approximation. Because of that, this method will not be more expensive than for instance Langlois approximation.

If you take only the L-1 MSB of  $x_C$ , you can use the output from the compressed ROM as the last bit, and combine it with the adder functionality (if the used FPGA architecture allows it). In this way the compression may be around L-2 bits to the same cost as the identity approximation. The exact value will however not be investigated due to time limitations.

In the illustration, L is set to 3 for illustration reasons, and the worst error is  $\approx 0.2$ , just below position x=0.125. This saves 2 bits of ROM width. The figure does not illustrate effects from a limited number of LUTs used.

Figure 2.9. Some "Very Coarse Approximations"

#### Usability

The four approximations above can be used not only to compress the pure ROM solutions; they can also be used to compress any coefficients that store a sine table, e.g. the last field in the polynomial solutions, or the first ROM in Sunderlands method.

14 Methods

### 2.6 Complex Rotation

Input the frequency rather than the angle. Have a complex vector v, that is multiplied with the complex constant  $e^{angle \cdot i}$  in each step.

| Benefit   | Pretty simple, low power, since the sine and cosine is to be calculated once per frequency change rather than once per sample. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|

| Drawbacks | Low precision.                                                                                                                 |

Table 2.12. Some properties for complex rotation

$This\ method\ has\ very\ low\ priority,$  according to thesis specification.

In applications where the power is critical and resources are cheep this is interesting. If you use a PSAC to calculate the complex value  $e^{freq \cdot i}$  every time the frequency is changed, and then and now between that do a correction of the actual vector v, the method can save some power because the complex multiplication in some cases may be more energy efficient than the PSAC calculation.

### Chapter 3

## Target Architectures

The main implementation target device is FPGAs, Field Programmable Gate Arrays. The FPGA is a chip that is configurable to behave in almost any way the user want it.

There are two main competing FPGA vendors, Altera and Xilinx, with some FPGA families and generations each. There are other vendors as well, but this thesis will only cover those two.

To simplify the handling of the different families/generations of FPGAs in this thesis, they have been assigned abbreviations, or codes. See tables 3.2 and 3.4 for the codes.

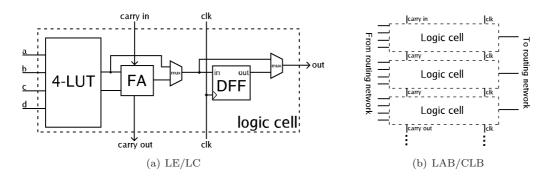

#### 3.1 Common FPGA Architecture

The FPGA is normally used for digital signal processing, "glue logic", and other types of digital tasks. Therefore it is both generalized and specialized in the same time. Typical FPGA components are:

Logic: FPGAs are mainly built up by many small *LUTs* (look-up tables), *FAs* (Full Adders), and *DFFs* (D-flip-flops), and small *muxes*. Many LUTs can also work as memories. Xilinx group the logic into slices/CLBs, Altera group it into LE/ALM/LABs. See figure 3.1 for a very simplified example of how the structure can be organized. A LUT with e.g. 6 inputs (6-LUT) can implement any combinatorial function of those inputs.

**Memories:** There use to be synchronous memory blocks, often configurable as RAM, ROM, shift register or FIFO buffer, and in several different heights and widths. For example the size 4 kBits =  $2^{12}$  bits can be shaped as 8 bits wide and  $512=2^9$  rows high, or 32 bits wide and  $128=2^7$  rows high. The address widths are 9 and 7 bits in those cases, respectively.

Memories can have single port (SP) or dual port (DP) features, meaning you can access the memory content from one and two sides, respectively. This thesis will only use ROMs with SP configurations, and hence the rest of the memory configurations are not listed here. For futher improvements the DP may be interesting, as noted below.

In most cases there are optional bits reserved for parities, usually 1 parity bit for each byte.

The LUTs are very small ROMs. Many of the LABs/CLBs can configure the LUTs as e.g. RAM, but in this thesis that is extraneous. The ROM function is implicit, and omitted in the ROM list.

Multipliers: Most FPGAs are equipped with dedicated binary multipliers. Altera uses  $18 \times 18$  bits signed or unsigned, Xilinx uses  $25 \times 18$  signed in their latest FPGAs.

FPGAs typically contains a lots of other features as well, but nothing interesting in this thesis.

#### 3.2 Altera

Altera has a number of different FPGA families[9]. Common for all is:

**Logic:** The logic is based on LABs (Logic Array Blocks), consisting of either 8-10 ALMs (Adaptive Logic Module) or 10-16 LE (Logical Element).

• The **LE** has typically a 4-LUT, a FA and a DFF. In some devices the entire FA is implemented into the LUT.

Figure 3.1. Simplified example of a general FPGA logic architecture

• The **ALM** has typically four 4-LUTs, two FAs and two DFF, but can be configured as two 5-LUTs with two DFF, or one 6-LUT with a DFF.

**ROMs:** There are a few different ROMs. See table 3.1.

**Multipliers:** They have 18x18-multipliers, most of them configurable as  $2 \cdot (9 \times 9)$  or  $1 \cdot (18 \times 18)$ . Both signed and unsigned (and combined) values are accepted.

| Name  | Size                       | Modes | Address widths                |

|-------|----------------------------|-------|-------------------------------|

| M512  | 512  bits + 1  parity/byte | SP    | 5-9 (18–1 bits data wide)     |

| M4K   | 4 kBits + 1 parity/byte    | SP/DP | 7 – 12 (36–1 bits data wide)  |

| M9K   | 8 kBits + 1 parity/byte    | SP/DP | 8 – 13 (36–1 bits data wide)  |

| M144K | 128 kBits + 1 parity/byte  | SP/DP | 11 – 14 (72–8 bits data wide) |

Table 3.1. ROMs in Altera's FPGAs

A summary of the Altera FPGAs and their relevant resources can be seen in table 3.2.

| Device                            | Code     | ROM        | LABs    | Multipliers |

|-----------------------------------|----------|------------|---------|-------------|

| Cyclone 1 [10]                    | cy1      | M4K        | 10 LEs  | no          |

| Cyclone 2 [11]                    | cy2      | M4K        | 16 LEs  | 18x18       |

| Cyclone 3 [12], Cyclone 4 [13]    | cy3, cy4 | M9K        | 16 LEs  | 18x18       |

| Arria 1 [14]                      | ar1      | M512, M4K  | 8 ALMs  | 18x18       |

| Arria 2 [15]                      | ar2      | M9K        | 10 ALMs | 18x18       |

| Stratix 1 [16], Stratix 1 GX [17] | sx1      | M512, M4K  | 10 LEs  | 18x18       |

| Stratix 2 [18] Stratix 2 GX [19]  | sx2      | M512, M4K  | 8 ALMs  | 18x18       |

| Stratix 3 [20], Stratix 4 [21]    | sx3, sx4 | M9K, M144K | 10 ALMs | 18x18       |

Table 3.2. Alteras FPGA Families

#### 3.3 Xilinx

Xilinx has two different families with different generations. Common for all:

**Logic:** The logic is based on *CLBs* (Configurable Logic Blocks), which have two or four *Slices*. Two notations within this thesis:

- The slice<sub>2</sub> has  $2 \cdot (4 LUT + FA + DFF)$ , but can act as a 5-LUT + 1 DFF. [22]

- The slice<sub>4</sub> has  $4\cdot(6\text{-LUT} + \text{FA} + 2 \text{ DFFs})$ , but can act as an 8-LUT + 1 DFF. [23]

Xilinx often implements the FAs into the LUTs, except the carry logic, to optimize speed and complexity.

Memories: There are two types of memories: Block SelectRAM = 4-32 kBits, in this thesis abbreviated 'bsRam', or Slices configured as 16 or 64 bits. Many bsRams do not have any preload functionality and will not be listed as ROM. The slices ROM functionality is simple LUT usage, which are implicit and will not be listed in table 3.3.

3.3 Xilinx 17

Multipliers: Xilinx' multipliers are typically 18x18 bits signed. Unlike Alteras FPGAs you cannot configure them to be unsigned. To do an unsigned multiplication, which this thesis deals with, you must sacrifice the sign bit, so that typically 17x17 bits are used.

| Name    | Size                       | Modes | Address Widths               |

|---------|----------------------------|-------|------------------------------|

| bsRam16 | 16  kbits + 1  parity/byte | SP/DP | 10–14 (18–1 bits data width) |

| bsRam32 | 32 kbits + 1 parity/byte   | SP/DP | 10–15 (36–1 bits data width) |

Table 3.3. ROMs in Xilinx' FPGAs

The resource types for the different generations are summarized in table 3.4.

| Device                       | Code    | ROM          | $_{ m CLBs}$          | Multipliers       |

|------------------------------|---------|--------------|-----------------------|-------------------|

| Spartan-3 [24]               | sp3     | bsRam16      | 4 slices <sub>2</sub> | 18x18 signed      |

| Spartan-6 [25]               | sp6     | bsRam16 [26] | 2 slices <sub>4</sub> | 18x18 signed [27] |

| Virtex [28, 29, 30]          | vx1     | no           | 2 slices <sub>2</sub> | 8x8 or 16x16      |

| Virtex-II [31, 32]           | vx2     | no           | 4 slices <sub>2</sub> | 18x18             |

| Virtex-4 [33, 34]            | vx4     | bsRam16      | 4 slices <sub>2</sub> | 18x18 signed      |

| Virtex-5 [35], Virtex-6 [36] | vx5,vx6 | bsRam32 [37] | 2 slices <sub>4</sub> | 25x18 signed [38] |

Table 3.4. Xilinx' FPGA Families

## Chapter 4

## Modeling

As decided in the introduction chapter, section 1.4.1, the main language will be Matlab. Therefore all models will be built in Matlab.

The models have two purposes: Verify (and understand) the algorithm, and to analyze the signal quality. The quality term refers to how good the signal is compared to how much noise it contains.

In the digital environment in an FPGA there are two types of noises: Truncation and rounding noise. Truncation noise origins from approximation errors<sup>1</sup>, e.g. introduced error when doing piecewise linear approximation. Rounding noise is introduced because of finite word length in operations and result, e.g. 11 bits precision in result, or several mult/adds where each operation introduce a rounding error.

#### 4.1 Quality Units

The quality of a signal uses to be measured in SFDR<sup>2</sup> and SNR<sup>3</sup>. The SFDR measures how much "louder" the carrier is than the loudest noise tone. The SNR compares the carrier to the sum of the noise, after the harmonics to the signal has been removed, this is meant to measure the noise that does not belong to the carrier.

Because the base frequency is  $\frac{f_{clk}}{2^N}$  (where  $f_{clk}$  is the clock frequency), and all occurring tones, carrier as well as noise, have frequencies  $FCW \cdot \frac{f_{clk}}{2^N}$ , all tones are harmonics to the base frequency. Therefore there is no 'SNR noise'. However, the rounding noise is "white" over these discreet frequencies, and can be seen as not belonging to the carrier signal. Therefore the SNR will in this thesis be counted as only the Carrier-to-rounding-noise error.

To count the harmonics as noise, you use the measurement  $SINAD^4$ , which counts everything that is not the carrier as noise.

The SFDR compares the carrier and the loudest noise tone. That tone is usually generated by a truncation error. The truncation errors is only limited by the approximating algorithm, and they occurres often "in groups" - that is, if the approximation has an error in one point, it is likely to have similar errors in the closest points.

Other quality methods are the ENOB<sup>5</sup>, average error and maximum error, according to the following definitions:

$$ENOB = \frac{SINAD-1.76}{6.02}$$

$$e2 = \sqrt{\text{mean}(e_i^2)}, \quad e_i = \text{error in point no } i.$$

$$einf = \max(|e_i|) \qquad i = 0, 1, ..., 2^N - 1$$

$$(4.1)$$

e2 is the average error (or more accurately the RMS<sup>6</sup> error), and einf is the maximum error. The notations are derived from the mathematical terms  $e_2$  and  $e_{\infty}$ , where  $e_{\alpha} = (\text{mean}(e_i^{\alpha}))^{1/\alpha}$

<sup>&</sup>lt;sup>1</sup>error = difference between calculated and exact sine value

<sup>&</sup>lt;sup>2</sup>Spurious Free Dynamic Range

<sup>&</sup>lt;sup>3</sup>Signal to Noise Ratio

<sup>&</sup>lt;sup>4</sup>Signal to noise and distortion ratio

<sup>&</sup>lt;sup>5</sup>Effective Number Of Bits

<sup>&</sup>lt;sup>6</sup>Root Mean Square

20 Modeling

### 4.2 Frequency Control Word Effects

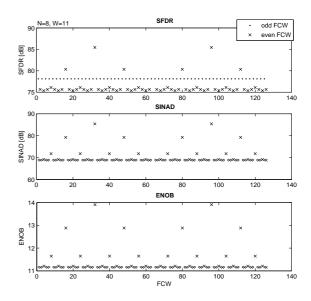

The DDFS' generated signal frequency is controlled through the Frequency Control Word (FCW), according to equation 4.2.

$f(FCW) = f_{clk} \cdot \frac{FCW}{2^N}, \ 0 \le FCW < \frac{2^N}{2}$  (4.2)

Because of frequency mirror effects the harmonic tones will be mirrored back again when FCW is big, and due to number theoretical effects, it will never be added upon any other frequency as long as FCW is odd. Therefore the amplitude of the noise is not affected by (odd) FCW, and neither are the amplitude of the carrier signal.

In figure 4.1 you can see how the qualities are constant when the FCW is odd, but how they are affected when FCW is even. One reason for the even FCW behavior is that half of the phases are used twice, and the rest is not used at all. Some rounding errors will therefore not affect the result. Which phases that are used or not depends on which phase you "start" on, with many possible quality values for a given signal at a given (even) FCW.

Because of this a normal approach is to measure only one odd FCW, and the analysis of a signal is therefore drastically eased. The analysis in this thesis will use that technique.

einf and e2 are dependent of the output values for each phase, independent of the order, and are thus FCW independent (as long as FCW is odd).

Figure 4.1. FCW effects on the SFDR, SINAD and ENOB

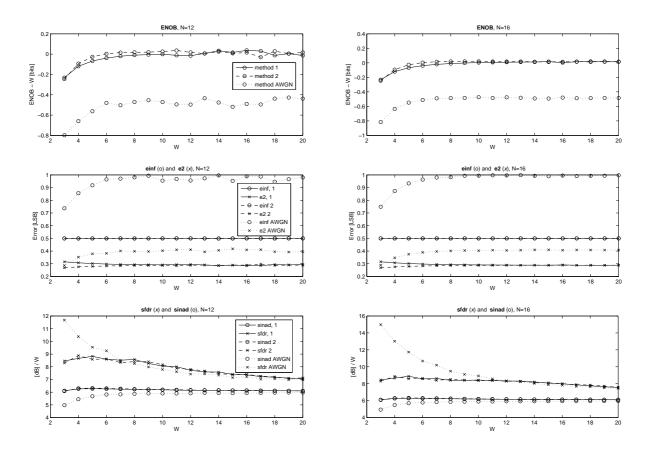

### 4.3 Rounding Noise Analysis

In this chapter rounding noise from operations will be discussed under the noise sections belonging to each method, and this section will only deal with method independent noise.

The rounding noise can be seen as white if W is fairly big, typically at least N-2, and is therefore not sensitive to FCW. If W is less than N-2, then some harmonics can occur, but those will never be bigger than the base tone divided by  $2^W$ . In cases of decomposition, the limit may be C-2 rather than N-2, or some other limit.

#### 4.3.1 Methods

Three rounding methods are covered, illustrated by an example where W=11, which gives an integer range between -1023 and 1023 for the result after rounding. E.g.  $y(phase) \approx 1023 \cdot \sin_0(phase)$ , where y is the output value from the DDFS, phase is an angle ( $x_Q$  in the DDFS), and  $sin_0$  is an approximation algorithm (the PSAC).

Method 1 describes the maximum amplitude solution.

$$y_0(phase) = round(1023.5 \cdot \sin_0(phase)) \tag{4.3}$$

where round(...) round toward closest integer.

**Method 2** gives possibly less rounding errors when the phase is very close to  $\pm 90^{\circ}$ , but over all very similar noise analyzing results as Method 1.

$$y_0(phase) = round(1023 \cdot \sin_0(phase)) \tag{4.4}$$

**Method AWGN** is a method to add some White Gaussian Noise with amplitude  $\frac{1}{2}$ ·LSB.

$$y_0(phase) = round(1023 \cdot \sin_0(phase) + rnd - 0.5) \tag{4.5}$$

where rnd is a (new) random value between 0 and 1 for each phase.

An example can illustrate the direct effect of the AWGN: If the amplitude  $y_0$  for a phase should have been 511.75 before rounding, then it may be 511, but with 75 % probability it will be 512.

The effect on the signal, compared to method 2, is that the **SFDR** is increased because the probability rounding tends to counteract the continuous aviations in the rounding errors that can occur when W < N - 2.

The **SINAD** is decreased, because we add some noise. **ENOB** and **einf** is 0.5 bits worse, because it can be rounded away up to 1 LSB. **e2** is increased with around 41 % (that means multiplied with  $\approx \sqrt{2}$ ).

Due to all the negative aspects of *method AWGN*, and the notice that the only profit of it is not likely to happen often, that method is discarded. And because of this, the exact effect from decomposition will not be investigated.

The difference between method 1 and 2 is so small so only method 1 will be used (a bigger amplitude is always preferred).

Figure 4.2. The ROM signal quality for the different rounding methods

Figure 4.2 illustrates the methods for N=12 and 16. You can see how *Method AWGN* (dotted lines) boosts the SFDR (cross marker in lower graphs) when W is small, but make all other quality units worse.

### 4.4 Algorithm Verification

This section discusses how the algorithms from chapter 2 works, and briefly what signal qualities that can be expected from the different configurations.

As defined chapter 2, the  $phase = 90^{\circ} \cdot (x_Q + x)$ , where  $x_Q = 0, 1, 2$  or 3, and  $0 \le x < 1$ . Due to the SURD<sup>7</sup> implementation, this chapter will only illustrate the first quadrant, which means  $x_Q = 0$ .

For decomposition methods, that split the N-2 bits in x into C+F or C+D+F bits, the (virtual) decimal point in x will be moved from the left to the right of  $x_C$ , making  $x_C$  to an integer,  $0 \le x_C < 2^C$ , indexing all sub ranges in the first quartile, and  $x_F$  (or  $x_D + x_F$ ) to the new fractional part.

#### 4.4.1 ROM/Polynomial

In this chapter  $x = x_C + x_F$ , where  $x_C$  is the integer part  $0...(2^C - 1)$ , and  $x_F$  is the fractional part  $0 \le x_F < 1$  with F bits precision, which will be used as the 'x' in the polynomials. Remember that there will be one

<sup>&</sup>lt;sup>7</sup>Symmetry Using Range Divider

22 Modeling

polynomial for each  $x_C$ , whose coefficients are stored in one (or several) ROMs/LUTs addressed with the  $x_C$ .

The number of coefficients to the polynomials (per range) is denoted K, which gives K = polynomial order + 1. The implementation uses Horners scheme in order to save some multiplication, it calculates e.g. the polynomial  $P(x_F) = a_0 + a_1x_F + a_2x_F^2 + a_3x_F^3$  as  $((a_3x_F + a_2)x_F + a_1)x_F + a_0$ , if K = 4.

#### Coefficient Evaluation Methods

There are a number of different methods for calculating the content of the ROM storing the polynomial coefficients, which affects the qualities of the result.

This thesis will investigate five methods, each of them is well known or inherits from a well known approximation method.

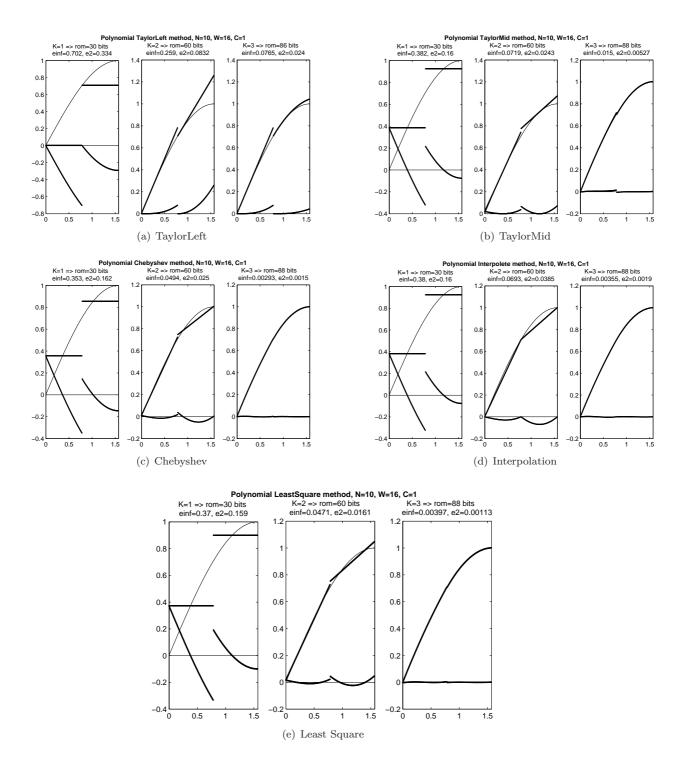

The graphs in figure 4.3 (on page 23) shows only the first quadrant, because the rest is just mirrored versions of this. For illustration reasons C is set to 1 in all examples, which gives 2 polynomials in the shown quadrant. Furthermore N=10, which gives  $x_F = 7$  bits, or a resolution of  $2^{-7} = 1/128$ , or 128 points per polynomial. The average and maximum errors are mentioned in each graph, as well as the number of ROM bits used to store the actual solution. This is further discussed in the analysis section.

- The **TaylorLeft** approach approximates the sine with a Taylor polynomial around  $\sin(x_C)$  in the range  $[x_C, x_C + 1)$ . This gives good approximation for small  $x_F$ , but bad when  $x_F$  is close to 1. In the analysis section there will be shown that this method is the worst method in all categories.

- The **TaylorMid** approach works like the TaylorLeft, but approximates the sine around  $x_C + 0.5$ , which increases the quality significantly compared to TaylorLeft.

- The Chebyshev approach equals the sine in K equality points distributed according to the Chebyshev zeros, to minimize the maximum error. The Chebyshev zeros in the range (-1, 1) are the solution to  $0 = \cos(K \cdot \arccos(x))$ , which gives  $x = \cos(\frac{\pi}{2K} \cdot \{1, 3, ..., 2K 1\})$ . Because  $0 \le x < 1$ , rather than -1 to 1, the Chebyshev points are just rescaled from (-1, 1) to (0, 1).

An exception is made for K = 1 (when the sine is nothing but a constant within each range), which should have given a Chebyshev point in  $x_F = 0.5$ , but instead takes the mean of the max and min sine values in the range. This way the approximation still minimize the maximum error for K=1.

- The Interpolation approach works like the Chebyshev, but the equality points are "stretched out" so the left- and rightmost points are placed in  $x_F = 0$  and  $x_F = 1 2^{-F}$  to ensure the result will be continuous between the integer ranges. When K = 1 the  $x_F = 0.5$  point is used as equality point.

- The **LeastSquare** approach is a least square polynomial approximation, that minimizes the sum of the squares of the errors. When the Chebyshev approach tries to minimizes the maximum error einf, this one minimizes the RMS error<sup>8</sup> e2.

In figure 4.3 the different methods are illustrated. Some clarification about the graphs: The three plots for each method differs in the K value only, which is 1, 2 and 3, from left to right. The thin line is the real sine. The upper thick line of dots is the approximated sine, and the lower thick line of dots is the error = the approximated minus the real sine.

The two Taylor methods are mostly mathematical approximations that are "good" when  $x_F$  is "close to" 0 resp. 0.5.  $x_F$  is however uniformly distributed over [0, 1), why those methods (especially TaylorLeft) are supposed to be worse in all quality measurements than the other three, who are better optimized for the entire range [0, 1).

For these five methods there are however a security scaling, that is not plotted in figure 4.3. This scales down the coefficients if the sine exceeds 1 in any point, which saves the final hardware implementation the need of an overflow detection.

Some comments about different variants:

- The pure **ROM/LUT** solution is any of the methods with K=1 and F=0.

- The truncation solution is the TaylorLeft with K=1 and F>0 (see fig 4.3a, left graph).

- The linear interpolation is the Interpolation with K=2 and F>0 (see fig 4.3d, middle graph).

$<sup>^{8}</sup>$ root-mean-square error = square root of the mean of the  $|errors|^{2}$

Figure 4.3. Illustrations of the different polynomial coefficients methods

24 Modeling

#### 4.4.2 Other Decomposition Solutions

After polynomial solution there are three mentioned methods left from the decomposition classification: Hutchinson's, Sunderland's and Curticapean's. The Hutchinson's approach can be modified by changing the value in on of the ROMs, which gives a fourth approach.

**Hutchinson's approach**:  $\sin(x) \approx \sin(x_C) + \sin(x_F) \cdot \cos(x_C)$ , used without multiplication, since  $\sin(x_F) \cdot \cos(x_C)$  is precalculated and stored in a ROM (same height but thinner than storing entire  $\sin(x)$ ). This approximation requires that 2C > W + 1 to "hide" the truncation errors in the rounding noise. See figure 2.6 (pg 9) for an illustration.

The alternative to Hutchinson's approach, in this project called "**Hutchinson's 2**", is to store  $\sin(x) - \sin(x_C)$  rather than  $\sin(x_F) \cdot \cos(x_C)$ , which will give no truncation error at all, and in general no higher resource usage then Hutchinson's original approach, why the original will be discarded. This approach will be further investigated under the subject "Sine compression".

Sunderland's approach:  $\sin(x) \approx \sin(x_C + x_D) + \cos(x_C) \cdot \sin(x_F)$ . Store  $\sin(x_C + x_D)$  and  $\cos(x_C) \cdot \sin(x_F)$  in one ROM each, and add together. This reduces the size of the ROM quite markedly when comparing with Hutchinson's. The approximation requires that 2C + D > W to hide the truncation errors. Illustrated in figure 2.7.

Curticăpean's approach:  $\sin(x) \approx \sin(x_C) + \sin(x_F) \cdot \cos(x_C)$ , used with multiplication, since  $\sin(x_F)$  and  $\cos(x_C)$  are stored in one ROM each. This method gives the same truncation but slightly more rounding noise than Hutchinson's, but on the other hand reduces the ROM size markedly. This also needs 2C > W + 1 to hide the truncation error. Illustrated in figure 2.8.

However; if 3C > W + 2 then  $\sin(x_F) = x_F$  (but scaled due to the adjusted phase unit), why this method turns to polynomial. Therefore, assume  $3C \le W + 2$  and  $2C \le W + 1$  in the analysis.

#### 4.4.3 CORDIC

The CORDIC algorithm is a classical way to calculate the sine.

Advantage: Uses no multiplication. Only as many ROM words are needed as there are bits in the output. It is quadrature (generates both sine and cosine).

Disadvantage: Requires very much logic/low clock frequency, very low throughput, or very high latency, depending on how it is pipelined. Of course you can have a trade off between those.

Due to time limitation and low priority, this method will not be implemented.

#### 4.4.4 Sine Compression

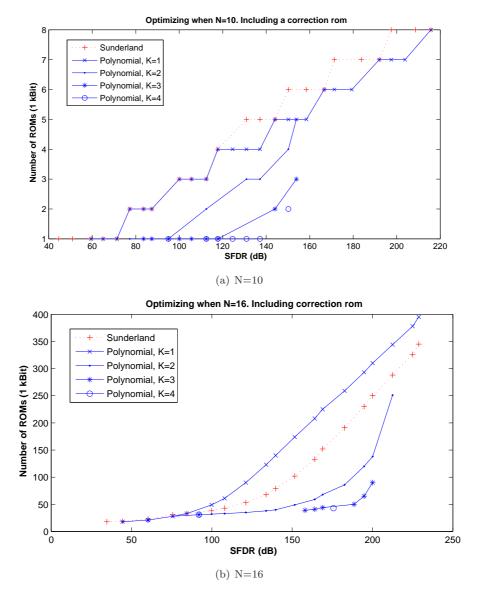

This method is very general. It can be combined with any of the methods mentioned earlier. It stores all truncation errors (but negated), and those are added to the approximated signal in the PSAC. This gives the effect that all truncation errors disappear, and only rounding noise is left. The cost is a large ROM with high  $= 2^{N-2}$  rows, and as wide as it takes to store the truncation errors. Therefore there is only a need to look at the maximum error factor (einf) at the used method. For the polynomial case this means that the Chebyshev method will be used in most cases. Experiments show that Chebyshev and interpolation polynomials and the Sunderland's approach are the best methods.

The choice of approximation method and its parameters is called the *configuration* of the sine compression in this thesis.

Table 4.1 shows the resources needed for some configurations. The last field of the configuration is the method code (see table 4.3). The columns ROM (appr), ROM (corr) and ROM (tot) are the ROM sizes used by the approximating method, the Correction ROM, and the sum of them respectively. The column mults shows the number of multipliers that is used.

When letting the sine compression function choose a configuration from given N and W only (without specifying the rest of the configuration), it minimizes the number of ROM bits used for methods using zero to three multipliers. See table 4.2 for some examples. Polynomial configurations will normally use two ROMS while Sunderland's will use three.

See the Appendix B for more tables showing resource usages.

#### 4.4.5 Method Codes

The final product will use a number of codes for the methods and their sub groups, as shown in table 4.3.

For instance cpi is a polynomial method with the interpolation coefficients approach, and a correction ROM on that.

| Configuration             | ROM (appr) | ROM (corr) | ROM (tot)         | mults |

|---------------------------|------------|------------|-------------------|-------|

| N=10, W=11, F=1, K=1, pls | 1.25 kbits | 1 kbits    | <b>2.25</b> kbits | 0     |

| N=10, W=11, F=2, K=1, pls | 640 bits   | 1.25 kbits | 1.88 kbits        | 0     |

| N=10, W=11, F=4, K=1, pls | 160 bits   | 1.75 kbits | <b>1.91</b> kbits | 0     |

| N=10, W=11, F=2, K=2, pls | 960 bits   | 512 bits   | 1.44 kbits        | 1     |

| N=10, W=11, F=4, K=2, pls | 272 bits   | 768 bits   | <b>1.02</b> kbits | 1     |

| N=10, W=11, F=2, K=3, pls | 960 bits   | 768 bits   | <b>1.69</b> kbits | 1     |

| N=10, W=11, F=4, K=3, pls | 320 bits   | 768 bits   | 1.06 kbits        | 2     |

| N=9, W=10, F=4, K=2, pc   | 128 bits   | 384 bits   | <b>512</b> bits   | 1     |

| N=9, W=12, F=4, K=2, pc   | 160 bits   | 512 bits   | <b>672</b> bits   | 1     |

| N=11, W=10, F=4, K=2, pc  | 448 bits   | 1.5 kbits  | <b>1.94</b> kbits | 1     |

| N=11, W=12, F=4, K=2, pc  | 576 bits   | 1 kbits    | <b>1.56</b> kbits | 1     |

| N=11, W=10, F=6, K=2, pc  | 128 bits   | 1.5 kbits  | <b>1.62</b> kbits | 1     |

| N=11, W=12, F=6, K=2, pc  | 160 bits   | 2 kbits    | <b>2.16</b> kbits | 1     |

| N=10, W=11, F=3, C=4, s   | 1.06 kbits | 1 kbits    | <b>2.06</b> kbits | 0     |

| N=10, W=11, F=3, C=3, s   | 704 bits   | 1.25 kbits | <b>1.94</b> kbits | 0     |

| N=10, W=11, F=4, C=3, s   | 1.03 kbits | 1.25 kbits | <b>2.28</b> kbits | 0     |

Table 4.1. Some examples of sine\_compression resources

| N  | $\mathbf{W}$ | 0 mults            | 1 mults            | 2 mults            | 3 mults            |

|----|--------------|--------------------|--------------------|--------------------|--------------------|

| 10 | 10           | F=2, C=3, s        | F=4, $K=2$ , $pc$  | F=6, K=3, pc       | F=7, K=4, pc       |

|    |              | ROMs = 1.44  kbits | ROMs = 752 bits    | ROMs = 604 bits    | ROMs = 574 bits    |

| 10 | 16           | F=3, K=1, pc       | F=3, K=2, pc       | F=5, K=3, pc       | F=5, K=4, pc       |

|    |              | ROMs = 3.22  kbits | ROMs = 1.81  kbits | ROMs = 1.05  kbits | ROMs = 864 bits    |

| 10 | 20           | F=4, K=1, pc       | F=4, $K=2$ , $pc$  | F=4, K=3, pc       | F=5, K=4, pls      |

|    |              | ROMs = 4.3  kbits  | ROMs = 3.05 kbits  | ROMs = 1.48  kbits | ROMs = 992 bits    |

| 16 | 10           | F=6, C=4, s        | F=10, K=2, pc      | F=12, K=3, pls     | F=14, K=4, pc      |

|    |              | ROMs = 36.2  kbits | ROMs = 32.2  kbits | ROMs = 32.1  kbits | ROMs = 48  kbits   |

| 16 | 16           | F=4, C=5, s        | F=5, K=2, pc       | F=11, K=3, pc      | F=12, K=4, pc      |

|    |              | ROMs = 66  kbits   | ROMs = 43  kbits   | ROMs = 48.3  kbits | ROMs = 48.2  kbits |

| 16 | 20           | F=3, C=8, s        | F=6, K=2, pc       | F=9, K=3, pc       | F=11, K=4, pc      |

|    |              | ROMs = 104  kbits  | ROMs = 55.8  kbits | ROMs = 49.4  kbits | ROMs = 48.5  kbits |

| 20 | 10           | F=9, K=1, pc       | F=14, K=2, pc      | F=16, K=3, pls     | F=18, K=4, pc      |

|    |              | ROMs = 517  kbits  | ROMs = 512  kbits  | ROMs = 512  kbits  | ROMs = 768  kbits  |

| 20 | 16           | F=6, C=6, s        | F=9, K=2, pc       | F=15, K=3, pc      | F=16, K=4, pc      |

|    |              | ROMs = 588  kbits  | ROMs = 523  kbits  | ROMs = 768  kbits  | ROMs = 768  kbits  |

| 20 | 20           | F=5, C=9, s        | F=7, K=2, pc       | F=13, K=3, pc      | F=15, K=4, pc      |

|    |              | ROMs = 776  kbits  | ROMs = 568  kbits  | ROMs = 769  kbits  | ROMs = 768  kbits  |

Table 4.2. Sine compression optimized for some N and W

| Code | Method                                           | VHDL         |

|------|--------------------------------------------------|--------------|

| р    | Any kind of polynomial                           |              |

| ptl  | Polynomial with Taylor Left coefficients         |              |

| ptm  | Polynomial with Taylor Mid coefficients          |              |

| pc   | Polynomial with Chebyshev coefficients           | $\checkmark$ |

| pi   | Polynomial with Interpolation coefficients       | $\checkmark$ |

| pls  | Polynomial with Least Square coefficients        | $\checkmark$ |

| S    | Sunderland                                       | <b>√</b>     |

| c#   | Sine Compression. $\#=$ any of the methods above | ✓            |

*Note:* The methods marked with a " $\checkmark$ " in the column "VHDL" are implemented as VHDL generators.

Table 4.3. The method codes for modelled methods

All methods mentioned in chapter 2, *Methods*, are not listed here. Only those that has been modelled are listed.

# 4.5 Truncation Noise Analysis

Most of the truncation (algorithmic) errors will appear as an overtone to the base frequency, due to the systematic pattern in the error – if a point is too low then its neighbors are probably also too low, which typically gives

26 Modeling

a harmonic. However, errors that occur in only one or perhaps two neighboring phases will not be identified as a real overtone, because it will occur only once (or twice) every  $2^N$  times, why those will be thought of as white noise.

## 4.5.1 Polynomial

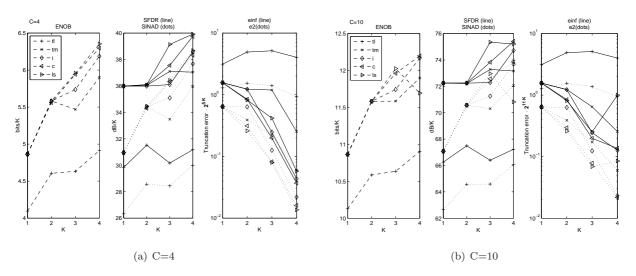

Figure 4.4 illustrates the quality measurements when modeling the methods for C=4 and 10, and with rather big F and W to filter out all but the truncation effects. This gives a huge error for small K, and a big improvement when K increases. Note the rather strange scales in the figures, especially the error graphs.

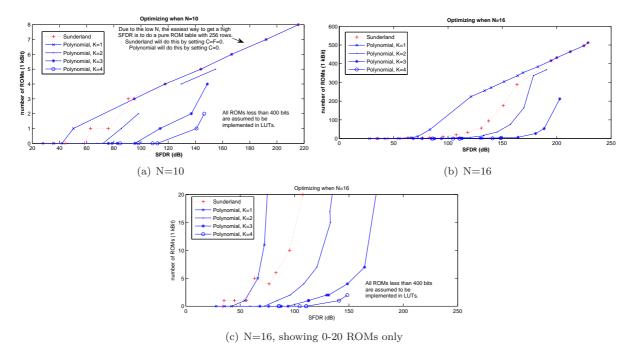

Some test where different C, F and K has been tested has resulted in the conclusion as follows (See appendix B for tables with results).

One limitation in all coefficient assignments is the double floating point precision used by Matlab, causing an upper limit of about 50 bits. This affects the *LeastSquare* method most and is clearly visible in figure 4.4(b), the ' $\triangleright$ ' marker where K=4.

- The **TaylorLeft** approach ('+' marker in the figures) gives of course very bad qualities. According to the tests the TaylorLeft has the worst qualities of the five methods. In figure 4.4 this is clearly visible, low ENOB/SFDR/SINAD and high error. This method is therefore discarded.

- The **TaylorMid** approach (' $\times$ ' marker in the figures) are (as expected) better than TaylorLeft, but not as good as the three later methods (at least for K > 2). This method is also discarded.

- The **Chebyshev** approach ('<' marker in the figures) have a rather low maximum error (continuous line to the right in fig 4.4a and b). The Chebyshev approach to minimize the max error works as best when C and/or K is big.

- The **Interpolation** approach (' $\diamond$ ' marker in the figures) works like the Chebyshev, but distributes the equality points different.

- The **LeastSquare** approach (' $\triangleright$ ' marker in the figures) minimizes the e2 factor.

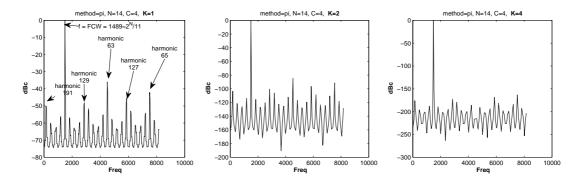

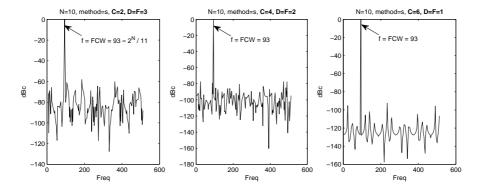

Some examples of frequency spectrum's derived from truncation errors are shown in figure 4.5. The graphs shows the configuration 'method=pi, C=4', for N=14, W is set to "big" to remove the rounding errors. K is set to 1, 2 and 4 in the graphs. FCW is set to 1489 in this case. All three plots have frequency components around -350 dB and below, but those are derived from rounding errors rather than truncation errors, and have therefore been removed in the graphs. The main noise frequency is harmonics number  $\{1, 2, 3, ...\} \cdot 2^{2+C} \pm 1 = \{63, 65, 127, 129, 191, 193, ...\}$  to the main tone, with decreasing amplitude.

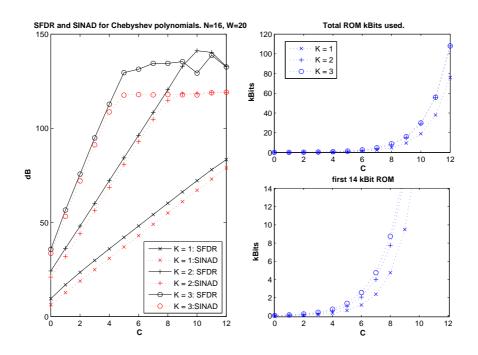

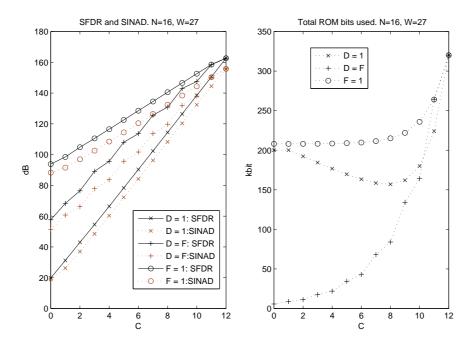

Figure 4.6 show the SFDR, SINAD and ROM result for different C values, N = 16, W = 20,  $K = \{1, 2, 3\}$ , and Chebyshev coefficients. You can clearly see the W effects on the SFDR. The upper graph to the right shows number of kBits ROM used, and the lower graph to the right the same thing, but rescaled y-axis.

Figure 4.4. Example of different polynomial qualities

See Appendix B, Analysis, for tables with values.

Figure 4.5. Examples of truncation derived frequency spectrum's for polynomial interpolation, where K=1, 2 and 4

${\bf Figure~4.6.~SFDR/SINAD~and~ROM~usage~for~Chebyshev~polynomials~with~different~C}$

#### 4.5.2 Other Decomposition Solutions

The four solutions Hutchinson's, Hutchinson's 2, Sunderland's and Curticapean's differs in results.

- The **Hutchinson's** has no advantages at all over Hutchinson's 2, and is therefore discarded.