Thesis No. 1021

### Integrated Optimal Code Generation for Digital Signal Processors

by

#### Andrzej BEDNARSKI

#### Akademisk avhandling

som för avläggande av teknologie doktorsexamen vid Linköpings universitet kommer att offentligt försvaras i Planck, Fysikhuset, Linköpings universitet, onsdagen den 7 juni 2006, kl. 13.15

#### Abstract

In this thesis we address the problem of optimal code generation for irregular architectures such as Digital Signal Processors (DSPs).

Code generation consists mainly of three interrelated optimization tasks: instruction selection (with resource allocation), instruction scheduling and register allocation. These tasks have been discovered to be  $\mathcal{NP}$ -hard for most architectures and most situations. A common approach to code generation consists in solving each task separately, *i.e.* in a decoupled manner, which is easier from a software engineering point of view. Phase-decoupled compilers produce good code quality for regular architectures, but if applied to DSPs the resulting code is of significantly lower performance due to strong interdependences between the different tasks.

We developed a novel method for fully integrated code generation at the basic block level, based on dynamic programming. It handles the most important tasks of code generation in a single optimization step and produces an optimal code sequence. Our dynamic programming algorithm is applicable to small, yet not trivial problem instances with up to 50 instructions per basic block if data locality is not an issue, and up to 20 instructions if we take data locality with optimal scheduling of data transfers on irregular processor architectures into account. For larger problem instances we have developed heuristic relaxations.

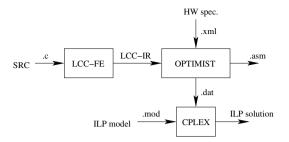

In order to obtain a retargetable framework we developed a structured architecture specification language, xADML, which is based on XML. We implemented such a framework, called OPTIMIST that is parameterized by an xADML architecture specification.

The thesis further provides an Integer Linear Programming formulation of fully integrated optimal code generation for VLIW architectures with a homogeneous register file. Where it terminates successfully, the ILP-based optimizer mostly works faster than the dynamic programming approach; on the other hand, it fails for several larger examples where dynamic programming still provides a solution. Hence, the two approaches complement each other. In particular, we show how the dynamic programming approach can be used to precondition the ILP formulation.

As far as we know from the literature, this is for the first time that the main tasks of code generation are solved optimally in a single and fully integrated optimization step that additionally considers data placement in register sets and optimal scheduling of data transfers between different registers sets.

This work has been supported by the Ceniit (Center for Industrial Information Technology) 01.06 project of Linköpings universitet, ECSEL (Excellence Center for Computer Science and Systems Engineering), and the RISE (Research Institute for Integrational Software Engineering) project supported by SSF (Stiftelsen för Strategisk Forskning), the Swedish Foundation for Strategic Research.

Department of Computer and Information Science Linköpings universitet SE-581 83 Linköping, Sweden

ISBN 91-85523-69-0

ISSN 0345-7524

## Linköping Studies in Science and Technology Dissertation No. 1021

# Integrated Optimal Code Generation for Digital Signal Processors

by

#### Andrzej Bednarski

Department of Computer and Information Science Linköpings universitet SE-581 83 Linköping, Sweden

Linköping 2006

To Leonia ...

#### **Abstract**

In this thesis we address the problem of optimal code generation for irregular architectures such as Digital Signal Processors (DSPs).

Code generation consists mainly of three interrelated optimization tasks: instruction selection (with resource allocation), instruction scheduling and register allocation. These tasks have been discovered to be NP-hard for most architectures and most situations. A common approach to code generation consists in solving each task separately, *i.e.* in a decoupled manner, which is easier from a software engineering point of view. Phase-decoupled compilers produce good code quality for regular architectures, but if applied to DSPs the resulting code is of significantly lower performance due to strong interdependences between the different tasks.

We developed a novel method for fully integrated code generation at the basic block level, based on dynamic programming. It handles the most important tasks of code generation in a single optimization step and produces an optimal code sequence. Our dynamic programming algorithm is applicable to small, yet not trivial problem instances with up to 50 instructions per basic block if data locality is not an issue, and up to 20 instructions if we take data locality with optimal scheduling of data transfers on irregular processor architectures into account. For larger problem instances we have developed heuristic relaxations.

In order to obtain a retargetable framework we developed a structured architecture specification language, xADML, which is based on XML. We implemented such a framework, called OPTIMIST that is parameterized by an xADML architecture specification.

The thesis further provides an Integer Linear Programming formulation of fully integrated optimal code generation for VLIW architectures with a homogeneous register file. Where it terminates successfully, the ILP-based optimizer mostly works faster than the dynamic programming approach; on the other hand, it fails for several larger examples where dynamic programming still provides a solution. Hence, the two approaches complement each other. In particular, we show how the dynamic programming approach can be used to precondition the ILP formulation.

ii Abstract

As far as we know from the literature, this is for the first time that the main tasks of code generation are solved optimally in a single and fully integrated optimization step that additionally considers data placement in register sets and optimal scheduling of data transfers between different registers sets.

This work has been supported by the Ceniit (Center for Industrial Information Technology) 01.06 project of Linköpings universitet, ECSEL (Excellence Center for Computer Science and Systems Engineering), and the RISE (Research Institute for Integrational Software Engineering) project supported by SSF (Stiftelsen för Strategisk Forskning), the Swedish Foundation for Strategic Research.

### **Acknowledgments**

The work presented in this thesis could never be accomplished without the support of many people. I would like to take the opportunity here to formally thank them and apologize for those I forgot to mention.

First of all I would like to thank my supervisor Christoph Kessler for his precious help and advice during this whole period of Ph.D. study. He spent a large amount of his time guiding me in research work and writing. For me he was the perfect supervisor that a Ph.D. student may have ever expected. This work could have never been completed without Christoph's support.

Also, I would like to thank Peter Fritzson who offered me the opportunity to join Programming Environments Laboratory (PELAB) in March 1999, and triggered in me the interest for code generation.

Many thanks go to Peter Aronsson for diverse administrative arrangements and his effort for making me feel here in Sweden like at home. To-day I am aware that without his help I would have probably never joined Linköpings universitet.

I would like as well to thank all members of PELAB, who create a stimulating environment, and in particular Jens Gustavsson, Andreas Borg, and John Wilander. A particular memory to Emma Larsdotter Nilsson who unfortunately passed away too early. Special thanks go to Levon Saldamli for relevant discussions concerning C++ issues but, also as a friend, for making my spare time enjoyable. Further, I am also thankful to Bodil Mattsson Kihlström, our secretary, who makes not only my stay at the university easier, but also of all other members of PELAB. A great thank to Jon Edvardsson, Tobias Ritzau, and Damien Wyart for tremendous help with Latex and motivating discussions. I am grateful to Mikhail Chalabine for helping me with the thesis cover and to Mattias Eriksson for proofreading the thesis. A thank to professor Petru Eles and Alexandru Andrei from Embedded Systems Laboratory (ESLAB) of Linköpings universitet for providing us access to CPLEX installation.

I would like to give credits to my master students, without whom this work would probably never progress so far. Special thanks go to Anders Edquist who provided me with relevant feed back and contributed significantly in the

iv Acknowledgments

implementation and improvement of the project. The credits for writing ARM specifications and improving xADML specifications go to David LANDÉN. A thank to Yuan Yongyi for providing me with the Motorola MC56K specifications. Further, I would like to thank Andreas Rehnströmer who implemented the first version of the graphical tool for writing xADML specifications.

Also a thank goes to administrative staff at IDA, in particular Lillemor WALLGREN and Britt-Inger KARLSSON.

Finally I would like to thank my friends and my family who encouraged me during these long years of expatriation. I also would like to thank Mingmin whom I love tenderly.

Andrzej Bednarski Linköping, May 2006

## **Contents**

| Ab | tract                                                         |   | i   |

|----|---------------------------------------------------------------|---|-----|

| Ac | nowledgments                                                  |   | iii |

| 1. | Introduction                                                  |   | 1   |

|    | 1.1. Introduction to Compilation and Code Generation for DSP  |   | 1   |

|    | 1.2. Compilation Process                                      |   | 3   |

|    | 1.3. Motivations                                              |   | 4   |

|    | 1.4. Research Interest                                        |   | 6   |

|    | 1.5. Contributions                                            |   | 7   |

|    | 1.6. Origin of the Chapters                                   |   | 8   |

|    | 1.7. Organization of the Thesis                               |   | 8   |

| 2. | Introduction to Code Generation for Digital Signal Processors | 1 | 11  |

|    | 2.1. Motivations                                              | 1 | 11  |

|    | 2.2. Main Tasks of Code Generation                            |   | 12  |

|    | 2.2.1. Instruction Selection                                  | 1 | 12  |

|    | 2.2.2. Instruction Scheduling                                 | 1 | 13  |

|    | 2.2.3. Register Allocation                                    | 1 | 13  |

|    | 2.2.4. Partitioning                                           |   | 14  |

|    | 2.3. Optimization Problems in Code Generation                 | 1 | 14  |

|    | 2.3.1. Code Generation Techniques                             |   | 15  |

|    | 2.4. Phase Ordering Problem                                   | 1 | 16  |

|    | 2.5. Integrated Approaches                                    | 1 | 18  |

|    | 2.6. DSP Challenges                                           |   | 19  |

|    | 2.7. Need for Integrated Code Generation                      |   | 21  |

|    | 2.8. Retargetable Code Generation                             | 2 | 22  |

| 3. | Prerequisites                                                 | 2 | 25  |

|    | 3.1. Notations                                                | 2 | 25  |

|    | 3.2 Modeling the Target Processor                             | 2 | 25  |

vi

|    | 3.3.  | Terminology                                                | 27 |

|----|-------|------------------------------------------------------------|----|

|    |       | 3.3.1. IR-level scheduling                                 | 27 |

|    |       | 3.3.2. Instruction selection                               | 27 |

|    |       | 3.3.3. Target-level scheduling                             | 29 |

|    | 3.4.  | Classes of Schedules                                       | 30 |

|    |       | 3.4.1. Greedy Schedules                                    | 30 |

|    |       | 3.4.2. Strongly Linearizable Schedules and In-order        |    |

|    |       | Compaction                                                 | 30 |

|    |       | 3.4.3. Weakly Linearizable Schedules                       | 32 |

|    |       | 3.4.4. Non-linearizable Schedules                          | 32 |

|    | 3.5.  | Advanced Code Obtained by Superoptimization                | 33 |

|    | 3.6.  | Register allocation                                        | 33 |

| 4. | Integ | rated Optimal Code Generation Using Dynamic Programming    | 35 |

|    |       | Overview of our Approach                                   | 35 |

|    | 4.2.  | Main Approach to Optimal Integrated Code Generation        | 36 |

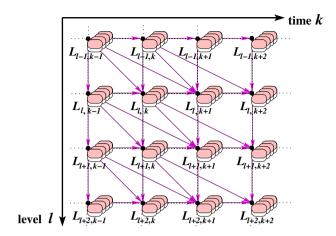

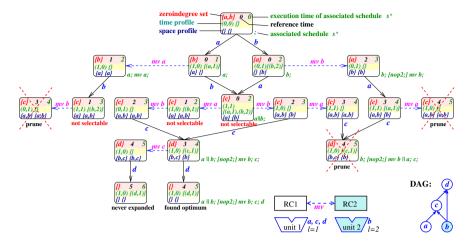

|    |       | 4.2.1. Interleaved Exhaustive Enumeration Algorithm        | 36 |

|    |       | 4.2.2. Comparability of Target Schedules                   | 39 |

|    |       | 4.2.3. Comparability I                                     | 40 |

|    |       | 4.2.4. Comparability II, Time Profiles                     | 41 |

|    |       | 4.2.5. Comparability III, Space Profiles                   | 47 |

|    | 4.3.  | Improvement of the Dynamic Programming Algorithms          | 53 |

|    |       | 4.3.1. Structuring of the Solution Space                   | 53 |

|    |       | 4.3.2. Changed Order of Construction and Early Termination | 54 |

|    |       | 4.3.3. Putting the Pieces Together: Time-optimal Code Gen- |    |

|    |       | eration for Clustered VLIW Architectures                   | 55 |

|    |       | 4.3.4. Example                                             | 58 |

|    |       | 4.3.5. Heuristic Pruning of the Solution Space             | 59 |

|    |       | 4.3.6. Beyond the Basic Block Scope                        | 60 |

|    | 4.4.  | Implementation and Evaluation                              | 61 |

| 5. | Ener  | gy Aware Code Generation                                   | 67 |

|    | 5.1.  | Introduction to Energy Aware Code Generation               | 67 |

|    | 5.2.  | Power Model                                                | 70 |

|    | 5.3.  | Energy-optimal Integrated Code Generation                  | 71 |

|    | 5.4.  | Power Profiles                                             | 71 |

|    | 5.5.  |                                                            | 72 |

|    | 5.6.  | Heuristics for Large Problem Instances                     | 74 |

|    | 5.7.  | Possible Extensions                                        | 76 |

|    | 5.8.  | Related Work                                               | 76 |

Contents

| 6. | •     |        | DAG Symmetries                                       |   | 79  |

|----|-------|--------|------------------------------------------------------|---|-----|

|    | 6.1.  | Motiv  | ation                                                | • | 79  |

|    | 6.2.  |        | on Space Reduction                                   |   | 81  |

|    |       | 6.2.1. | Exploiting the Partial-symmetry Property             |   | 81  |

|    |       | 6.2.2. | 1                                                    | • | 83  |

|    |       | 6.2.3. | 1 1                                                  | • | 83  |

|    |       | 6.2.4. | 1                                                    |   | 83  |

|    |       | 6.2.5. | Improved Dynamic Programming Algorithm               |   | 85  |

|    | 6.3.  | Imple  | mentation and Results                                | • | 86  |

| 7. | Integ |        | ar Programming Formulation                           |   | 91  |

|    | 7.1.  |        | luction                                              |   | 91  |

|    | 7.2.  | The II | LP Formulation                                       |   | 92  |

|    |       | 7.2.1. | Notations                                            |   | 93  |

|    |       | 7.2.2. |                                                      |   | 93  |

|    |       | 7.2.3. | Parameters to the ILP Model                          |   | 94  |

|    |       | 7.2.4. | Instruction Selection                                |   | 95  |

|    |       | 7.2.5. | Register Allocation                                  |   | 97  |

|    |       | 7.2.6. | Instruction Scheduling                               |   | 98  |

|    |       | 7.2.7. | Resource Allocation                                  |   | 99  |

|    |       | 7.2.8. | Optimization Goal                                    |   | 100 |

|    | 7.3.  | Exper  | imental Results                                      |   | 100 |

|    |       | 7.3.1. | Target Architectures                                 |   | 101 |

|    |       | 7.3.2. | Experimental Setup                                   |   |     |

|    |       | 7.3.3. | Results                                              |   |     |

| 8. | xAD   | ML: An | Architecture Specification Language                  |   | 107 |

|    | 8.1.  |        | ation                                                |   | 107 |

|    | 8.2.  |        | 10ns                                                 |   |     |

|    | 8.3.  |        | ML: Language Specifications                          |   |     |

|    | 8.4.  |        | ware Resources                                       |   |     |

|    |       | 8.4.1. |                                                      |   |     |

|    |       | 8.4.2. | Registers                                            |   |     |

|    |       | 8.4.3. | Residences                                           |   |     |

|    |       | 8.4.4. | Resources                                            |   |     |

|    | 8.5.  | Patter |                                                      |   |     |

|    | 8.6.  |        | ction Set                                            |   |     |

|    | 0.0.  | 8.6.1. |                                                      |   |     |

|    |       | 8.6.2. | Pattern Mapping                                      |   |     |

|    |       | 8.6.3. | Shared Constructs of Instruction and Pattern Nodes . |   |     |

|    |       | 8.6.4. | Data Dependence Edges                                |   |     |

viii

|     | 8.7.<br>8.8.<br>8.9. | Transfer Instructions                               | <ul><li>22</li><li>23</li><li>23</li><li>23</li></ul> |  |  |

|-----|----------------------|-----------------------------------------------------|-------------------------------------------------------|--|--|

| 9.  | Relat                | ed Work                                             | 29                                                    |  |  |

| ٠.  |                      | Decoupled Approaches                                |                                                       |  |  |

|     | ,                    | 9.1.1. Optimal Solutions                            |                                                       |  |  |

|     |                      | 9.1.2. Heuristic Solutions                          |                                                       |  |  |

|     | 9.2.                 | Integrated Code Generation                          |                                                       |  |  |

|     |                      | 9.2.1. Heuristic Methods                            |                                                       |  |  |

|     |                      | 9.2.2. Optimal Methods                              |                                                       |  |  |

|     | 9.3.                 | Similar Solutions                                   |                                                       |  |  |

|     |                      | 9.3.1. Aviv Framework                               | 32                                                    |  |  |

|     |                      | 9.3.2. Chess                                        | 35                                                    |  |  |

| 10. | Poss                 | ble Extensions 1                                    | 37                                                    |  |  |

|     | 10.1.                | Residence Classes                                   | 37                                                    |  |  |

|     | 10.2.                | xADML Extension                                     | 37                                                    |  |  |

|     |                      | 10.2.1. Parallelization of the                      |                                                       |  |  |

|     |                      | Dynamic Programming Algorithms                      |                                                       |  |  |

|     |                      | Global Code Generation                              |                                                       |  |  |

|     |                      | Software Pipelining                                 |                                                       |  |  |

|     |                      | DAG Characterization                                |                                                       |  |  |

|     |                      | ILP Model Extensions                                |                                                       |  |  |

|     | 10.7.                | Spilling                                            | 43                                                    |  |  |

| 11. | Cond                 | lusions 1                                           | 45                                                    |  |  |

| Α.  | Leas                 | :-cost Instruction Selection in DAGs is №P-complete | 47                                                    |  |  |

| В.  | AMP                  | L Code of ILP Model 1                               | 49                                                    |  |  |

|     |                      |                                                     |                                                       |  |  |

|     |                      |                                                     |                                                       |  |  |

| Ind | Index 1              |                                                     |                                                       |  |  |

## Chapter 1.

#### Introduction

This chapter is a general introduction to our research area, that is optimal code generation for irregular architectures. We define what an irregular architecture is and give a short introduction to compilation and code generation. Further, we motivate the interest of optimal code generation and summarize the contributions of our work.

## 1.1. Introduction to Compilation and Code Generation for DSP

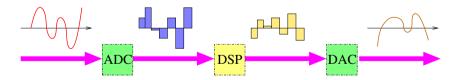

A Digital Signal Processor (DSP) is an integrated circuit whose main task is to process a digital input signal and produce an output signal. Usually the input signal is a sampled analog signal, for instance speech or temperature. An Analog-Digital Converter (ADC) transforms analog signals into a digital form, *i.e.* the input signal for a DSP. The output signal from the processor can be converted back to an analog signal with a Digital-Analog converter (DAC), or remain in digital form. Figure 1.1 depicts such a DSP system.

Today DSP systems represent a high volume of the electronic and embedded applications market that is still growing. Mobile phones, Portable Digital Assistants (PDAs), MP3 players, microwave-ovens, cars, air planes, etc. are

Figure 1.1.: Model of a DSP system.

only some examples equipped with a DSP system. Most embedded systems implement signal filters that are based on signal theory. Many filter computations are based on convolution:

$$x(n) = \sum_{i=0}^{n} x(i)\delta(n-i)$$

that involves the fundamental operation of Multiplication and Accumulation, for short MAC. Thus a MAC instruction is implemented in hardware on almost all classes of DSPs for efficiency purposes. The MAC instruction is an example of various hardware solutions to cope with high market requirements.

Manufacturers produce DSP processors with different technical solutions that meet computational requirements imposed by the market. As a consequence, processors exhibit more and more irregularities: specialized register sets, multiple memory banks, intricate data paths, *etc.* Thus, high requirements are achievable only if the code exploits DSP features and irregularities efficiently.

For regular architectures, currently available compiler techniques produce high quality code, but if applied to DSPs hand made code is hundreds of percent better [Leu00a]. This is because compiler techniques for standard processors are unable to efficiently exploit all available resources. Thus, for hot parts of the applications, DSP experts often write code directly in target assembly language and integrate it into automatically generated assembly code. Hand-coded parts of an application are generally of high quality but come with several drawbacks:

- High cost: it is due to the need of highly qualified staff and longer production time.

- Maintainability: it is difficult to update an application that is written partially in high level language, such as C, and in assembly language.

- Hardware update: if the platform is replaced all parts of the assembly code are likely to be totally rewritten. This is time consuming in terms of implementation and testing.

Moreover, high competition in electronics market increases the time to market demand drastically. Programmers are eager to write embedded applications in a high level language such as C instead of target depend assembly code and leave the optimization task to the compiler. There are numerous reasons for using the C language, mainly its popularity in industry for embedded

systems and its flexibility. However, some basic operators implemented in a DSP are of higher level than basic operators in C. For example, on most DSPs the following C statement a=b\*c+a; requires a single target instruction, called multiply and accumulate, noted MAC. To map such a statement to the MAC instruction the compiler needs to perform pattern matching on the intermediate code.

Additionally, retargetability of a tool is an issue for fast adaptation to new emerging hardware.

#### 1.2. Compilation Process

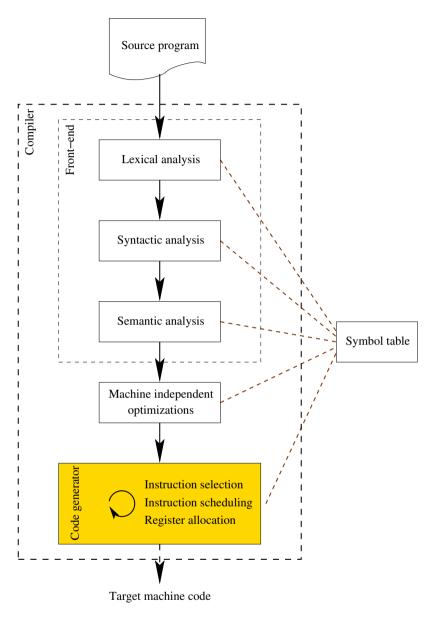

In general, a compiler is a software tool that translates programs written in a high level language into equivalent programs in object code or machine language that can be executed on a particular target architecture (could be a virtual machine as well). The compilation process inside a compiler consists of at least five steps [ASU86]:

- Lexical analysis takes as input character strings and divides them into tokens. Tokens are symbolic constants representing strings that constitute the vocabulary of the input language (e.g. "=", words, delimiters, separators, etc.). Lexical analysis produces error messages if the input character strings are incorrectly formed. The output of lexical analysis consists of a stream of tokens.

- Syntactic analysis, or parsing, processes the stream of tokens and forms a high level Intermediate Representation (IR) such as parse trees or abstract syntax trees. A tree is a data structure accessed by the top node, called root. Each node of a tree is either a leaf or an internal node that has one or more child nodes. A syntax tree is a compressed representation of a parse tree. An operator appears as an internal node of a tree, where its children represent operands.

- Semantic analysis takes as input a high level IR and verifies that the program satisfy semantic properties of the input language. Usually, after semantic analysis the IR is transformed to lower level, also known as intermediate code generation phase.

- Optimizations that are target independent such as dead code elimination, local and global subexpression elimination, loop unrolling, etc. are performed on a high and/or low level IR. The choice, order and level of

optimization depend on the overall optimization goal. Machine independent optimizations are considered as add-ons intended to improve code quality in various aspects.

Code generation transforms the low level IR, or the intermediate code into equivalent machine code. Besides the tasks of instruction selection, instruction scheduling, and register allocation, numerous machine dependent optimizations are performed inside the code generator.

A compiler includes additionally a *symbol table*, a data structure which records each identifier used in the source code and its various attributes (type, scope, *etc.*). The five tasks with the symbol table are summarized in Figure 1.2.

#### 1.3. Motivations

The first criterion of a compiler is to produce correct code, but often correct code is not sufficient. Users expect programs to use available hardware resources efficiently. The current state-of-the-art in writing highly optimized applications for irregular architectures offers two alternatives:

- Writing the applications directly in the assembly code for the specific hardware. Often, it is possible to automatically generate assembly code for those parts of the program that are not critical for the application, and only concentrate on the computationally expensive parts and write code for them by hand.

- Obtain highly optimized libraries from the hardware provider for a given target architecture. Then, the work consists in identifying parts of the application that may use a given library and call it. However, there are few companies that can spend sufficient effort in implementing highly optimized general purpose libraries, that are as well handwritten directly in the assembly language by experts. Designing a good library may be a difficult task, and it may work only for specific application areas.

With the solutions above it is possible to generate highly optimized code but at high cost in terms of man months. Further, the code needs to be rewritten almost completely if the underlying hardware changes, since the methods are rarely portable. In terms of software engineering, maintainability is difficult as long as there is no unified framework where third-party components can be updated more frequently than the application itself.

1.3. Motivations 5

Figure 1.2.: Global view of a compilation process for a specific target machine.

Within this work we aim at improving the current state-of-the-art in compiler generation for irregular architectures, where the user keeps writing applications in a high level language and the compiler produces highly optimized code that exploits hardware resources efficiently. We focus particularly on code generation and aim at producing an optimal code sequence for a given IR of an input program. Optimal code sequence is of particular interest for fixed applications where the requirements are difficult to meet, and often a dedicated hardware is required. Furthermore, from the hardware designer viewpoint, information about optimal code sequence may influence further design decisions.

Moreover, we consider the retargetability issue. The code generation framework should not encapsulate target hardware specific, but take the hardware description as input information together with the application specified in a high level language. From the hardware description it is either possible to generate a compiler (code generator generator), or parameterize an existing framework. A code generator generator is usually more difficult to build, thus in this thesis we implement a prototype of a parameterizable retargetable framework for irregular architectures.

#### 1.4. Research Interest

In the rest of this thesis by IR we mean a low level IR where data dependences are represented as a Directed Acyclic Graph (DAG). A DAG G = (V, E) is a graph whose edges  $e \in E$  are ordered pairs of nodes  $v \in V$  and there is no path that starts and ends at the same node. IR nodes correspond to operations (except for the leave nodes) and the children of a node are the operands. The graphical representation of the IR can be described in textual form by *three-address code*. Three-address code consists of an instruction with at most three operands. Such a representation is close to the assembly language. For instance for a binary operation a three-address code is shown below.

destination = operand1 operation operand2

In general, the compilation process does not work on the whole program or the whole function at once but on a set of smaller units called *basic blocks*. A basic block is a set of three-address codes (or IR statements) in which the flow of control enters only at the beginning and leaves only at the end. Each time the basic block is entered all the statements are executed exactly once.

Code generation research started at the time when the first computers appeared. Today it is known that for most hardware architectures and for IR

1.5. Contributions 7

dependence graphs that form DAGs, most important problems of optimal code generation are NP-hard.

Often, the quality of a compiler is evaluated using a set of benchmarks and compared either to figures obtained by another compiler on the same set of benchmarks or to hand optimized code. However, in both cases it is impossible to indicate how far from the optimal code the generated code sequence is because the optimum is not known. We do research aiming for a novel method for fully integrated code generation, that actually allows to produce optimal code for problem instances that could not be solved optimally with the state-of-the-art technology.

From a code generation point of view, a program is a directed graph, also called *Control Flow Graph* (CFG) whose nodes represent basic blocks. In this thesis, and as a first step, we focus on code generation on basic block level, *i.e.* local code generation. Generalization for global code generation is planned for future work.

Integration of several NP-hard problems into a single optimization pass increases considerably the complexity. We are aware that generating optimal code is not feasible for large problem instances, such as basic blocks with hundreds of instructions.

#### 1.5. Contributions

In this thesis we provide both a dynamic programming and an integer linear programming approach to retargetable, fully integrated optimal code generation that makes it possible to precisely evaluate a code generation technique. Further, we see other domains that can benefit from optimal code generation:

- The method is suitable for optimizing critical parts of a fixed (or DSP) application. Since the proposed optimization technique requires a large amount of time and space, it is intended only for the final code generation before shipping the code on the hardware.

- For hardware designers it is possible to evaluate an architecture during the design phase, and take decisions upon the resulting feedback. Thus, it is possible to modify a hardware, reevaluate an application and analyze the influence on code quality of such a modification.

As part of the discussion of future work in Chapter 10 we provide further possible extensions and contributions.

#### 1.6. Origin of the Chapters

KESSLER started considering the problem of optimal code generation in 1993 with different scheduling algorithms [Kes98, Keß00]. In year 2000, he joined Linköpings universitet and under his guidance we continued research on optimal code generation. A large part of the material in this thesis originates from the following publications:

- A. Bednarski and C. Kessler. Exploiting Symmetries for Optimal Integrated Code Generation. In *Proc. International Conference on Embedded Systems and Applications*, pages 83–89, June 2004.

- C. Kessler and A. Bednarski. Energy-Optimal Integrated VLIW Code Generation. In Michael Gerndt and Edmund Kereku, editors, *Proc. 11th Workshop on Compilers for Parallel Computers*, pages 227–238, July 2004.

- C. Kessler and A. Bednarski. Optimal integrated code generation for VLIW architectures. To appear in *Concurrency and Computation: Practice and Experience*, 2006.

- A. Bednarski and C. Kessler. Optimal Integrated VLIW Code Generation with Integer Linear Programming. Accepted for publication at Euro-Par 2006 Conference in Dresden, 2006.

#### 1.7. Organization of the Thesis

The rest of the thesis is organized as follows:

- Chapter 2 introduces the code generation problem and focuses on digital signal processor issues. In this chapter we motivate why, if searching for an optimal code sequence, we require an integrated approach.

- Chapter 3 provides the necessary notations and formalisms used in the rest of the thesis. Additionally, we provide a formal model of our target architecture.

- Chapter 4 provides the dynamic programming algorithm for determining a time-optimal schedule for regular and irregular architectures. In this chapter we also formally prove that the dynamic programming algorithm to find an optimal solution.

- Chapter 5 is an extension of our work in the area of energy aware code generation. Our method is generic and can be easily adapted to other domains where it is possible to define a monotonic cost function of the schedule length. The chapter presents a method for energy optimal integrated code generation (for generic VLIW processor architectures) based on an energy model from the literature.

- Chapter 6 presents an optimization technique that reduces time and space usage of the dynamic programming algorithm. We exploit a so-called partial-symmetry property of data dependence graphs that results in higher compression of the solution space.

- Chapter 7 provides an integer linear programming (ILP) formulation that fully integrates all phases of code generation as a single integer linear problem. The formulation is evaluated against the dynamic programming approach and we show the first results.

- Chapter 8 provides the specification of our structured hardware description language called *Extended Architecture Description Mark-up Language* (xADML), based on Extensible Mark-up Language (XML).

- Chapter 9 classifies related work in the area of decoupled and integrated code generation solutions.

- Chapter 10 gives different possible extensions of the thesis work.

- Chapter 11 concludes the thesis.

## Chapter 2.

# Introduction to Code Generation for Digital Signal Processors

In this chapter we introduce the code generation problem and concentrate more on digital signal processor (DSP) architectural issues. Additionally we motivate why we need an integrated approach when we are searching for an optimal code sequence. Further we provide related work in the area of integrated code generation.

#### 2.1. Motivations

The advances in the processing speed of current microprocessors are caused not only by progress in higher integration of silicon components, but also by exploiting an increasing degree of instruction-level parallelism in programs, technically realized in the form of deeper pipelines, more functional units, and a higher instruction dispatch rate. Generating efficient code for such processors is largely the job of the programmer or the compiler back-end. Even though most superscalar processors can, within a very narrow window of a few subsequent instructions in the code, analyze data dependences at runtime, reorder instructions, or rename registers internally, efficiency still depends on a suitable code sequence.

The high volume of the embedded processor market asks for high performance at low cost. Digital Signal Processors (DSPs) with a VLIW or clustered VLIW architecture became, in the last decade, the predominant platform for high-performance signal processing applications. In order to achieve high code quality, developers still write critical parts of DSP applications in assembly language. This is time consuming, and maintenance and updating are difficult. Traditional compiler optimizations developed for standard processors

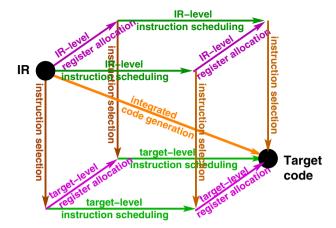

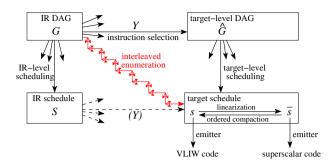

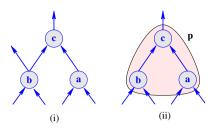

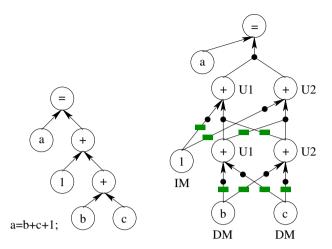

Figure 2.1.: The tasks of code generation as phase-decoupled or integrated problem. For clustered VLIW architectures, a fourth problem dimension (partitioning) could be added.

still produce poor code for DSPs [Leu00a]. and thus do not meet the requirements One reason for this is that the main tasks in code generation, such as instruction selection, instruction scheduling and register allocation, are usually solved in separate, subsequent phases in the compiler back-end, such that the interdependences between these phases, which are particularly strong for DSP architectures, are partially ignored. Hence, we consider the integration of these tasks into a single optimization problem.

#### 2.2. Main Tasks of Code Generation

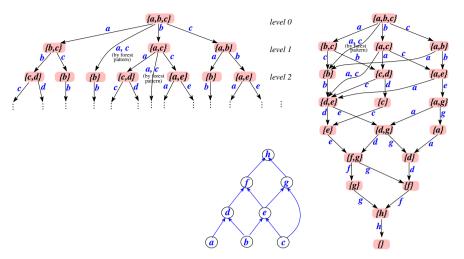

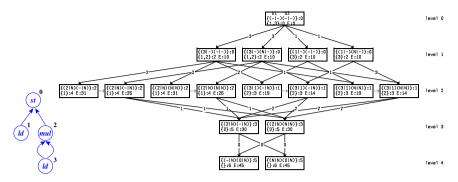

The task of generating target code from an intermediate program representation can be mainly decomposed into the interdependent subproblems of instruction selection, instruction scheduling, and register allocation. These subproblems span a three-dimensional problem space (see Figure 2.1). Phase-decoupled code generators proceed along the edges of the cube, while an integrated solution directly follows the diagonal, considering all subproblems simultaneously.

#### 2.2.1. Instruction Selection

Instruction selection maps the abstract operations given in an intermediate representation (IR) of the input program to machine-specific instructions of the

target processor, where our notion of an instruction also includes a specific addressing mode and a (type of) functional unit where it could be executed, if there are several options. For each instruction, one can specify its expected cost (in CPU cycles) and its semantics in terms of equivalent IR operations, where the latter is usually denoted in the form of a (tree) pattern. Hence, instruction selection amounts to a pattern matching problem with the goal of determining a minimum cost cover of the IR with machine instructions where cost usually denotes latency but also may involve register requirements, instruction size, or power consumption. For tree-structured IR formats and most target instruction sets, this problem can be solved efficiently. The dynamic programming algorithm proposed by Aho and Johnson [AJ76] gives a minimal-cost covering for trees in polynomial time for most target instruction sets.

But, for DAGs minimal-cost instruction selection is NP-complete [Pro98], see also Appendix A. There are several heuristic approaches that split the DAG into disjoint subtrees and apply tree pattern matching [EK91,PW96] on these.

#### 2.2.2. Instruction Scheduling

Instruction scheduling is the task of mapping each instruction of a program to a point (or set of points) of time when it is to be executed, such that constraints implied by data dependences and limited resource availability are preserved. For RISC and superscalar processors with dynamic instruction dispatch, it is sufficient if the schedule is given as a linear sequence of instructions, such that the information about the issue time and the functional unit can be inferred by simulating the dispatcher's behavior. The goal is usually to minimize the execution time while avoiding severe constraints on register allocation. Alternative goals for scheduling can be minimizing the number of registers (or temporary memory locations) used, or the energy consumed.

#### 2.2.3. Register Allocation

Register allocation maps each value in a program that should reside in a register, thus also called a *virtual register*, to a physical register in the target processor, such that no value is overwritten before its last use. If there are not enough registers available from the compiler's point of view, the live ranges of the virtual registers must be modified, either by:

• coalescing, that is, forcing multiple values to use the same register. Register coalescing identifies copy operations of values that do not interfere

with each other and are not overwritten after the copy. Then, the unnecessary copy is eliminated, and occurrences of the copied value are replaced with the original value.

• *spilling* the register, that is, storing the value of that register back to the memory and reloading it later, thus splitting the live range of value such that a different value can reside in that register in the meantime.

Even for superscalar processors, which usually expose quite many general-purpose registers to the programmer and internally may offer even more by hardware register renaming, spilling caused by careless use of registers should be avoided if possible, as generated spill code cannot be recognized as such and removed by the instruction dispatcher at runtime, even if there are internally enough free registers available. Also, spill code should be avoided especially for embedded processors because more memory accesses generally imply higher energy consumption. Finally, if less virtual registers are live across a function call, less registers must be saved to the stack, which results in less memory accesses, too. If the schedule is fixed and spilling cannot be avoided completely, the goal is to find a fastest instruction sequence that includes necessary spill code. Another strategy is to find a new schedule that uses less registers, possibly by accepting an increase in execution time.

#### 2.2.4. Partitioning

Partitioning of data and instructions across clusters becomes an issue for clustered VLIW architectures, where not every instruction can use every register as operand or destination register, due to restrictions implied by data paths or instruction set encoding. We group registers that exhibit equal constraints on addressability as operands in all instructions of a given instruction set into a register class (a formal definition will be given later). While we could even treat partitioning as a fourth problem dimension, the partitioning of data across register classes can be considered a part of the register allocation task, and the mapping of instructions to a unit in a specific cluster for execution can be included in the instruction selection problem.

#### 2.3. Optimization Problems in Code Generation

We refer to solving the problem of generating *time-optimal* code for a given program fragment, that is, code that needs a minimum number of clock cycles to execute, as *time optimization*. Likewise, by *space optimization*, we denote solving the problem of determining *space-optimal* code, that is, code that

needs a minimum number of registers (or temporary memory locations) for storing intermediate results without spilling. For non-pipelined single-issue architectures, this problem is also known as minimum register instruction sequencing (MRIS) problem. By adding an execution time deadline or a limit in the number of registers, we obtain constrained optimization problems such as time-constrained space optimization or space-constrained time optimization, respectively.

#### 2.3.1. Code Generation Techniques

During the last two decades there has been substantial progress in the development of new methods in code generation for scalar and instruction-level parallel processor architectures. New retargetable tools for instruction selection have appeared, such as IBURG [FHP92, FH95]. New methods for finegrain parallel loop scheduling have been developed, such as software pipelining [AN88, Lam88]. Global scheduling methods like trace scheduling [Fis81, Ell85], percolation scheduling [Nic84, EN89], or region scheduling [GS90] allow to move instructions across basic block boundaries. Also, techniques for speculative or predicated execution of conditional branches have been developed [HHG+95]. Finally, high-level global code optimization techniques based on data flow frameworks, such as code motion, have been described in [KRS98].

Most of the important optimization problems in code generation have been found to be NP-complete. Hence, these problems are generally solved by heuristics. Global register allocation is NP-complete, as it is isomorphic to coloring a live-range interference graph [CAC+81, Ers71] with a minimum number of colors. Time-optimal instruction scheduling for basic blocks is NP-complete for almost any nontrivial target architecture [AJU77, BRG89, HG83, MPSR95, PS93] except for certain combinations of very simple target processor architectures and tree-shaped dependency structures [BGS93, BG89,BJPR85,EGS95,Hu61,KPF95,MD94,PF91]. Space-optimal instruction scheduling for DAGs is NP-complete [BS76, Set75], except for tree-shaped [BGS93, SU70] or series-parallel [Güt81] dependency structures. Instruction selection for basic blocks with a DAG-shaped data dependency structure is assumed to be NP-complete, too, and the dynamic programming algorithm designed for (IR) trees can no longer guarantee optimality for DAGs, especially in the presence of non-homogeneous register sets [Ert99].

Optimal selection of spill candidates and optimal a-posteriori insertion of spill code for a given fixed instruction sequence and a given number of available registers is NP-complete even for basic blocks and has been solved by dynamic programming or integer linear programming for various special cases of

processor architecture and dependency structure [AG01, HKMW66, HFG89, MD99].

For the general case of DAG-structured dependences, various algorithms for time-optimal local instruction scheduling have been proposed, based on integer linear programming *e.g.* [GE92, Käs00a, WLH00, Zha96], branch-and-bound [CC95, HD98, YWL89], and constraint logic programming [BL99]. Dynamic programming has been used for time-optimal [Veg92] and space-optimal [Kes98] local instruction scheduling.

#### 2.4. Phase Ordering Problem

In most compilers, the subproblems of code generation are treated separately in subsequent *phases* of the compiler back-end. This is easier from a software engineering point of view, but often leads to suboptimal results because the strong interdependences between the subproblems are ignored. For instance, early instruction scheduling determines the live ranges for a subsequent register allocator; where the number of physical registers is not sufficient, spill code must be inserted a-posteriori into the existing schedule, which may compromise the schedule's quality. Also, coalescing of virtual registers is not an option in that case. Conversely, early register allocation introduces additional ("false") data dependences and thus constrains the subsequent instruction scheduling phase.

Example Let us illustrate the phase ordering problem by a simple example. We consider a pipelined single-issue architecture, *i.e.* only one instruction can be issued per clock cycle. Figure 2.2 shows a situation where performing register allocation prior to target instruction scheduling decreases the number of possible schedules by adding extra constraints, and thus may miss the optimal solution. Let us consider that the register allocator allocates values computed by instructions a, b and c to registers  $r_1$ ,  $r_2$ , and  $r_1$  respectively. We observe that instruction b needs to be computed before instruction c, since c overwrites the value of register  $r_1$  that is required for computing b. Therefore, this register assignment adds an extra dependence edge, the dashed edge in the figure, sometimes called "false" dependence that ensures that the content of  $r_1$  is not overwritten before its last use.

There is only one possible target schedule after register allocation that is compatible with such a register allocation, *i.e.* a, b, c. Now, if we suppose that the instruction c has a latency of two clock cycles, and instructions a and b take only one clock cycle, we obtain a schedule with a total execution time of four clock cycles. Consequently, if we are optimizing for the shortest

Figure 2.2.: Performing register allocation before instruction scheduling adds additional constraints to the partial order of instructions.

execution time, we miss the optimal schedule, *i.e.* a, c, b that computes the same result in three clock cycles, where b and c are overlapping in time.

Moreover, there are interdependences between instruction scheduling and instruction selection: In order to formulate instruction selection as a separate minimum-cost covering problem, phase-decoupled code generation assigns a fixed, context-independent cost to each instruction, such as its expected or worst-case execution time, while the actual cost also depends on interference with resource occupation and latency constraints of other instructions, which depends on the schedule. For instance, a potentially concurrent execution of two independent IR operations may be prohibited if instructions are selected that require the same resource.

**Example** An example, adapted from [NN95], illustrates the interdependence between the phases of instruction selection and instruction scheduling. Let us consider an architecture with three functional units: an adder, a multiplier, and a shifter. We assume a single-issue architecture. For the following integer computation,

$$b \leftarrow a \times 2$$

it is possible to choose three different target instructions: multiply, addition and left shift. Table 2.1 lists the three possibilities with their respective unit occupation time. We assume that, for this target architecture and this example each possible instruction runs on a different functional unit.

The code selection phase, if performed first, would choose the operation with the least occupation time. In our example, the left shift instruction would be selected, associating the shifter functional unit with the multiplication operation. However, in the subsequent scheduling phase it might be the case that the left shift instruction should be scheduled at time  $t_{i+1}$ , but the shift unit is already allocated for computing another operation at that time  $t_i$ , such as  $y = x \ll 3$  (see Figure 2.3). Figure 2.3 illustrates that the choice of using a left shift operation instead of addition produces final code that takes one clock

| Operation                    | Func. unit          | Unit occupation      |

|------------------------------|---------------------|----------------------|

| add(b, a, a)<br>mul(b, a, 2) | adder<br>multiplier | 4 cycles<br>5 cycles |

| lshift(b, a, 1)              | shifter             | 3 cycles             |

Table 2.1.: Possible operations to perform the integer computation  $b \leftarrow a \times 2$ , with their occupation time in clock cycles.

cycle longer, although the adder requires one additional occupation clock cycle. Figure 2.3 (a) shows the resulting unit occupation schema if the shifter unit performs the integer multiplication; Figure 2.3 (b) illustrates the schedule if using the adder unit instead, which is shorter by one clock cycle.

| $t_i$ :     | lshift(y, x, 3) | $t_i$ :     | lshift(y, x, 3) |

|-------------|-----------------|-------------|-----------------|

| $t_{i+1}$ : | NOP             | $t_{i+1}$ : | add(b, a, a)    |

| $t_{i+2}$ : | NOP             | $t_{i+2}$ : | NOP             |

| $t_{i+3}$ : | lshift(b, a, 1) | $t_{i+3}$ : | NOP             |

| $t_{i+4}$ : | NOP             | $t_{i+4}$ : | NOP             |

| $t_{i+5}$ : | NOP             |             |                 |

|             |                 |             |                 |

(a) Using the shifter

(b) Using the adder

Figure 2.3.: Here, using an adder results in a shorter execution time than using a shifter.

Furthermore, on clustered VLIW processors, concurrent execution may be possible only if the operands reside in the right register sets, which is an issue of register allocation. Especially for DSP processors where data paths and instruction word encodings are optimized for a certain class of applications, such interdependences can be quite involved. Hence, the integration of these subproblems and solving them as a single optimization problem is a highly desirable goal, but unfortunately this increases the overall complexity of code generation considerably.

#### 2.5. Integrated Approaches

There exist several heuristic approaches that aim at a better integration of instruction scheduling and register allocation [BSBC95, FR92, GH88, KG92].

For the case of clustered VLIW processors, the heuristic algorithm proposed by Kailas *et al.* [KAE01] integrates cluster assignment, register allocation, and instruction scheduling; heuristic methods that integrate instruction scheduling and cluster assignment were proposed by Özer *et al.* [OBC98], Leupers [Leu00b] and by Nagpal and Srikant [NS04].

Nevertheless, the user is, in some cases, willing to afford spending a significant amount of time in optimizing the code, such as in the final compilation of time-critical parts in application programs for DSPs. However, there are only a few approaches that have the potential—given sufficient time and space resources—to compute an optimal solution to an integrated problem formulation, mostly combining local scheduling and register allocation [BL99, Käs00a, Leu97]. Some of these approaches are also able to partially integrate instruction selection problems, even though for rather restricted machine models. For instance, WILSON et al. [WGHB94] consider architectures with a single, non-pipelined ALU, two non-pipelined parallel load/store/move units, and a homogeneous set of general-purpose registers. ARAUJO and MALIK [AM95] consider integrated code generation for expression trees with a machine model where the capacity of each sort of memory resource (register classes or memory blocks) is either one or infinity, a class that includes, for instance, the TI C25. The integrated method adopted in the retargetable framework Aviv [HD98] for clustered VLIW architectures builds an extended data flow graph representation of the basic block that explicitly represents all alternatives for implementation; then, a branch-and-bound heuristic selects an alternative among all representations that is optimized for code size.

Most of these approaches are based on integer linear programming, which is again a NP-complete problem and can be solved optimally only for rather small problem instances. Otherwise, integration must be abandoned and/or approximations and simplifications must be performed to obtain feasible optimization times, but then the method gives no guarantee how far away the reported solution is from the optimum. Admittedly, ILP is a very general tool for solving scheduling problems that allows to model certain architectural constraints in a flexible way, which enhances the scope of retargetability of the system. ILP has also been used for several other integrated approaches, by WILSON [MG95], LEUPERS [Leu97], and GOVINDARAJAN et al. [GYZ<sup>+</sup>99].

#### 2.6. DSP Challenges

High performance requirements push DSP manufactures to build more and more irregular processors. A typical irregular feature consists in dedicated register sets, also called special purpose registers. Thus an instruction can only be executed if the operands reside in special registers and/or it writes the result in another specific register or register set. In some DSPs dedicated register sets are context dependent.

Additionally, to increase data bandwidth, manufacturers of DSPs provide separate data memory banks and support for word-parallel execution.

Today there exists different techniques that improve the overall code quality without significant changes in the compiler. Here, we enumerate some of currently applied ad-hoc methods:

- Provide user directives to help the compiler to identify specific opportunities for code improvement.

- Allow direct access to the target specific instructions, i.e. allow the user

to manually write a part of the code directly in the assembly language of

the architecture to perform certain critical operations of the application.

Wagner and Leupers [WL01] provide access to the target processor

with so-called compiler-known functions, or compiler intrinsics. Compiler known-functions bring higher level abstraction provided by the

hardware into the programming language.

- Build ahead generic highly optimized libraries for most of the digital signal processing arithmetic operations. Thus, hardware providers do not only manufacture a processor, but additionally related libraries. Usually assembly and hardware experts write such libraries directly in assembly language.

On the one hand, the methods enumerated above considerably improve the final object code. But they are not portable and considerable time and effort must be spent in rewriting applications and libraries for a different hardware.

Further, contrary to general purpose processors, DSPs offer a reduced number of addressing modes. Often, an addressing mode offers the possibility of auto-decrementing or auto-incrementing an address. A restricted number of addressing modes may be practical if programmers write applications directly in assembly code, but it imposes on the compiler to carefully place data in memory to efficiently access them, since address arithmetic instructions are limited. Leupers [Leu00a] addresses the issue of offset assignment that consists in rearranging local variables in memory such that the address generation unit can access them efficiently with auto-increment and auto-decrement operations.

Summarizing, DSPs exhibit numerous irregularities and thus increase considerably the complexity of high quality code generation. Hence, producing highly optimized code for DSPs is a challenging task.

#### 2.7. Need for Integrated Code Generation

In Section 2.4 we mentioned the existence of dependences between different phases in a decoupled code generation. These interdependences are "stronger" for irregular architectures, that present intricate structural constraints. In order to produce optimal code it is necessary to combine the three main tasks of code generation into a single optimization phase. In phase decoupled code generators the code generation is illustrated as a path along the edges of the code generation cube (see Figure 2.1), while integrated solutions follow directly the diagonal of the cube from the IR to target code.

For IRs in form of directed acyclic graphs (DAGs) and most architectures, most subproblems of code generation are NP-hard (see Section 2.3.1). Considering them as a single problem leads to a complex and challenging optimization problem.

For instance, if we consider an architecture with general purpose registers (regular architecture) and an IR-level DAG with n nodes the number of all possible (sequences) IR-level schedules is less than n!, the number of permutations of the operations. Due to the data dependence constraints the number of schedules depends on the DAG structure and is usually less than the upper bound. Brute-force enumerating all possible schedules is feasible for small problem instances, with up to 15 instructions per basic block even if only space-optimization is considered [Kes98].

For irregular architectures, where accessible registers for a given instruction are context dependent, registers need to be carefully allocated. The location of operands may influence the possibility of concurrent execution of given instructions.

**Example** Let us consider two independent simple operations, an addition and a multiplication. For the Hitachi SH7729 SH3-DSP [Hit99], if the operands for addition are located in registers Y0 and Y1 and for the multiplication in X0 and A1 then both cannot be scheduled simultaneously. The registers of the destination also influence the possibility of parallelism, but we do not consider it in this example. Then, possible target schedules are:

```

t1: ADD YO, Y1, YO

t2: MUL XO, A1, XO

t2: ADD YO, Y1, YO

```

However, if the operands and result destinations are carefully chosen, then both operations can be executed simultaneously:

```

t1: ADD XO, X1, XO || MUL YO, Y1, YO

```

Figure 2.4.: In a dedicated compilation system, the compiler embeds the information of the target architecture.

This shows that the number of possible target schedules may be larger than the number of permutations of instructions. In the case of a fully integrated solution of the three problems, the complexity is even higher.

#### 2.8. Retargetable Code Generation

Writing compilers is generally time consuming, and consequently expensive. In the worst case, once the compiler is available it might turn out that the target hardware is already obsolete. Therefore, it is important, for a code generation system to be easily reconfigurable for different architectures, *i.e.* to be a retargetable code generation system.

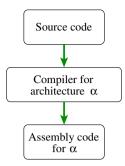

Generally, most compilation systems that come with a processor are dedicated compilers for that given architecture. However, in a design and development phase it is desirable to have a retargetable system. In Section 1.2 we described a classical view of a compiler that is a dedicated compiler for a specific hardware. Figure 2.4 illustrates a dedicated compiler for an architecture  $\alpha$ . In such designs the back-end is specific for a given architecture, but also it may not be clearly separated from the rest of the compiler, and often the hardware information is spread within the whole compiler. In order to produce code for a different hardware, say  $\beta$ , it is necessary to spend considerable time and effort in porting the existing  $\alpha$  compiler for  $\beta$  architecture.

Modular compiler toolkits, such as the compilation system CoSy [AAvS94], provide facilities to exchange compiler components, also called engines, and adapt the whole compilation system for a specific goal. Thus, if the target

Figure 2.5.: A retargetable compiler takes as input the program and the description of the hardware architecture.

processor changes, it is theoretically sufficient to replace the back-end (engine) of any previously constructed compiler. Modular compiler toolkits facilitate significantly the task of compiler construction, but it is still necessary to write back-ends for each type of target architecture.

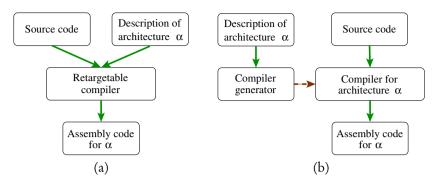

In contrast to dedicated code generation systems, retargetable compilers require additionally to the source program a description of the architecture for which to produce code (see Figure 2.5). Thus, to produce code for the  $\alpha$  hardware we need to provide the  $\alpha$  architecture description and the source program. This looks like an extra overhead compared to a dedicated compiler, but considerably facilitates the migration to some other hardware  $\beta$ , where it is only required to modify the hardware specifications. Figure 2.5 represents two variants of retargetable compilers: (a) parameterized, or dynamically retargetable such as GCC [FSF06] or OPTIMIST [KB05], and (b) generated, or statically retargetable (e.g. IBURG).

A retargetable code-generator generator is a framework that takes the hardware description as input and produces a compiler for the specified hardware. OLIVE [BDB90] and IBURG [FHP92] are examples of a retargetable codegenerator generator tool. Code-generator generators are generally more complex to write than dynamically retargetable frameworks.

Dynamically retargetable back-ends take the architecture description and the source code simultaneously. A well known example is the GCC C compiler that includes descriptions for several processor architectures.

# Chapter 3.

# **Prerequisites**

In this chapter we introduce necessary terminology for integrated optimal code generation that we use in the rest of the thesis. Further, we give the generic model of our target architectures.

#### 3.1. Notations

In the following, we focus on code generation for basic blocks where the data dependences among the IR operations form a directed acyclic graph (DAG) G = (V, E). Let n denote the number of IR nodes in the DAG. An extension to extended basic blocks [Muc97] will be given in Section 4.3.6. For brevity, we often use the IR node names also to denote the values computed by them.

## 3.2. Modeling the Target Processor

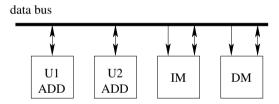

We assume that we are given an in-order issue superscalar or a VLIW processor with f *resources* U<sub>1</sub>,..., U<sub>f</sub>, which may be functional units or other limited resources such as internal buses.

The issue width  $\omega$  is the maximum number of instructions that may be issued in the same clock cycle. For a single-issue processor, we have  $\omega=1$ , while most superscalar processors and all VLIW architectures are multi-issue architectures, that is,  $\omega>1$ .

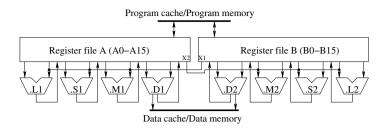

**Example** The DSP processor TI-C62x (see Figure 3.1) has eight functional units and is able to execute a maximum of eight instructions concurrently in every clock cycle, *i.e.*  $\omega = 8$ . The full issue width can only be exploited if each instruction uses a different functional unit.

Figure 3.1.: Texas TI-C62x family DSP processor (VLIW clustered architecture).

In order to model instruction issue explicitly, we provide  $\omega$  separate instruction issue units  $u_i$ ,  $1 \le i \le \omega$ , which can take up at most one instruction per time unit (clock cycle) each. For a VLIW processor, the contents of all  $u_i$  at any time corresponds directly to a (long) instruction word. In the case of a superscalar processor, it corresponds to the instructions issued at that time as resulting from the dynamic instruction dispatcher's interpretation of a given linear instruction stream.

Example The following instruction word for TI-C62x

consists of three instructions (multiplication, addition and subtraction) issued concurrently, as indicated by  $|\cdot|$ . Note that NOPs are implicit. The mapping to issue unit slots at time t is

|   | $\mathfrak{u}_1$ | $\mathfrak{u}_2$ | $\mathfrak{u}_3$ | $\mathfrak{u}_4$ | $\mathfrak{u}_5$ | $\mathfrak{u}_6$ | $u_7$ | $\mathfrak{u}_8$ |

|---|------------------|------------------|------------------|------------------|------------------|------------------|-------|------------------|

|   | L1               | <b>S</b> 1       | M1               | D1               | D2               | M2               | S2    | L2               |

| t | ADD              | NOP              | MPY              | NOP              | NOP              | NOP              | NOP   | SUB              |

where we use mnemonics for each entry.

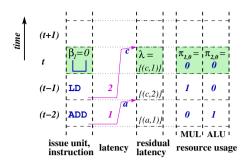

Beyond an issue unit time slot at the issue time, an instruction usually needs one or several resources, at issue time or later, for its execution. For each instruction y issued at time (clock cycle) t, the resources required for its execution at time t, t + 1, ... can be specified by a reservation table [DSTP75], a bit matrix  $o_y$  with  $o_y(i,j) = 1$  iff resource i is occupied by y at time t + j. Let  $O_i = \max_y \{j : o_y(i,j) = 1\}$  denote the latest occupation of resource i for any instruction. For simplicity, we assume that an issue unit is occupied for one time slot per instruction issued.

3.3. Terminology 27

An instruction y may produce a result, which may, for instance, be written to a register or a memory location. The number of clock cycles that pass from the issue time of y to the earliest possible issue time of an instruction that can use this result is called the *latency* of that instruction, denoted by  $\ell(y)$ . Hence, the result of instruction y issued at time t is available for instructions issued at time  $t + \ell(y)$  or later. We assume here that latency is always nonnegative. A more detailed modeling of latency behavior for VLIW processors is given *e.g.* by RAU *et al.* [RKA99].

# 3.3. Terminology

Our code generation methods are generally "driven" at the IR level because this gives us the possibility to consider multiple choices for instruction selection.

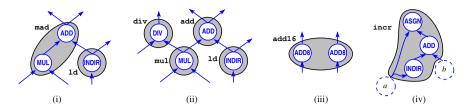

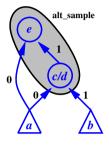

We call an IR *fine-grained* for a given instruction set I if the behavior of each instruction in I can be represented as tree/forest/DAG patterns (see Figure 3.2; a formal definition will be given later) covering one or several operations in the IR DAG completely. In other words, there is no "complex" IR operator whose functionality could be shared by two adjacent target instructions, and the boundaries between two adjacent covering patterns therefore always coincide with boundaries between IR operations.

From now on, let us assume that our IR is fine-grained. This assumption is realistic for low-level IRs in current compilers, such as L-WHIRL in ORC, or the LCC IR [FH95] that we use in our implementation.

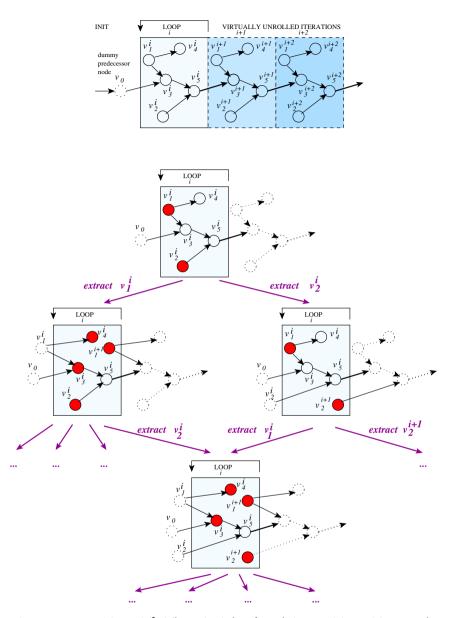

### 3.3.1. IR-level scheduling

An *IR schedule* of the basic block (IR DAG) is a bijective mapping  $S: V \rightarrow \{1, ..., n\}$  describing a linear sequence of the n IR operations in V that is compliant with the partial order defined by E, that is,  $(u, v) \in E \Rightarrow S(u) < S(v)$ . A partial IR schedule of G is an IR schedule of a subDAG of G. A subDAG  $G' = (V', E \cap (V' \times V'))$  of a DAG G is a subgraph induced by a subset  $V' \subseteq V$  of nodes where for each  $v' \in V'$  holds that all predecessors of v' in G are also in V'. A partial IR schedule of G can be extended to a (complete) IR schedule of G if it is prefixed to a schedule of the remaining DAG induced by V - V'.

#### 3.3.2. Instruction selection

Instruction selection is performed by applying graph pattern matching to the IR DAG. The user specifies one or several patterns for each target instruction;

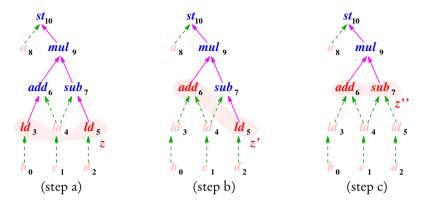

Figure 3.2.: Instruction selection by covering (a part of) an IR DAG by patterns, resulting in a target-level DAG. (i) A tree pattern for linked multiply-add (mad) matches the multiplication and the addition operation. (ii) mad does not match here because there is another operation (div) using the result of the multiplication operation. (iii) A forest pattern, describing a 16-bit SIMD-parallel addition of two 8-bit integers. (iv) A DAG pattern for incrementing a memory location with address a (common subexpression) by integer expression b.

a pattern is a small graph consisting of IR nodes and edges that describes the behavior of the instruction in terms of IR operations and data flow. The patterns may be trees, forests, or DAGs; some examples are given in Figure 3.2.

Covering a set  $\chi$  of IR DAG nodes with a pattern  $B_y$  for an instruction y implies that each DAG node  $v \in \chi$  is mapped one-to-one to a node  $B_y(v)$  in the pattern with the same operator, and all DAG edges (v,w) between nodes  $(v,w) \in \chi^2$  coincide with pattern edges  $(B_y(v),B_y(w))$  between the corresponding pattern nodes. There may be additional constraints, such as on values of constants, on type, size, and location of operands, *etc.* Moreover, for the most interesting case  $|\chi| > 1$ , we usually have the constraint that "interior" values  $v \in \chi$ , corresponding to the sources of DAG edges (v,w) covered by a pattern edge  $(B_y(v),B_y(w))$ , must not be referenced by edges (v,u) to DAG nodes  $u \notin \chi$ , because they will not be exposed by instruction y for use by other instructions selected for u.

An *instruction selection* Y for an IR DAG G = (V, E) and a given instruction set J is a surjective mapping  $V \to J$  such that each DAG node  $v \in V$  is covered exactly once in a pattern for an instruction  $y \in J$ . Moreover, for all DAG edges that are not covered by pattern edges and thus represent data flow between instructions, the type, size and storage of the source instruction's result must match the corresponding expectations for the target instruction's operand. By applying an instruction selection Y to a (IR) DAG G, we obtain a *target-level DAG*  $\hat{G}$  whose  $\hat{n}$  nodes correspond to target instructions and thereby to covered subsets  $\chi$  of IR DAG nodes, and whose edges are prece-

3.3. Terminology 29

dence constraints among target instructions and correspond to the IR DAG edges between covered node subsets.

Generally, there are several possible ways to cover each DAG node  $\nu$  and thus many possible instruction selections for a DAG G. In order to keep track of all alternatives, we denote by  $\Psi(\nu)$  the set of all instructions in  $\mathbb I$  such that  $\nu$  may be covered by a leaf node in a pattern for  $\mu$ . We will use  $\Psi$  in our algorithms to narrow the search space for matching instructions. It can be derived automatically by analyzing the patterns specified for the instructions in  $\mathbb I$ . Note that for IR trees, more general preprocessing methods for fast matching of tree patterns have been described in the literature, *e.g.* [HO82].

**Example** A common example in the DSP world consists in covering a multiplication and a dependent addition IR node with a single MAC (multiply and accumulate) instruction. Moreover, an integer multiplication of an operand by 2 is semantically equivalent to an integer addition of the operand with itself or to a left shift of the operand by 1. Thus, if an IR node  $\nu$  represents an integer multiplication, then  $\Psi(\nu) = \{\text{MUL}, \text{MAC}, \text{ADD}, \text{LSH}\}$  contains instructions for integer multiplication, multiply-add, addition, and left shift. Our framework will consider all alternatives, since they may imply different resource usage and latency behavior.

#### 3.3.3. Target-level scheduling