# Design and Implementation of a Module Generator for Low Power Multipliers

### **Kaihong Sun**

Reg nr: LiTH-ISY-EX-3315-2003

2003-09-25

# Design and Implementation of a Module Generator for Low Power Multipliers

#### **Master's Thesis**

Division of Electronics Systems Department of Electrical Engineering Linköping Institute of Technology Linköping University, Sweden

# By Kaihong Sun

Reg nr: LiTH-ISY-EX-3315-2003

Supervisor: Weidong Li

Examiner: Prof. Mark Vesterbacka

Linköping, September 25, 2003

#### Avdelning, Institution

Division, Department

Division of Electronics Systems,

Department of Electrical Engineering,

581 83 LINKÖPING

**Datum** Date

2003-09-25

#### **Språk** Language

Svenska/Swedish

X Engelska/English

#### Rapporttyp

Report category

Licentiatavhandling X Examensarbete

C-uppsats

D-uppsats

Övrig rapport

ISBN

ISRN LiTH-ISY-EX-3315-2003

**Serietitel och serienummer** Title of series, numbering

ISSN

#### URL för elektronisk version

http://www.ep.liu.se/exjobb/isy/2003/3315/

Titel

Title Design and Implementation of a Module Generator for Low Power Multipliers

Författare

Author Kaihong Sun

#### Sammanfattning

Abstract

Multiplication is an important part of real-time system applications. Various hardware parallel multipliers used in such applications have been proposed. However, when the operand sizes of the multipliers and the process technology need to be changed, the existing multipliers have to be redesigned.

From the point of library cell reuse, this master thesis work aims at developing a module generator for parallel multipliers with the help of software programs. This generator can be used to create the gate-level schematic for fixed point two's complement number multipliers. Based on the generated schematic, the entire multiplier can be implemented by small manual intervention. This feature can reduce the time of chip design.

The design phases consist of the logic, circuit and physical designs. The logic design includes gate-level schematic generation with C and SKILL programs and structural VHDL-code descriptions as well as validation. The circuit and physical design are custom in Cadence and the routing uses automatic place and route tools

To demonstrate the design method, an 18 by 18-bit modified Booth recoded multiplier was implemented in 0.18  $\mu m$  CMOS process with a supply voltage of 1.2 V and simulated using simulator (Spectre). The number of integrated transistors is 13000 and the active area is 85000  $\mu m^2$ . The postlayout simulation shows the critical path with a delay of 17 ns.

#### Nyckelord

Keyword

Modified Booth Encoding, Low Power, Multipliers, Module Generator.

#### **ABSTRACT**

Multiplication is an important part of real-time system applications. Various hardware parallel multipliers used in such applications have been proposed. However, when the operand sizes of the multipliers and the process technology need to be changed, the existing multipliers have to be redesigned.

From the point of library cell reuse, this master thesis work aims at developing a module generator for parallel multipliers with the help of software programs. This generator can be used to create the gate-level schematic for fixed point two's complement number multipliers. Based on the generated schematic, the entire multiplier can be implemented by minimizing manual intervention. This feature can reduce the time of chip design.

The design phases consist of the logic, circuit and physical designs. The logic design includes gate-level schematic generation with C and SKILL programs and structural VHDL-code descriptions as well as validation. The circuit and physical design are custom in Cadence and the routing uses automatic place and route tools.

To demonstrate the design method, an 18 by 18-bit modified Booth recoded multiplier was implemented in 0.18  $\mu m$  CMOS process with a supply voltage of 1.2 V and simulated using simulator (Spectre). The number of integrated transistors is 13000 and the active area is 85000  $\mu m^2$ . The post-layout simulation shows the critical path with a delay of 17 ns.

#### **ACKNOWLEDGMENTS**

First of all, I would like to thank my supervisor Weidong Li and examiner Professor Mark Vesterbacka for giving me the opportunity of this interesting work, especially Weidong Li for his support and guidance during this master thesis work. I also would like to acknowledge Emil Hjalmarson for his help and providing the useful material of Skill programmable language. Thanks also to the staff, Electronics systems at Linkoping University, for their support in many aspects.

I would sincerely grateful to my classmates, friends and many others for their support and invaluable help, not only during this master thesis work, but also during the past two years.

Finally, I would like to express my extreme gratitude to my wife Fengling and my son Lei for their encouragement and endless support in every aspect of my life.

| 1. | Introduction                          | 1  |

|----|---------------------------------------|----|

|    | 1.1 Purpose                           | 1  |

|    | 1.2 Design Specifications             | 1  |

|    | 1.3 Reading Guidelines                | 2  |

| 2. | Encoding Schemes                      | 5  |

|    | 2.1 Multiplication Process            | 5  |

|    | 2.2 Non-Booth Encoding.               | 6  |

|    | 2.3 Booth Encoding                    | 7  |

|    | 2.4 Modified Booth Encoding           | 8  |

|    | 2.5 Other Encoding                    | 11 |

|    | 2.6 Sign Extension schemes            | 12 |

|    | 2.6.1 Basic Concept of Sign Extension | 12 |

|    | 2.6.2 Conventional Sign Extension     | 14 |

|    | 2.6.3 Sign Generate Sign Extension    | 14 |

|    | 2.7 Summary                           | 16 |

| 3. | Power Reduction Techniques            | 17 |

|    | 3.1 Sources of Power Dissipation      | 17 |

|    | 3.2 Supply Voltage Scaling            | 18 |

|    | 3.3 Reducing Effective Capacitance    | 20 |

|    | 3.3.1 Physical Capacitance Reduction  | 20 |

|    | Effects of Circuit Styles             | 20 |

|    |                                       |    |

| Transistor sizing                             | 22 |

|-----------------------------------------------|----|

| 3.3.2 Switching Activity Reduction            | 22 |

| Minimizing Glitching Activity                 | 23 |

| 3.4 Summary                                   | 25 |

| 4. Multiplier Architecture                    | 27 |

| 4.1 Modified Booth Encoder                    | 28 |

| 4.2 Partial product Generator                 | 30 |

| 4.3 Wallace tree                              | 30 |

| 4.4 4-2 Compressors                           | 31 |

| 4.5 Vector Merging Adders                     | 33 |

| 4.5.1 Carry Look Ahead Adder                  | 33 |

| 4.5.2 Carry Skip Adder                        | 35 |

| 4.5.3 Carry Look Ahead with Bypass Adder      | 37 |

| 4.6 Partial Product Reduction Tree Topologies | 37 |

| 4.6.1 Regular Topologies                      | 38 |

| Array Structures                              | 38 |

| Tree Structures                               | 41 |

| 4.6.2 Irregular Topologies                    | 42 |

| 4.7 Summary                                   | 44 |

| 5. Implementation                             | 45 |

| 5.1 Architecture Selection                    | 45 |

| 5.2 Design Methodology                        | 46 |

| 5.3 Design Flow                               | 46 |

| 5.4 Logic Design                              | 48 |

| 5.4.1 Cell Models                         | 48 |

|-------------------------------------------|----|

| 5.4.2 Creating Schematic Generation Files | 48 |

| 5.4.3 Gate-level Schematic generation     | 49 |

| 5.4.4 Structural VHDL Generation          | 50 |

| 5.4.5 Structural VHDL-Code Validation     | 50 |

| 5.5 Circuit Design                        | 50 |

| 5.5.1 Custom versus Automatic Designs     | 51 |

| 5.5.2 Logic Style Considerations          | 51 |

| Static CMOS                               | 52 |

| Transmission Gate                         | 52 |

| Complementary Pass-Transistor Logic       | 53 |

| 5.5.3 Leaf Cell Design.                   | 54 |

| Design Environment                        | 55 |

| Transistor Sizing Criteria                | 55 |

| Layout Requirements                       | 56 |

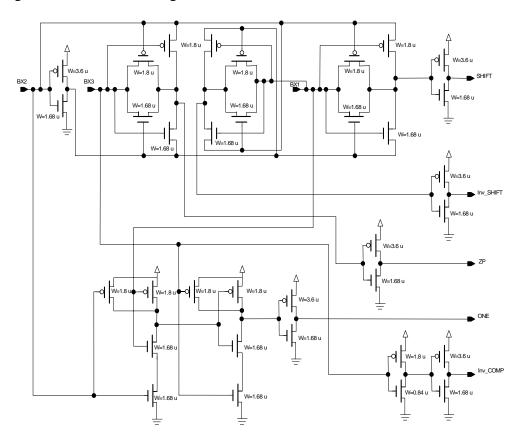

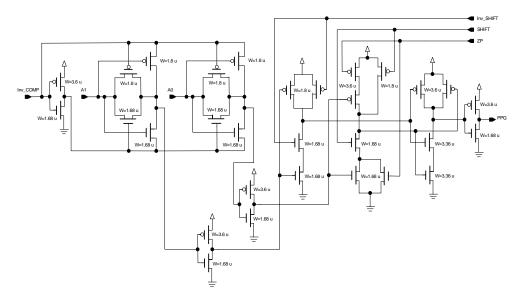

| Implementing MBE Encoder                  | 56 |

| Implementing One-Generator                | 60 |

| Implementing PP-Generator                 | 60 |

| Implementing Sign Generator               | 62 |

| Implementing Adder Cells                  | 63 |

| Implementing 4-2 Compressors              | 66 |

| Implementing the Vector-Merging Adders    | 68 |

| 5.5.4 Cell-level Schematic                | 71 |

| 5.6 Routing                               | 71 |

| 5.7 Simulation Strategy                   | 73 |

| 5.8 Summary                               | 74 |

| 6. | Conclusion                  | 77 |

|----|-----------------------------|----|

|    | 6.1 Conclusions.            | 77 |

|    | 6.2 Comments on the Project | 78 |

|    | 6.2 Future Improvements     | 78 |

| R  | EFERENCES                   | 80 |

# **List of Figures**

| Figure 2.1 Multiplication calculation by hand                          | 5  |

|------------------------------------------------------------------------|----|

| Figure 2.2 Multiplication operation in hardware                        | 6  |

| Figure 2.3 Booth encoding with negative multiplier                     | 8  |

| Figure 2.4 Partial product selections by using MBE                     | 10 |

| Figure 2.5 An example for an 8×8-bit MBE multiplier                    | 10 |

| Figure 2.6 An 8×8-bit multiplier based on smaller multipliers          | 12 |

| Figure 2.7 Partial product diagram with the sign generate scheme       | 16 |

| Figure 3.1 Power consumption for a 4-bit CLA as a function of $V_{dd}$ | 19 |

| Figure 3.2 Propagation delay versus $V_{dd}$ for a 4-bit CLA adder     | 19 |

| Figure 3.3 Power-delay product versus delay for an 8-bit adder         | 21 |

| Figure 3.4 Glitching behaviour for a 4-bit RCA                         | 23 |

| Figure 3.5 Tree versus chain structures                                | 24 |

| Figure 4.1 Architecture of the parallel multiplier                     | 27 |

| Figure 4.2 a) Glitch-free MB encoder, b) Partial Product Generator     | 28 |

| Figure 4.3 a) One generator, b) Truth table of the one generator       | 29 |

| Figure 4.4 16×16-bit modified Booth encoding                           | 29 |

| Figure 4.5 Wallace tree with 3-2 counters                              | 31 |

| Figure 4.6 4-2 compressor built with two 3-2 counters                  | 31 |

| Figure 4.7 An improved structure of the 4-2 compressor                 | 33 |

| Figure 4.8 Block diagram of the 4-bit CLA adder                        | 35 |

| Figure 4.9 Block diagram of a 16-bit carry skip adder                  | 36 |

| Figure 4.10 Propagation delay of the RCA versus CSKA                   | 36 |

| Figure 4.11 Block diagram of a 16-bit CLA with bypass adder            | 37 |

| Figure 4.12 4×4 ripple carry array multiplier                          | 39 |

|                                                                        |    |

## List of Figures

| Figure 4.13 Rectangular floorplan of $4 \times 4$ carry save multiplier | 39 |

|-------------------------------------------------------------------------|----|

| Figure 4.14 Array topology using 4-2 compressors                        | 40 |

| Figure 4.15 A binary tree topology with 4-2 compressors                 | 42 |

| Figure 4.16 A balanced delay tree topology using 3-2 counters           | 43 |

| Figure 5.1 Design flow                                                  | 47 |

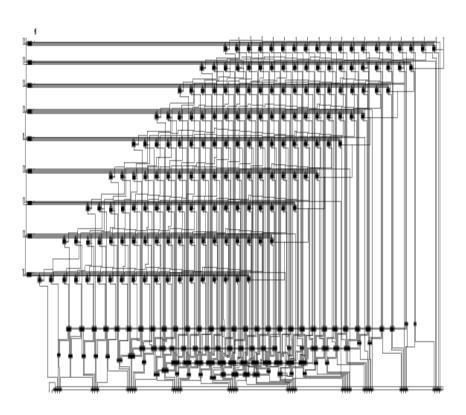

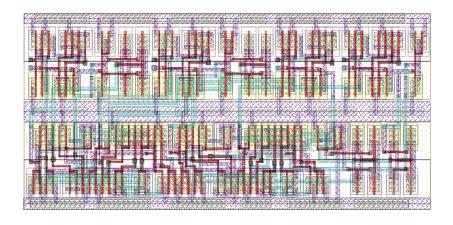

| Figure 5.2 Schematic for the 18×18-bit multiplier                       | 49 |

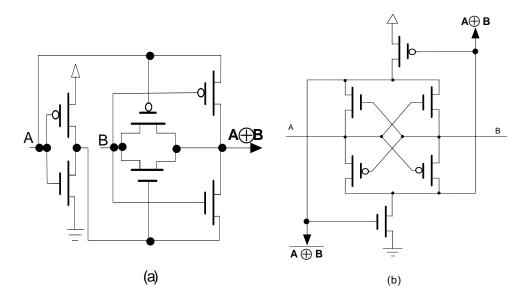

| Figure 5.3 Pass-transistor XOR/XNOR circuits                            | 53 |

| Figure 5.4 Typical complementary pass-transistor logic gates            | 54 |

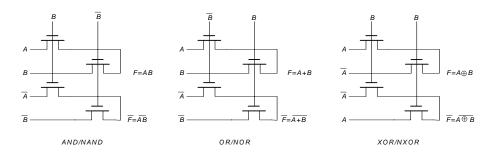

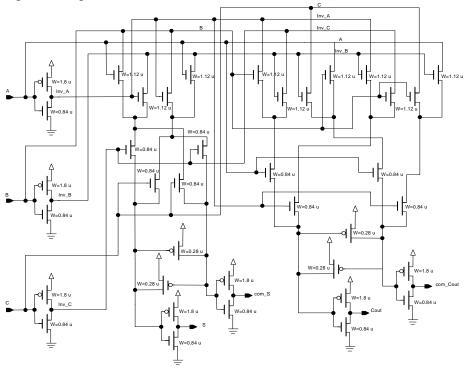

| Figure 5.5 Schematic of the MBE encoder                                 | 58 |

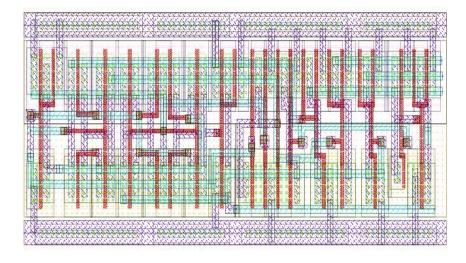

| Figure 5.6 Layout of the MBE encoder                                    | 59 |

| Figure 5.7 Schematic of the partial product generator                   | 61 |

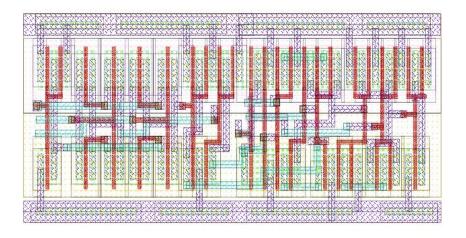

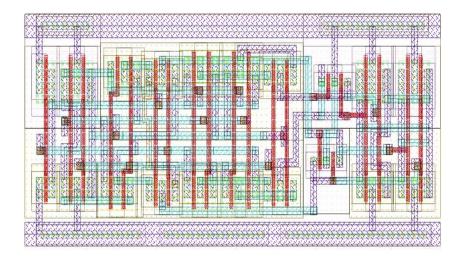

| Figure 5.8 Layout of the partial product generator                      | 61 |

| Figure 5.9 Logic functions and truth tables for the adder cells         | 64 |

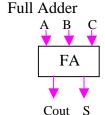

| Figure 5.10 Schematic of the full adder                                 | 65 |

| Figure 5.11 Layout of the full adder                                    | 66 |

| Figure 5.12 Schematic diagram of a 4-bit look-ahead adder               | 69 |

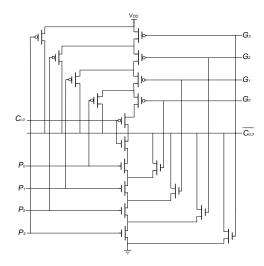

| Figure 5.13 Proposed schematic of the 4-bit CLA                         | 70 |

| Figure 5.14 Layout of the 4-bit CLA                                     | 69 |

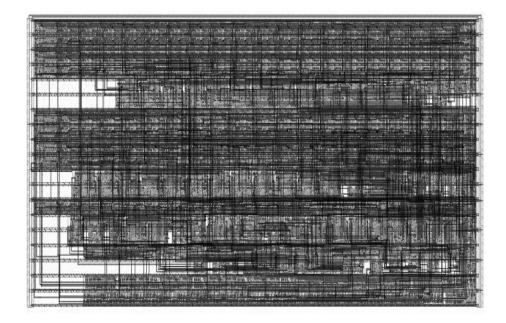

| Figure 5.15 Final layout of the 18×18-bit multiplier                    | 73 |

| Figure 5.16 Critical path for the 18×18 multiplier                      | 74 |

# List of Tables

# **List of Tables**

| Table 2.1 Modified Booth encoder truth table        | 9  |

|-----------------------------------------------------|----|

| Table 4.1 Truth table of the 4-2 compressor         | 32 |

| Table 5.1 Truth table of the modified Booth encoder | 57 |

| Table 5.2 Features for the adder cells              | 66 |

| Table 5.3 Features of the vector merging adders     | 71 |

### **Abbreviations**

BE Booth Encoding

CLA Carry Look Ahead

CPL Complementary Pass-transistor Logic

LSB Least Significant Bit

MBA Modified Booth Algorithm

MBE Modified Booth Encoding

Mcand Multiplicand

MSB Most Significant Bit

PP Partial Product

PPG Partial Product Generator

PPCT Partial Product Compression Tree

PPRT Partial Product Reduction Tree

PPSB Partial Product Sign Bit

Prod Product

RCA Ripple Carry Adder

TG Transmission Gate

VMA Vector Merging Adder

# **Chapter 1** Introduction

Low power high performance multipliers have become a basic building block in computations especially in digital signal processing. For most of the applications, multiplication operations take a significant part of time delay, area cost, and power consumption. Therefore, many techniques and design methodologies have been proposed to improve the speed and power dissipation of the multipliers. Most of the designs are targeted at a specific technology and require redesign for a new process technology. To speed up the chip design, a module generator for implementation of parallel multipliers with different sizes is presented in this thesis.

#### 1.1 Purpose

The aim with this thesis work is to develop a module generator for fixed-point parallel multipliers. The delay, area and power have also been taken into considerations. The multiplier should be able to multiply two n-bit two's complement numbers and produce a 2n-bit product. Using such a method, the basic library cells can be reused, which results in a less time of the chip designs. To demonstrate the design method, an 18 by 18 bit parallel multipliers is designed.

#### 1.2 Design Specifications

The design specifications for the parallel multiplier include the general requirements for designing the parallel multipliers and special requirements for implementing the 18 by 18 bit multiplier. Both of them are described as follows.

#### **General Requirements**

Multiplicand: n-bit two's complement number.

Multiplier: n-bit two's complement number.

Product: 2n-bit two's complement number.

Supply voltage: 1.2 V. Rise/fall time: 500 ps.

Target performance: Minimum area and power consumption under the

required delay.

#### **Special Requirements**

Multiplicand: 18-bit two's complement number.

Multiplier: 18-bit two's complement number.

Product: 36-bit two's complement number.

Supply voltage: 1.2 V. Rise/fall time: 500 ps.

Target performance: Minimum area and power consumption under the

operating frequency of 25.6 MHz.

In addition, the design and implementation should also satisfy the following further requirements.

- 1. The logic design and functional validation shall be performed in UNIX C and the Modelsim from Mentor Graphics for VHDL simulation.

- 2. The gate-level schematic shall be generated according to the required word-length.

- 3. All the transistor sizes shall be parameteriable.

- 4. The library for all the transistors in schematic view shall be analogLib and the DK\_hcmos8d for the layout.

- 5. The design and implementation shall be carried out in  $0.18 \mu m$  CMOS process technology.

#### 1.3 Reading guidelines

This thesis consists of six chapters. The rest of the chapters are organized as follows.

Chapter 2 gives an overview of the theoretical algorithms on parallel multipliers, such as encoding and sign extension schemes.

Chapter 3 briefly presents the power reduction techniques that are related to the design and implementation of parallel multipliers.

Chapter 4 contains the description of the overall architecture as well as the major functional units of the parallel multiplier. In addition, the partial product reduction tree topologies are also described in this section.

Chapter 5 focuses on the design of the module generator and the implementation of the 18 by 18 bit MBE multiplier. Three design phases, that is, logic, circuit and physical designs, have been represented in details.

Chapter 6 summarizes the results and comes to the conclusions from the master thesis work. Moreover, some suggestions on the future possible improvements are discussed in this chapter.

This page is left blank on purpose.

# **Chapter 2 Encoding Schemes**

This chapter briefly describes the methods for generating partial products. The major encoding schemes used for multipliers will be introduced, and their advantages and disadvantages will also be discussed. In order to introduce the concept of the encoding for the multiplication operation, let us start with an overview of the multiplication process.

#### 2.1 Multiplication Process

The simplest multiplication operation is to directly calculate the product of two numbers by hand. This procedure can be divided into three steps: partial product generation, partial product reduction and the final addition.

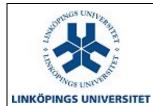

To further specify the operation process, let us calculate the product of two two's complement numbers, for example,  $1101_{\rm two}(-3_{\rm ten})$  and  $0101_{\rm two}(5_{\rm ten})$ , when computing the product by hand, which can be described according to figure 2.1.

Figure 2.1 Multiplication calculation by hand

The bold italic digits are the sign extension bits of the partial products. The first operand is called the multiplicand and the second the multiplier. The

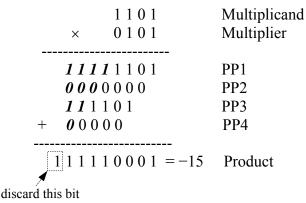

intermediate products are called partial products and the final result is called the product. However, the multiplication process, when this method is directly mapped to hardware, is shown in figure 2.2.

Figure 2.2 Multiplication operation in hardware

As can been seen in the figures, the multiplication operation in hardware consists of PP generation, PP reduction and final addition steps. The two rows before the product are called sum and carry bits. The operation of this method is to take one of the multiplier bits at a time from right to left, multiplying the multiplicand by the single bit of the multiplier and shifting the intermediate product one position to the left of the earlier intermediate products. All the bits of the partial products in each column are added to obtain two bits: sum and carry. Finally, the sum and carry bits in each column have to be summed.

Similarly, for the multiplication of an n-bit multiplicand and an m-bit multiplier, a product with n + m bits long and m partial products can be generated.

The method shown in figure 2.2 is also called a non-Booth encoding scheme. Its advantages and drawbacks will be discussed in next section.

#### 2.2 Non-Booth encoding

Using the non-Booth encoding method for partial product generation, the multiplier bits are examined sequentially starting from LSB to MSB. If the

multiplier bit is one, the partial product is simply the multiplicand. Otherwise, the partial product is zero. Each new partial product is shifted one bit position to the left. Each partial product can be produced by just using a row of two-input AND gates. The number of partial products generated equals the size of the multiplier bits.

The advantage of this method is that the partial product circuit is simple and easy to implement. Therefore, this scheme is suitable for the implementation of small multipliers.

The drawback is that the method is not able to efficiently handle the sign extension and it generates a number of partial products as many as the number of bits of the multiplier, which results in many adders needed so that the area and power consumption increase. This method is not applicable for large multipliers.

#### 2.3 Booth Encoding

The Booth encoding, or Booth algorithm, was proposed by Andrew D. Booth in 1951 [1]. This method can be used to multiply two two's complement number without the sign bit extension.

The operation of Booth encoding consists of two major steps [2]: the first one is to take one bit of the multiplier, and then to decide whether to add the multiplicand according to the current and previous bits of the multiplier. This encoding scheme is serial, which means that the different value of the 2 bits (current and previous bits) corresponds to the different operations. The serial encoding scheme is usually applied in serial multipliers. The operation procedure can be described with the following table.

00: no arithmetic operation.

01: adding the multiplicand to the left half of the product.

10: subtracting the multiplicand from the left half of the product.

11: no arithmetic operation.

The second step is to shift the product right one bit.

For example, let us consider the multiplication of two two's complement number  $0110_{\text{two}}(6_{\text{ten}})$  and  $1011_{\text{two}}(-5_{\text{ten}}) = 11100010_{\text{two}}(-30_{\text{ten}})$ . The operation is illustrated in Figure 2.3.

| Itera- | Multi-  |                                                           |                    |

|--------|---------|-----------------------------------------------------------|--------------------|

| Tion   | plicand | Step                                                      | Product            |

| 0      | 0110    | Initial values                                            | 0000 10110         |

|        | 0110    | $10 \Rightarrow \text{Prod} = \text{Prod} - \text{Mcand}$ | 1010 1011 0        |

| 1      | 0110    | Shift right product                                       | 1101 010           |

|        | 0110    | 11 => no operation                                        | 1101 0101 1        |

| 2      | 0110    | Shift right product                                       | 1110 10101         |

|        | 0110    | $01 \Rightarrow \text{Prod} = \text{Prod} + \text{Mcand}$ | 0100 1010 1        |

| 3      | 0110    | Shift right product                                       | 0010 01010         |

|        | 0110    | $10 \Rightarrow \text{Prod} = \text{Prod} - \text{Meand}$ | 1100 0101 0        |

| 4      | 0110    | Shift right product                                       | <b>1110 0010</b> 1 |

Note: The circled bits are used to determine the operation for the next step.

Figure 2.3 Booth encoding with negative multiplier

#### 2.4 Modified Booth Encoding

The modified Booth encoding (MBE), or modified Booth's algorithm (MBA), was proposed by O. L. Macsorley in 1961 [3]. The encoding method is widely used to generate the partial products for implementation of large parallel multipliers, which adopts the parallel encoding scheme. The basic principle for the modified Booth encoding can be described as follows.

Let us consider the multiplication of two fixed-point two's complement numbers, X and Y, where X is the multiplier and Y is the multiplicand, both of them have n bits, and the X can be expressed by

$$X = -X_{n-1}2^{n-1} + \sum_{i=0}^{i=n-2} X_i 2^i,$$

=

$$\sum_{i=0}^{i=n/2-1} (-2X_{2i+1} + X_{2i} + X_{2i-1}) \cdot 2^{2i},$$

$$= \sum_{i=0}^{i=n/2-1} d_i \cdot 2^{2i},$$

$$= \sum_{i=0}^{i=n/2-1} d_i \cdot 4^i$$

(2-1)

Using this notation, the multiplication of *X* and *Y* is given by

$$YX = \sum_{i=0}^{(n/2)-1} d_i \cdot 4^i \cdot Y,$$

$$= \sum_{i=0}^{(n/2)-1} P_i \cdot 4^i$$

(2-2)

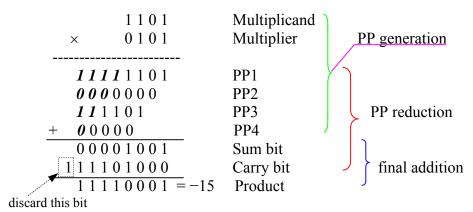

In this way, the bits of the multiplier are partitioned into sub-strings by the 3 adjacent bits and each sub-string group ( $X_{2i+1}, X_{2i}, X_{2i-1}$ ) corresponds to one of the value in the set  $\{-2, -1, 0, +1, +2\}[30]$ . This means that the each three adjacent bits of the multiplier can generate a single encoding digit, which is called the modified Booth recoding digit ( $d_i$ ) [5], as shown in table 2.1. Each MBE blocks can work in parallel, therefore, all the partial product bits are generated simultaneously. The parallel encoding scheme is suitable for parallel multipliers.

| Table 2.1 Wodffied Booth cheoder truth table |          |            |       |  |

|----------------------------------------------|----------|------------|-------|--|

| $X_{2i+1}$                                   | $X_{2i}$ | $X_{2i-1}$ | $d_i$ |  |

| 0                                            | 0        | 0          | 0     |  |

| 0                                            | 0        | 1          | +1    |  |

| 0                                            | 1        | 0          | +1    |  |

| 0                                            | 1        | 1          | +2    |  |

| 1                                            | 0        | 0          | -2    |  |

| 1                                            | 0        | 1          | -1    |  |

| 1                                            | 1        | 0          | -1    |  |

| 1                                            | 1        | 1          | 0     |  |

Table 2.1 Modified Booth encoder truth table

The number of bits for the multiplier, X, must be even. Otherwise, the sign bit of X should be extended. For the  $n \times m$  multiplication, using the modified Booth encoding m/2 partial products are produced or (m+1)/2 partial products if m is odd. Obviously, from the equation (2-2), the partial product,  $P_{i+1}$ , should be shifted two positions to the left of the partial product,  $P_i$ , due to the  $P_i$  is multiplied by  $4^i$ .

| $d_i$ | Operation on meand (Y)                         |  |

|-------|------------------------------------------------|--|

| 0     | $0*Y: 0 \Rightarrow \text{Prod}$               |  |

| +1    | +1*Y: mcand => Prod                            |  |

| +2    | +2*Y: one shift to the left for macnd = > Prod |  |

| -1    | -1*Y: inverted mcand & added 1 to the LSB      |  |

| -2    | -2*Y: one shift to the left for macnd, then    |  |

The operation for *Y* times *X* can be summarized in figure 2.4.

Figure 2.4 Partial product selections by using MBE

inverted mcand & added 1 to the LSB

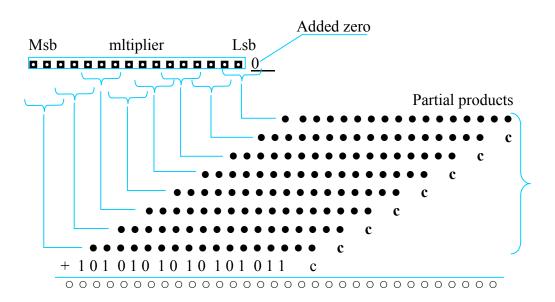

This operation can also be illustrated graphically. For example, an  $8 \times 8$  bit MBE multiplier with  $X = 10011101_{\text{two}}(-99_{\text{ten}}), Y = 01101101_{\text{two}}(109_{\text{ten}}), n = 8$ , is shown in figure 2.5. The binary numbers in parentheses are the generated sign bits of the partial products.

Figure 2.5 An example for an 8×8 bit MBE multiplier

The advantage of using MBE is that it can reduce the number of partial products by 50%, which results in about half of the adders reduced compared to the non-Booth encoding, and the consumed power is also decreased. This encoding method is applicable for parallel multipliers with the input operands of equal to or greater than 16-bit.

However, the modified Booth encoding is not suitable for implementing smaller multipliers due to the extra hardware overhead for MBE encoder and the complex circuit of the partial product generator.

#### 2.5 Other Encoding

Besides the non-Booth and Modified Booth encoding, higher radix Booth encoding such as radix-8 can be also used to generate partial products. Radix-8 Booth encoding method is also called the Booth 3 scheme [32]. Using the Booth 3 encoding scheme, the multiplier is divided into overlapping groups of 4 bits in parallel. Each partial product can be selected from the set of the multiplicand  $Y \{0, \pm Y, \pm 2Y, \pm 3Y, \pm 4Y\}$  [32].

The advantage of this encoding method is that it can further reduce the partial products to (n + 1)/3. But the drawback is obviously the complexity of the partial product selection logic and the Booth encoders as well as the generation of the  $\pm 3Y$  multiple. In this thesis work, this method will not be discussed in detail.

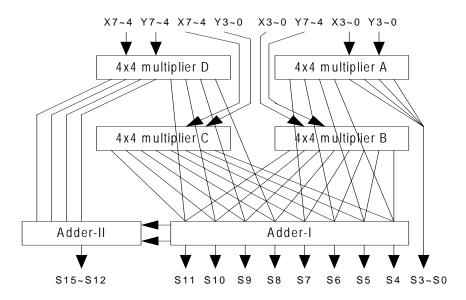

Another encoding scheme for generation of partial products is to use smaller multipliers. For instance, an  $8\times8$  bit multiplier can be constructed with four  $4\times4$  bit multipliers and two adders [4], as shown in Figure 2.6.

The non-Booth encoding scheme can be used to partition and distribute the two 8-bit numbers to the four 4×4 multipliers. The four 4×4 smaller multipliers could be implemented by non-Booth encoding method, and their partial product generator is simply two-input AND gates. The four 8-bit products produced can be added by using two adders.

In general, this encoding is not efficient compared to other encoding schemes implemented in current process technology [32].

Figure 2.6 An 8×8 bit multiplier based on smaller multipliers

#### 2.6 Sign Extension Schemes

The multiplication and addition operations for two's complement numbers have to handle the sign bits, as shown in figure 2.2. The addition of the extended sign bits for each partial product results in additional cost. To reduce the cost of the sign extension, several extension schemes have been proposed, as described in [28].

In the following section, the basic principle of sign extension and one method used for sign extension in this thesis will be introduced.

#### 2.6.1 Basic Concept of Sign Extension

The two's complement is a special case of radix complement for binary numbers in which the radix equals to two. For instance, a k+1 bit number A can be represented in two's complement as

$$A = -a_k \cdot 2^k + \sum_{i=0}^{k-1} a_i \cdot 2^i$$

(2-3)

where the  $a^k$  is the sign bit. A is positive when  $a^k$  equals to zero, while A is negative when  $a^k$  is 1.

If the sign bit of a two's complement number A is extended by S bits, then A should include three parts [29], the original MSB, the extension of the sign bit by S bits and the number's value. In this case, the A is rewritten by

$$A = -a_k \cdot 2^{k+S} + \sum_{i=k}^{k+S-1} a_k \cdot 2^i + \sum_{i=0}^{k-1} a_i \cdot 2^i$$

(2-4)

When defining  $A_{ext}$  as the sign bit plus the S extended bits, the  $A_{ext}$  can also be presented using two's complement format with a length of S+1 and bit significances from  $2^k$  to  $2^{k+S}$ . The  $A_{ext}$  can be expressed as

$$A_{ext} = -a_k \cdot 2^{k+S} + \sum_{i=k}^{k+S-1} a_k \cdot 2^i$$

$$= -a_k \cdot 2^{k+S} + a_k \cdot \sum_{i=k}^{k+S-1} 2^i$$

$$= a_k (-2^{k+S} + 2^{k+S} - 2^k)$$

$$= -a_k 2^k, \quad \text{with } \sum_{i=k}^{n-1} 2^i = 2^n - 2^k.$$

(2-5)

From the above derivation, it is clear that the sign for the number with sign extension is the same as the original one. Therefore, the positive two's complement numbers actually have an infinite number of 0s on the left, whereas the negative ones have an infinite number of 1s. In order to fit the width of the hardware, sign extension can be used to restore some of the hidden sign bits.

#### 2.6.2 Conventional Sign Extension

Conventional sign extension is similar to the method used to calculate the multiplication by hand [28]. This method can be used to add the partial products sequentially. This means that the first row of partial products is summed to second row and the result is added to third row and so on. In this way, sign extension is only performed from one row to the next. Furthermore, the sign is encoded into the carry and sum of the MSB of the intermediate addition results. Therefore, the carry and sum of MSB should be extended to the next row.

This method is not efficient for low power design since the full adder on the most significant position in each row has one more fan-out than the rest of the adders. Another efficient method that is called sign generate is described in the following section.

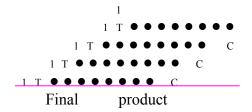

#### 2.6.3 Sign Generate Sign Extension

The sign generate scheme [5] is an efficient method to reduce the length of each partial product. This sign extension scheme assumes that all the partial products are negative. Based on such an assumption, for an n by m multiplier, the sum of all sign extensions can be precalculated as

$$Signs = \sum_{i=0}^{(m/2)-1} ((-1)2^{n})4^{i},$$

$$= 2^{n}(-1)(\frac{2^{m}-1}{3}).$$

(2-6)

The equation (2-6) shows the relationship that can be interpreted as a fixed number,  $(-1)[(2^m-1)/3]$ , which should be added to the  $N^{\text{th}}$  binary position of the partial product leftwards. This number expressed in binary form is equal to 1010101...01011, where there are exactly m/2-1 zeros. If the partial product generated is positive, its sign bit should be simply replace by a one to suppress the effect of the previous assumption. This technique can be summarized as follows.

- 1. Inverting the sign bit of each partial product, and placing it into the  $N^{th}$  binary position.

- 2. Adding one to the left of each partial product.

- 3. Adding one in  $N^{th}$  bit column.

The operation of the one addition can be implemented by using increment adders. Therefore, no extra adders for adding these constant 1s are required using this method. The advantage of the sign generate method is that it does not only reduce the area, power consumption, but also speed up the multiplication. The following example illustrates an 8 by 8 multiplier using this method together with the modified Booth encoding [28]. In this case, the sign of the final result can be expressed as

$$S = S_0 \sum_{i=8}^{15} 2^i + \left( S_1 \sum_{i=8}^{13} 2^i \right) 2^2 + \left( S_2 \sum_{i=8}^{11} 2^i \right) 2^4 + \left( S_3 \sum_{i=8}^{9} 2^i \right) 2^6$$

(2-7)

where  $S_i$  is the sign bit of the partial product in the  $i^{th}$  row. By using the following two equations

$$\sum_{i=j}^{n-1} 2^i = 2^n - 2^j \tag{2-8}$$

$$S_i = 1 - \overline{S_i} \tag{2-9}$$

then S becomes

$$S = \overline{S}_0 2^8 + \overline{S}_1 2^{10} + \overline{S}_2 2^{12} + \overline{S}_3 2^{14} + 2^9 + 2^{11} + 2^{13} + 2^{15} + 2^8.$$

(2-10)

Equation 2-10 indicates that the sign of the final result can be calculated directly according to the partial products. Figure 2-7 shows the partial product diagram with the sign generate method, in which T is the one's complement of the sign and C is the correction constant for the negative partial products. Another example is shown in figure 2.5.

Figure 2.7 Partial product diagram with the sign generate scheme

#### 2.7 Summary

The aim of this chapter was to give an overview of the methods for generating the partial products. It started with the introduction of the multiplication process. Several encoding schemes have been described and their advantages and drawbacks have also been discussed.

The Non-Booth encoding method generates the same number of partial products as the number of bits of the multiplier. It is suitable for implementing the smaller multipliers due to the simple realization of the partial product generator and no need to use an encoding circuit.

The original Booth encoding performs the encoding serially. The serial encoding scheme is usually employed in bit-serial multipliers.

The modified Booth encoding performs the encoding in parallel, which is widely used to generate the partial products of the large parallel multipliers. In general, this method is not applied to implement the multipliers with a word length less than 16 bits.

Higher radix Booth encoding also performs the encoding in parallel, which can further reduce the number of partial products, but it uses a more complex circuit for the Booth encoder.

A small multiplier can also be used to construct large multipliers. However, it is not an efficient method compared to other encoding schemes in current implementation technology.

# **Chapter 3 Power Reduction Techniques**

Reducing power consumption has become an important issue in digital circuit design, especially for high performance portable devices. Many power reduction techniques have also been proposed from the system level down to the circuit level. In this section, some of these techniques, which are related to the design for parallel multiplier, will be presented.

#### 3.1 Sources of power Dissipation

The sources of power dissipation in digital CMOS circuits are composed of the following parts: switching power, short-circuit power, and leakage power, which are expressed in the following equation

Dynamic Power Static Power

$$P_{total} = \alpha_{0-1} \cdot C_L \cdot V_{dd}^2 \cdot f_{clk} + I_{SC} \cdot V_{dd} + I_{leakage} \cdot V_{dd}$$

Switching power Short-circuit power Leakage Power

The first term stands for the switching power, which is the power required to charge/discharge the circuit nodes.  $\alpha_{0-1}$  is the node switching activity factor of the circuit, which is the average number of the node making a power consuming transition per clock cycle.  $C_L$  is the load capacitance,  $V_{dd}$  is the supply voltage, and  $f_{clk}$  is the clock frequency. The switching power consumption is the dominating component in digital circuits, and it can be reduced by minimizing any one or several of  $\alpha_{0-1}$ ,  $C_L$ ,  $V_{dd}$ , and  $f_{clk}$  under the required performance.

The second term in equation (3-1) represents the short-circuit power consumption due to short-circuit current. The short-circuit current in complementary CMOS circuit arises when both the pull-up network and the pull-down network are turned on at the same time during the transitions. The amount of  $I_{sc}$  is proportional to the rising and falling time of the input signals, transistor sizes and the output load capacitance [6]. Hence, the longer the transition time for the input signals, the larger the short-circuit current which results in more power consumed. The short-circuit power consumption can be lowered by optimal transistor sizing and input reordering transistors [7].

The total average short-circuit current can be minimized by designing with equal input and output edge times [8]. In this way, the power consumed by the short-circuit currents is less than 10% of the total dynamic power. In particular, when the supply voltage is lowered to be below the sum of the thresholds of the transistors, the short-circuit currents can be eliminated.

The third term in equation (3-1) refers to the leakage power dissipation due to the leakage current. Though one and only one of the pull-up and pull-down networks in a static CMOS circuit is conducting in steady state, there still is a small leakage current which flows through the reverse-biased diode junctions of the transistors between the diffusion regions and the substrate [9]. Another source of the leakage current is potentially the subthreshold current of the transistors. Both sources of leakage caused the static power dissipation which constitutes a small fraction of the overall power dissipation in current technologies. However, with the progress of the technology scaling, the subthreshold leakage currents will become a larger component in total power dissipation. The leakage current depends strongly on the technology, and it can be reduced by applying some techniques such as multithreshold voltage CMOS technology [10] etc.

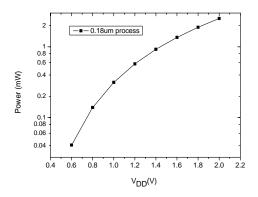

#### 3.2 Supply Voltage Scaling

The most effective method to reduce the power consumption is scaling the supply voltage, as indicated by equation (3-1). Reducing the supply voltage can significantly reduce the power dissipation that is a quadratic function of the operating voltage. This is illustrated in figure 3.1, which shows the

power consumption as a function of  $V_{\rm dd}$  for a 4-bit carry look-ahead adder in 0.18  $\mu$ m process technology. The power consumption dependence on supply voltage for various logic functions and logic styles has been described in [11].

Figure 3.1 Power consumption for a 4-bit CLA as a function of  $V_{dd}$

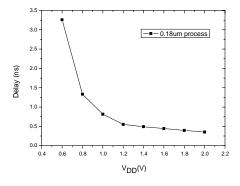

However, reducing the supply voltage also increases the delay. The relationship between  $V_{dd}$  and the delay,  $T_d$ , can be expressed [8] by

$$T_{d} = \frac{C_{L} \times V_{dd}}{I} = \frac{C_{L} \times V_{dd}}{\frac{\mu C_{ox}}{2} (W / L) (V_{dd} - V_{t})^{2}}$$

(3-2)

From the equation (3-2), when  $V_{dd}$  approaches the threshold voltage,  $V_t$ , the delay increases drastically, as shown in figure 3.2.

Figure 3.2 Propagation delay versus  $V_{dd}$  for a 4-bit CLA adder

Obviously, using this method causes the performance loss on the speed. In order to compensate for the loss in throughput at low supply voltages, several techniques can be applied such as parallel and pipelined architectures as well as modifying the threshold voltage of the devices [8].

### 3.3 Reducing Effective Capacitance

When the performance loss in throughput due to lowering the supply voltage is not acceptable, reducing the effective capacitance can also obtain low power consumption in CMOS circuits. The effective capacitance is defined by the product of the physical capacitance and the switching activity, which is shown as

$$C_{effective} = \alpha_{0-1} C_L$$

where  $\alpha_{0-1}$  is the node transition activity factor, and  $C_L$  is the load capacitance which refers to physical capacitance. The switching power consumption can be rewritten as

$$P_{switching} = C_{effective} V_{dd}^2 f_{clk}$$

From the above equation, reducing the switching power consumption can be achieved by minimizing both of the physical capacitance and the switching activity.

# 3.3.1 Physical Capacitance Reduction

The physical capacitance can be reduced through selecting the appropriate circuit style and optimizing the transistor sizes.

# **Effects of Circuit Styles**

The different circuit and logic styles result in different gate and diffusion capacitance of the transistors in a combinational logic circuit. Some of the

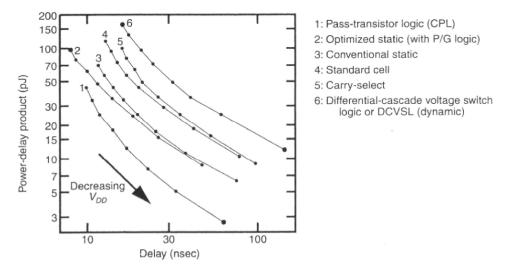

circuit styles can substantially reduced the physical capacitance and is good for low-power operation. Figure 3.3 shows the relationship between the power-delay products of an 8-bit adder that was implemented in 2  $\mu$ m CMOS technology with different circuit styles and the corresponding propagation delays [9].

Figure 3.3 Power-delay product versus delay for an 8-bit adder

As shown in Figure 3.3, the adder that was implemented by using complementary pass transistor logic (CPL) is about twice as fast as the conventional static CMOS. This is due to that CPL improves the performance of the circuit with a lower input capacitance and reduced voltage swing. Moreover, a CPL logic circuit consumes less power than a static CMOS one, for instance, the power saving for a CPL adder is about 30% compared to a conventional static CMOS adder [12]. This improvement is mainly due to the reduction in capacitance.

The performance of a full adder implemented with different circuit styles, such as conventional CMOS, transmission gate CMOS, CPL without output swing restoration, CPL with minimum size PMOS restoration transistors (LCPL2), CPL and TG combination (CPL-TG), has been compared in [13]. This comparison reveals that the circuit styles impact dramatically on the delay and power dissipation of the circuit. The compared results indicate that the CPL-TG provides the lowest power delay product, and the LCPL2

has the second lowest power delay product. Both of them are the best suited for low-power high-performance applications such as adders and multipliers.

### **Transistor Sizing**

The capacitive load that originates from transistor capacitance and interconnect wiring can be reduced by optimizing transistor sizes whenever possible and reasonable. In general, increasing the transistor sizes results in a large (dis)charging current and simultaneously increases the parasitic capacitance. On the other hand, reducing the transistor sizes will result in decreasing input capacitance that may be the load capacitance for other gates and lowering the speed of the circuit. Thus, the objective of transistor sizing is to obtain the minimum power dissipation under given performance requirements.

In order to explain how to make transistor sizing, let us consider a static inverter driving a load capacitance being composed of an intrinsic (diffusion) and an extrinsic (wiring and fan out) capacitances. When the total load capacitance to the gate output is dominated by the diffusion capacitance, the smallest possible sizes of the transistors should be used for obtaining the lowest power consumption. Otherwise, if the load capacitance is dominated by the extrinsic component, the power consumption first begins to decrease with increasing transistor sizes and then starts to increase. An optimal sizing factor that corresponds to the minimum power consumption can be found [8].

## 3.3.2 Switching Activity Reduction

The dynamic power consumption of a circuit is strongly related to the switching activity of the circuit. The node switching activity in the circuit is predominantly determined by the architectural and register transfer level [14]. At the circuit level, one main consideration for low-power designs is the choice of the static or dynamic logic styles. The dynamic logic gates are clocked, and undergo the precharge and evaluation phases, which are

suitable for high-speed applications at the expense of high power dissipation [14]. Whereas the static CMOS is the best choice for low-power high-speed implementation of dedicated circuit applications like multipliers [14].

The switching activity can be reduced by many means such as reordering input signals, no bus-sharing technique, and minimizing the glitching activity of the static circuits etc.

## **Minimizing Glitching Activity**

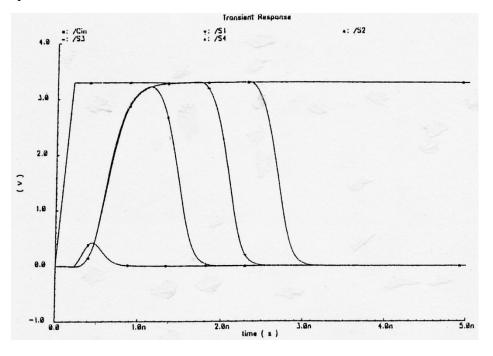

Glitches, or dynamic hazards, are unwanted signal transitions which occur before the signal settles to its intended value. Glitches can be generated and propagated in both data path and control parts of the circuits. Figure 3.4 illustrates the glitching behaviour for a 4-bit ripple carry adder which was implemented in static CMOS.

Figure 3.4 Glitching behaviour for a 4-bit RCA

The simulation result from the circuit simulator (Spectre) was obtained under the following conditions. All input bits of  $A_i$  and  $C_{in}$  go up from zero to one, and all the input bits of  $B_i$  are set to zero. As shown in the figure, spurious transitions appear at the sum bits of  $S_i$  due to the finite propagation delays of the intermediate carry signals. The spurious transitions consume extra power compared to the glitch-free scenarios. The number of spurious transitions in a circuit depends on the logic depth, input patterns, and intermediate carry signal states etc.

In some arithmetic circuits such as adders and multipliers, the glitches may result in a large portion of the switching power dissipation. For example, in a non-pipelined 16 by 16 bit array multiplier, 75% of the switching power consumption is due to glitches [15].

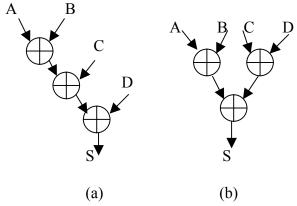

The glitching activity in static circuit designs can be minimized by selecting structures with balanced signal paths and reduced logic depth. The tree structures can be applied to implement a circuit with both of the balanced signal paths and less logic depth, while the chain structures are quite the contrary. A good example in figure 3.5 illustrates the choice of the tree or chain structures. In the chained implementation shown in figure 3.5(a), the second adder computes twice and the third adder computes three times per cycle due to the finite propagation delay through the previous adders. By contrast, the logic depth in the tree case has been reduced from three to two and the signal paths are more balanced. Thus, the switched capacitance (effective capacitance) for the chained case is a factor of 1.5 larger than in the tree [8].

Figure 3.5 Tree versus chain structures

Another possible approach to eliminate the spurious transitions is to use dynamic logic circuits instead of static logic, since any node in dynamic logic circuits can only undergo at most one transition per clock cycle.

### 3.4 Summary

This chapter briefly described some of the power reduction techniques that are related to the arithmetic circuit designs such as the adder and multiplier. In some arithmetic circuits, the major portion of the switching power consumption is due to glitches. The glitching activity can be minimized by selecting structures with balanced signal paths and reduced logic depth. Furthermore, both supply voltage scaling and reduction of effective capacitance are the important means to lower the power consumption.

This page is left blank on purpose.

# **Chapter 4** Multiplier Architecture

To meet the various demands of multiplication-based arithmetic operations, many classes of multipliers such as bit-serial multipliers, digit-serial multipliers, and parallel multipliers have been developed. However, for high-speed applications, the parallel multiplier is one of the best solutions.

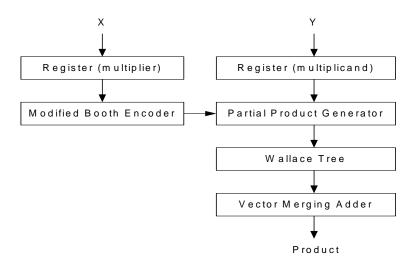

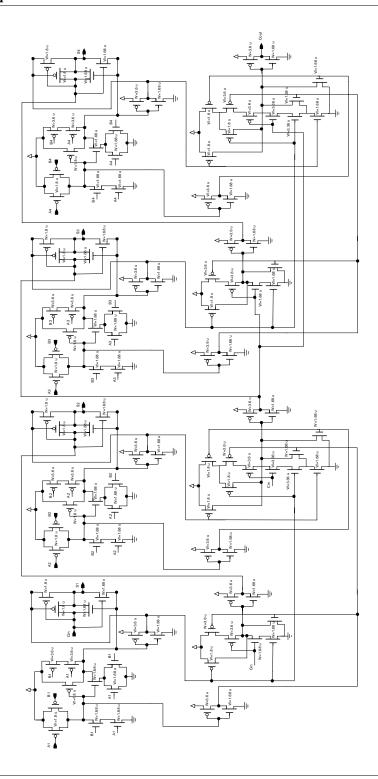

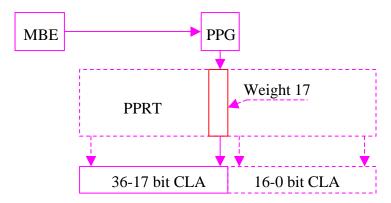

In general, the architecture of a parallel multiplier consists of the following parts: partial product generator (PPG), partial product reduction tree (PPRT), and final addition. Each part can be implemented by using various architectural choices. Figure 4.1 shows the architecture of the parallel multiplier that has been widely applied for the large multiplier.

Figure 4.1 Architecture of the parallel multiplier

This architecture consists of modified Booth encoder, partial product generator, Wallace tree that is also called partial product reduction tree, and vector merging adder (VMA).

#### 4.1 Modified Booth Encoder

When calculating fixed-point two-operand multiplication, the modified Booth (MB) encoding is often employed to produce the partial products. Usually, this method is more suitable for input operands of equal to or greater than 16-bit. Using MB encoding to generate partial products, the hardware for this section can be divided into the following three components: modified Booth encoder, partial product and sign bit generators, each component performs different logic functions.

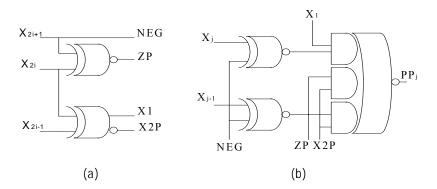

Assuming the multiplier X has n bits wide and the multiplicand Y has m bits, for this case, n/2 or (n+1)/2 three-input MB encoders are required. The n bit multiplier can be partitioned into overlapping groups of three bits in parallel. Each group acts as the input of one of the MB encoders. Each MB encoder generates several control signals to select one of the multiples of the multiplicand Y {0,  $\pm Y$ ,  $\pm 2Y$ }, the MB encoding scheme can reduce the number of partial product by 50% compared to the non-Booth encoding. The MB encoder can be implemented by using various fashions. A glitch-free MB encoder [16] at gate level is shown in Figure 4.2a.

Figure 4.2: a) Glitch-free MB encoder, b) Partial product generator

The partial product generation circuit by using MB encoding is composed of complex gates, as shown in Figure 4.2b [16]. Moreover, corresponding to the operations of the negative partial products  $\{-1Y, -2Y\}$ , one generator should be implemented. The one generator can be controlled by the adjacent

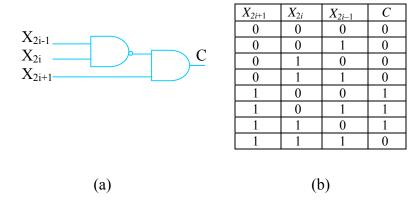

three bits of the multiplier, the circuit at gate level and the truth table are illustrated in Figure 4.3.

Figure 4.3: a) One generator, b) Truth table of the one generator

The sign bits of the partial products can be obtained by using sign extension or sign generate methods. A  $16 \times 16$  bit multiplier by using MB encoding scheme and sign generate is illustrated in Figure 4.4.

Figure 4.4 16×16 bit modified Booth encoding

#### 4.2 Partial Product Generator

The partial products in a parallel multiplier can be generated using several encoding methods, such as non-Booth encoding, modified Booth encoding (Radix 4), higher radix Booth encoding (Radix 8), and smaller multipliers methods etc. A glitch-free partial product generator with modified Booth encoding at the gate level is shown in figure 4.2(b).

Actually, the partial products can be generated in two stages. During first stage, the modified Booth encoders generate the Booth codes for encoding the multiplicand into partial products. After that, the partial product generators read in Booth code signals and encode multiplicand producing the partial products.

#### 4.3 Wallace Tree

The Wallace tree was proposed by C. S. Wallace in 1964 [17]. This method can be used to sum up all the bits of the partial product in each column. The summation is independent and simultaneous due to each modified Booth encoder works in parallel. It results in all bits of partial products arrive at the adder tree at the same time. Thus, the Wallace tree structure increases the speed of the multiplication by introducing parallelism.

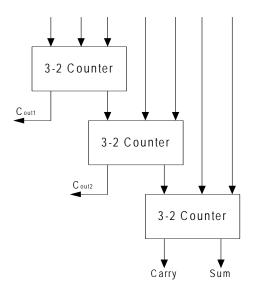

The Wallace tree was first constructed by using 3-2 counters (carry save adders). A 3-2 counter is also called a 3-2 compressor, which has three inputs and two outputs. This counter has a maximum of two XOR delays. The Wallace tree uses 3-2 counters to sum up all the partial products with the same weight, and produce two bits, one is the carry bit with the weight of n + 1 and the other is the sum bit with the weight of n.

In order to sum up N partial products to two bits, this operation requires about  $\lceil \log_{3/2}(N/2) \rceil$  levels of the 3-2 counters [31]. For example, if the maximal number of the partial product in a column is 7 bits, three levels are required, yielding the Wallace tree with 3-2 counters in Figure 4.5.

The Wallace tree with 3-2 counters is irregular in structure and is difficult to layout due to the irregular interconnections.

Figure 4.5 Wallace tree with 3-2 counters

### 4.4 4-2 Compressors

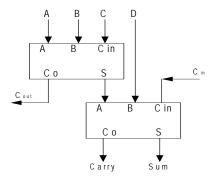

A more regular partial product reduction tree based on a binary tree can be obtained with 4-2 compressors. 4-2 compressors can be used to reduce the number of partial products by one half. This method was first proposed by A. Weinberger, and improved by V. G. Oklobdzija and D. Villeger [18]. A 4-2 compressor can be built by using two 3-2 counters (full adder based) in cascade, as described in Figure 4.6.

Figure 4.6 4-2 compressor built with two 3-2 counters

As described in Fig. 4.6, a 4-2 compressor has five inputs and three outputs. The five inputs and sum output have the same weight, whereas the outputs of Cout and Carry have one greater binary bit weight. In addition, the output of the Cout does not have to be a function of the Cin input, so that the carry propagation is avoided. By this implementation, the sum, intermediate carry and carry output signals can be expressed with

$$Sum = [[(A \oplus B) \oplus C] \oplus D] \oplus Cin$$

$$Cout = A \cdot B + A \cdot C + B \cdot C$$

$$Carry = [(A \oplus B) \oplus C] \cdot (D + Cin) + D \cdot Cin$$

The 4-2 compressor was constructed as described above and denoted the conventional approach. It has a critical path which contains a maximum of four XOR delays [19]. But this 4-2 compressor has more regular structure and suitable to layout than the 3-2 compressors. The truth table of the 4-2 compressor is shown in Table 4.1.

Table 4.1 Truth table of the 4-2 compressor

| Table 1.1 Train table of the 12 compressor |   |   |   |         |       |     |         |       |     |

|--------------------------------------------|---|---|---|---------|-------|-----|---------|-------|-----|

|                                            |   |   |   | Cin = 0 |       |     | Cin = 1 |       |     |

| A                                          | В | C | D | Cout    | Carry | Sum | Cout    | Carry | Sum |

| 0                                          | 0 | 0 | 0 | 0       | 0     | 0   | 0       | 0     | 1   |

| 0                                          | 0 | 0 | 1 | 0       | 0     | 1   | 0       | 1     | 0   |

| 0                                          | 0 | 1 | 0 | 0       | 0     | 1   | 0       | 1     | 0   |

| 0                                          | 0 | 1 | 1 | 0       | 1     | 0   | 0       | 1     | 1   |

| 0                                          | 1 | 0 | 0 | 0       | 0     | 1   | 0       | 1     | 0   |

| 0                                          | 1 | 0 | 1 | 0       | 1     | 0   | 0       | 1     | 1   |

| 0                                          | 1 | 1 | 0 | 1       | 0     | 0   | 1       | 0     | 1   |

| 0                                          | 1 | 1 | 1 | 1       | 0     | 1   | 1       | 1     | 0   |

| 1                                          | 0 | 0 | 0 | 0       | 0     | 1   | 0       | 1     | 0   |

| 1                                          | 0 | 0 | 1 | 0       | 1     | 0   | 0       | 1     | 1   |

| 1                                          | 0 | 1 | 0 | 1       | 0     | 0   | 1       | 0     | 1   |

| 1                                          | 0 | 1 | 1 | 1       | 0     | 1   | 1       | 1     | 0   |

| 1                                          | 1 | 0 | 0 | 1       | 0     | 0   | 1       | 0     | 1   |

| 1                                          | 1 | 0 | 1 | 1       | 0     | 1   | 1       | 1     | 0   |

| 1                                          | 1 | 1 | 0 | 1       | 0     | 1   | 1       | 1     | 0   |

| 1                                          | 1 | 1 | 1 | 1       | 1     | 0   | 1       | 1     | 1   |

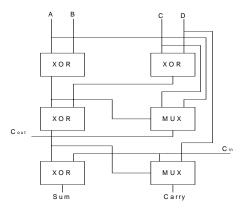

An improved approach to build a 4-2 compressor by using pass-transistor multiplexer [20] is shown in Figure 4.7. This structure of the 4-2 compressors includes a critical path with the maximal delay of three XORs. Thus, it has higher performance than that of the full adder based design.

Figure 4.7 An improved structure of the 4-2 compressor

A 4-2 compressor can further reduce the logic depth. For N partial products with the same weight, the summation tree built with 4-2 compressors has about  $\log_2 N$  levels.

### 4.5 Vector Merging Adders

The final unit in a parallel multiplier is a fast adder, which performs fast addition for the sum and carry bit vectors from the outputs of the PPRT. There are many different fast adders that suit parallel multipliers, such as carry look ahead, carry skip adder and carry select adder etc. In the following section, the carry look ahead adder and carry skip adder as well as the combination of them will be introduced.

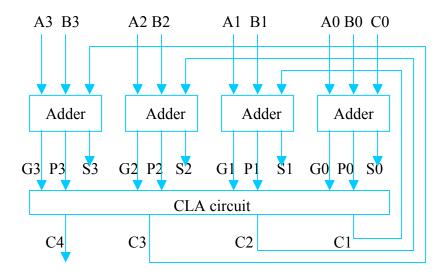

## 4.5.1 Carry Look Ahead Adder

Carry Look Ahead (CLA) can produce carries faster due to the carry bits generated in parallel whenever inputs change. This technique uses carry bypass logic to speed up the carry propagation. In order to explain carry look ahead, two important signals, traditionally called carry generate  $(G_i)$  and carry propagate  $(P_i)$ , are defined as follows.

$$G_i = A_i \cdot B_i$$

$$P_i = A_i \oplus B_i$$

The concept of the carry generation and propagation can be explained as follow. For a given stage, a carry signal is generated if  $G_i$  is true, and it propagates an input carry to its output if  $P_i$  is true.

The carry output signal can be derived from the carry generate, carry propagate and the carry-in signals, as expressed by

$$C_{i+1} = G_i + P_i \cdot C_i$$

To avoid carry ripple, the carry output  $C_{i+1}$  should be expressed by using the  $C_i$  for each stage.

Let us use this technique for the carries of a 4-bit CLA adder

$$\begin{split} C_1 &= G_0 + P_0 \cdot C_0 \\ C_2 &= G_1 + P_1 \cdot (G_0 + P_0 \cdot C_0) \\ C_3 &= G_2 + P_2 \cdot G_1 + P_2 \cdot P_1 \cdot G_0 + P_2 \cdot P_1 \cdot P_0 \cdot C_0 \\ C_4 &= G_3 + P_3 \cdot G_2 + P_3 \cdot P_2 \cdot G_1 + P_3 \cdot P_2 \cdot P_1 \cdot G_0 + P_3 \cdot P_2 \cdot P_1 \cdot P_0 \cdot C_0 \end{split}$$

The each above equation, there is a corresponding multi-input circuit. Figure 4.8 shows the block diagram of the 4-bit CLA adder.

From the figure, the CLA circuit generates the carry signals  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  by using the carry-in  $C_0$  simultaneously. The adder circuits generate the sums, which is expressed by

$$S_i = C_{i-1} + A_i \oplus B_i$$

$$= C_{i-1} + P_i$$

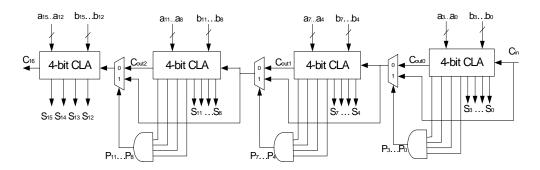

In general, 4-bit look ahead block is used to implement an *n*-bit CLA adder with a single level. To go faster, an n-bit CLA adder can be implemented at

a high level. The number of look ahead levels is  $\lceil \log_r n \rceil$ , where r is the maximum number of inputs per gate.

Figure 4.8 Block diagram of the 4-bit CLA adder

The delay of the CLA adder increases as the logarithm of the word size, whereas the delay of the ripple carry adder increases linearly with the word size. Thus, the addition performed by a multi-level CLA for a large word size is much faster than a ripple carry adder. For example, when we compare the number of gate delays for the critical path of two 16-bit adders, one using ripple carry and the other using two-level carry look ahead. As a result, for the 16-bit addition, carry look ahead adder is six times faster than ripple carry [2]. On the other hand, due to high complexity of carry look ahead circuit, it consumes more power than ripple carry adder.

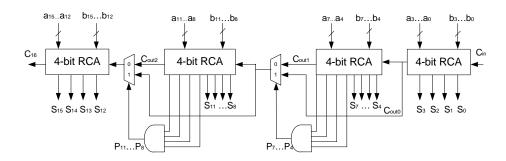

# 4.5.2 Carry Skip Adder

The carry skip adder is also called a carry bypass adder. In general, a carry skip adder should be built using n-bit ripple-carry adders as basic blocks and multiplexers. Figure 4.9 shows that the block diagram of a 16-bit carry skip adder. Each basic group can be constructed using 4-bit ripple-carry adder.

Each group also generates a group propagate signal  $P_i$  which is used as the select signals.  $P_i$  can be defined as

$$P_i = p_j \cdot p_{j+1} \cdot p_{j+2} \cdot p_{j+3}$$

(*i* = 1,2; *j* = 0,1,2,.... 15)

If  $P_1 = 1$ , the carry out signal  $C_{out0}$  from the first 4-bit RCA will propagate to the incoming carry of the next 4-bit RCA. In this way, it is possible to bypass the carry out  $C_{out0}$  to the carry in of the third or fourth 4-bit RCA. While  $P_i = 0$ , the whole carry skip adder becomes a ripple carry adder.

Figure 4-9 Block diagram of a 16-bit carry skip adder

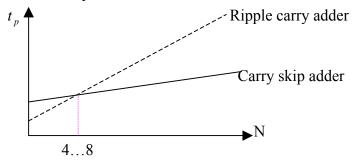

The total propagate delay is linear in the number of bits *N*. Figure 4.10 shows the relationship of the propagate delay between carry skip and ripple carry adders [9]. As can be seen in the figure, for a larger adder the carry skip adder is quite faster than a ripple carry adder, while for a smaller adder the ripple carry adder should be chosen. The crossover point depends on the technology, it is normally between 4 and 8 bits.

Figure 4.10 Propagation delay of the RCA versus CSKA

### 4.5.3 Carry Look ahead with Bypass Adder

The carry look ahead with bypass adder has the advantages of both carry look ahead and carry skip adders. The block diagram of a 16-bit carry look ahead with bypass adder is shown in figure 4.11. In this case, the bypass circuit can be implemented by using multiplexer which can be inserted between each CLA adder. The carry bypass signals  $BP_i$  is the function of the propagate signal,  $P_j$ , for each CLA. If a 4-bit carry look ahead adder used as a basic block constructs the 16-bit, the  $BP_i$  can be defined as

$$BP_i = p_j \cdot p_{j+1} \cdot p_{j+2} \cdot p_{j+3}$$

( $i = 1,2,3; j = 0,1,2,....15$ )

The critical path for the CLA with bypass adder could be the first CLA block, three multiplexers and the final CLA block. This method is more suitable for larger adders.

Figure 4-11 Block diagram of a 16-bit CLA with bypass adder

# 4.6 Partial Product Reduction Tree Topologies

After the partial products are generated, the partial product matrix must be summed up in each column to obtain the final product. To solve this problem, several techniques have been proposed such as the Wallace tree, Carry-save tree, and the Wallace tree based on 4-2 compressors. These approaches are generally called partial product reduction tree (PPRT) [21] or partial product compression tree (PPCT). The PPRT performs the multi-

operand addition for all the generated partial products and produces the two vectors, the carry and sum.

The summation in the PPRT usually adopts counters and compressors. The counters and compressors can be connected in several different ways. This is a major consideration in the design of parallel multiplier due to different interconnection among these components, leading to different critical path delay. A special terminology, which is called multiplier topology, has been used to describe how to configure the PPRT. That is, the multiplier topology refers to the way of interconnection among bit positions in PPRT.

The multiplier topology has two important points to keep in mind, one is the minimum number of wires needed to interconnect the counters or compressors, and the other is the number of counter or compressor delays. The topologies for configuring the PPRT can be roughly classified into regular and irregular structures.

### 4.6.1 Regular Topologies

Use of regular topology is a common method in custom digital circuit design, especially for the design of parallel multipliers. Regular topology takes into account a trade-off between performance optimisation and design effort. Regularity makes the generation of the structure possible to program. Regular topology can be realized in array and tree structures.

# 4.6.1.1 Array Structures

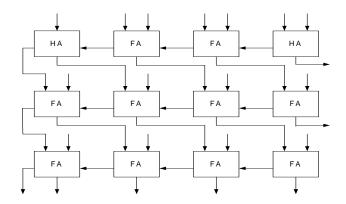

To introduce array structures in a PPRT, let us consider the multiple of two unsigned 4-bit binary numbers. If we apply manual computational method and directly map the operations into hardware, the resulting structure is called an array multiplier. In this case, there is a one-to-one correspondence between the partial products in the multiplier and the ones in the manual method. The adder tree with an array structure is shown in Figure 4.12.

The array topology in figure 4.12 is implemented as ripple carry structure. This array method is also called linear or simple array. There are more than two almost identical critical paths in this array.

Figure 4.12 4×4 ripple carry array multiplier

The optimization of the performance can only be achieved with careful transistor sizing, which is time-consuming. Another more efficient array structure can be obtained by using carry save adders. The PPRT without the final adder is presented in figure 4.13.

Figure 4.13 Rectangular floorplan of  $4 \times 4$  carry save multiplier

In this way, the array just includes only one worst-case critical path. The number of counter delays is two full adder plus one half adder, while the number of wiring tracks per bit channel is 3.

Obviously, the addition of partial products can be performed with (m, n) counters and 4-2 compressors in an array topology. For example, a  $54 \times 54$ -

bit full parallel multiplier [22] adopted 4-2 compressors to construct the PPRT, as shown in Figure 4.14.

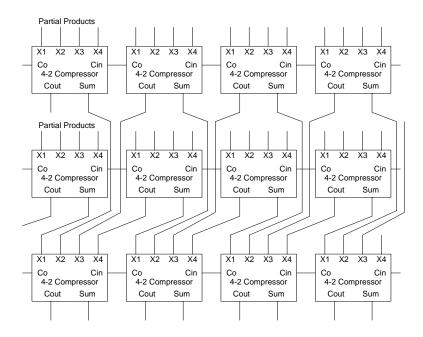

Figure 4.14 Array topology using 4-2 compressors

For this special case, the 4-2 compressors in four levels are needed to add 27 partial products. The compressors can sum up the partial products concurrently. Though the carry out *Co* signal is connected to next 4-2 compressor's carry-in signal, *Cin*, as can be seen in the figure, the *Co* is never produced by *Cin*. Moreover, the 4-2 compressors have 3 XOR gate propagations at the critical path, while two 3-2 counters in carry-save adder tree have 4 XOR gate propagations. Hence, the array topology used 4-2 compressors can speed up the summing computation compared to an ordinary carry save array structure.

In summary, the principle of array topology is to minimize the width of wiring channel per bit position at the expense of counter delays. Comparatively, array topologies have poor speed performance and power wastage due to spurious transitions. But this method has a regular structure and is easy to layout, therefore it still is a common approach to partial product reduction.

#### 4.6.1.2 Tree Structures

Trees, similar to the array mentioned above, are also constructed using counters and compressors, but the tree structure is substantially faster than the array topology due to the optimized depth at the expense of the width of a tree [31]. The width of a tree also refers to the number of wires per bit position in the tree.

Trees are either regular ones or irregular. The width of regular tree is a known function of the number of partial products, while the width of irregular tree is determined by design layout. The regular trees contain binary tree, balanced-delay tree, and overturned staircase tree etc. In this section, a brief overview of the binary and balanced-delay trees will be given.

# **Binary Tree**

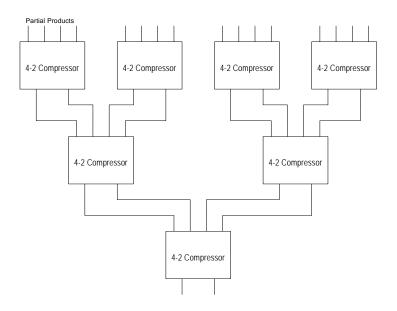

The binary tree [23] has a regular structure. This tree is implemented using 4-2 compressors. 4-2 compressors are also called (5,3) counters due to the components with 5 inputs and 3 outputs. The 4-2 compressors can be combined using two (3,2) counters serially or implemented using the method shown in figure 4.7. The latter has three XORs delay in the critical path, whereas the former with four XORs delay.

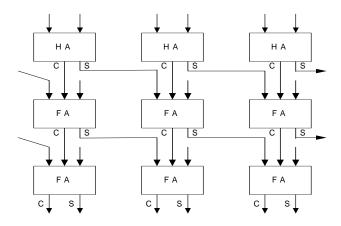

The binary tree topology with 4-2 compressors is similar to the complete binary tree with n nodes. When the n nodes in the complete binary tree are replaced using 4-2 compressors, the resulting structure becomes the binary tree topology that can reduce n partial products to two bits. The bit slice of a 16-bit binary tree is shown in figure 4.15 [31] on the next page.

The 4-2 compressors can reduce the partial products in the 2-to-1 compression ratios. Therefore, to reduce n partial products to two, the  $\lceil \log_2(n/2) \rceil$  levels of 4-2 compressors are needed [32].

Figure 4.15 A binary tree topology with 4-2 compressors

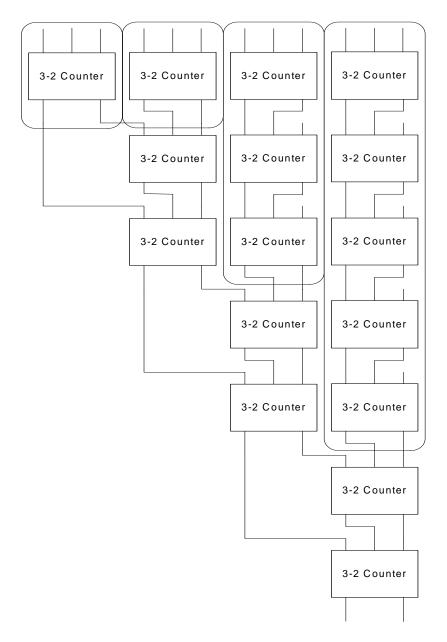

### **Balanced Delay Tree**

The balanced delay tree was proposed by D.Zuras and W.McAllister (ZM) [24] in 1986. This tree has regular tree structure. It can be recursively defined by a tree body and a chain. The tree body and chain consist of 3-2 counters, the delay in each chain is the same as one of the tree. Figure 4.16 illustrates a balanced delay tree [31], which reduces 18 partial products to two. As can be seen in the figure, the series 3-2 counters increase in the lateral direction as 1, 1, 3, 5,... The tree constructed in this way is called a balanced delay tree of type 1. This tree can reduce the *N* partial products in  $O(2\sqrt{N})$  3-2 counters levels [31].

## 4.6.2 Irregular Topologies

The first tree for partial product reduction was the Wallace tree [17], which was an irregular tree originally built using 3-2 counters. This topology can speed up the multiplication time for large multipliers compared to the carry save structure. On the other hand, it is hard to design and layout due to the irregularity and complexity. Thus, the Wallace tree is only applied to the

designs whose performance is critical and design effort is of secondary consideration.

Figure 4.16 A balanced delay tree topology using 3-2 counters

### 4.7 Summary

In this chapter, the most commonly used architecture for implementation of a parallel multiplier was presented, and the partial product reduction tree topologies were also described. The topologies can be divided into either regular or irregular. The regular topology can be realized in array and tree structures, which takes into account a trade-off between performance optimization and design effort. The irregular topology is applied to the designs whose performance is critical and the design effort is of secondary consideration.

# **Chapter 5** Implementation

Various design and implementation techniques for parallel multipliers have been proposed. However, most of these techniques can only be applied for that of fixed word-length multipliers. This means that when the word-length of the multipliers or the process technology is changed, the whole circuits need to be redesigned. To solve this problem, this chapter describes the design procedure of the parallel multipliers with variable sizes through the implementation of an 18×18 bit multiplier. This design consists of the logic, circuit and physical stages. The meet-in-the-middle design methodology will be used in this thesis. For this custom design, the speed, area and power trade-off of the multipliers should be taken into account. Furthermore, some choices for the design from the architecture to the circuit styles will be made later in the following sections.

#### 5.1 Architecture Selection

Selecting the architecture is very important before starting the detailed design, since the performance such as speed, area, and power dissipation strongly depends on the architecture of the multiplier. The architecture should be low-power, high-performance, and easy to implement. The choice of the architecture should include the encoding scheme, sign extension method, partial product reduction structure and the final addition. The chosen architecture is shown in figure 4.1.

For the selected architecture, the modified Booth encoding is used for this design due to MBE can reduce the number of the partial products by a factor of 50%, which results in a higher speed and a lower power dissipation than a non-Booth encoding scheme. Also, the glitch-free partial product generator is employed, whose gate-level circuit is shown in figure 4.2(b). In addition, the Wallace tree with 4-2 compressors is applied to the partial product reduction tree. The tree structure in the static style can reduce the spurious

transitions as mentioned in section 3.3.2 and increase the speed of summing by means of increased parallelism as well as result in a much more regular structure. Furthermore, the carry look-ahead adders that uses block of 4 bits are made use of the final addition. These are the most common choice and more suitable for the cell-based design of the multiplier with different operand sizes.

### **5.2 Design Methodology**

For a custom ASIC design, several design methodologies such as bottomup, top-down and meet-in-the-middle have been proposed. These methods can be applied to deal with the design complexities and reduce the design time. Which methodology to select depends on the system requirements, the complexity, the cost and the available time. In this thesis, the meet-in-themiddle design method will be used to develop the module generator for parallel multipliers. By using this method, the logic and circuit designs could be started independently and simultaneously, but the results for the logic and circuit designs should be exactly same. The basic principle of this method is that the specification process is essentially a top-down method to validate the functional correctness, while the design of the building blocks for the circuits starts from the bottom level. Thus, the advantages of this methodology are that the library cells can be reused, and the circuit design phase can be shorted through using program creating the structural schematic. Because the cell-based design of a large parallel multiplier could include hundreds of building blocks and the interconnections among these blocks could be up to thousands. In such a case, the structural schematic of a manually generated multiplier is hard to ensure correctness for.

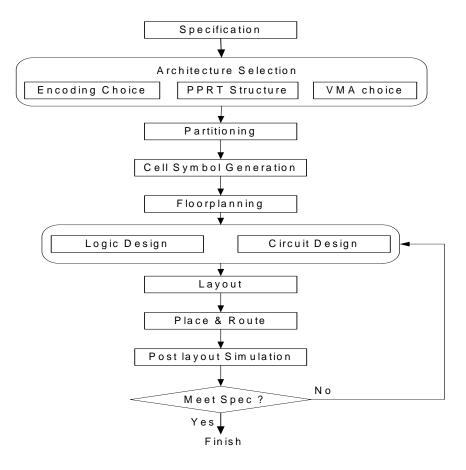

# **5.3 Design Flow**

The previous section presents the architecture and the design methodology employed in the multiplier. In this section, the design flow used to realize the above architecture is presented, as shown in figure 5.1.

The design process based on the design flow starts from the specification that defines the functionality and performance targets according to the user's requirements. Based on the specification, the architecture, including the encoding scheme, the PPRT structure, and the vector merging adder

should be chosen. The modified Booth encoding method and its application in multiplier have been proved in [25, 30]. In general, the design is partitioned into more basic blocks so that each block can be reused and analysed individually. After this, each cell symbol is created in Cadence, however, the cell symbols at this moment are combined by using only empty rectangles with the input and output pin names, the circuit inside is going to be designed in circuit design stage. Also, the preliminary floorplan should be created through estimating the size and complexity of the each block. Based on the above design steps, the logic and circuit design can be started. When logic and circuit designs are complete, the physical design may begin. In the subsequent subsections, these three design stages will be presented in more detail.

Figure 5.1 Design flow

### 5.4 Logic Design