**Doctoral Thesis in Electronics**

# Germanium layer transfer and device fabrication for monolithic 3D integration

AHMAD ABEDIN

# Germanium layer transfer and device fabrication for monolithic 3D integration

**AHMAD ABEDIN**

Academic Dissertation which, with due permission of the KTH Royal Institute of Technology, is submitted for public defence for the Degree of Doctor of Philosophy on Friday the 21st May 2021, at 1:00 p.m. in Sal C, Kistagången 16, Stockholm, Sweden.

Doctoral Thesis in Electronics KTH Royal Institute of Technology Stockholm, Sweden 2021

| © Ahmad Abedin<br>© Mikael Östling, Per-Erik Hellström, Pooria Asadollahi, Konstantinous Garidis, Laura Zurauskaite, Gunnar Malm,<br>Ganesh Jayakumar |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISBN 978-91-7873-834-2<br>TRITA-EECS-AVL-2021:23                                                                                                      |

| Printed by: Universitetsservice US-AB, Sweden 2021                                                                                                    |

#### Abstract

Monolithic three-dimensional (M3D) integration, it has been proposed, can overcome the limitations of further circuits' performance improvement and functionality expansion. The emergence of the internet of things (IoT) is driving the semiconductor industry toward the fabrication of higher-performance circuits with diverse functionality. On the one hand, the scaling of devices is reaching critical dimensions, which makes their further downscaling technologically difficult and economically challenging, whereas, on the other hand, the field of electronics is no longer limited only to developing circuits that are meant for data processing. Sensors, processors, actuators, memories, and even power storage units need to be efficiently integrated into a single chip to make IoT work. M3D integration through stacking different layers of devices on each other can potentially improve circuits' performance by shortening the wiring length and reducing the interconnect delay. Using multiple tiers for device fabrication makes it possible to integrate different materials with superior physical properties. It offers the advantage of fabricating higherperformance devices with multiple functionalities on a single chip. However, high-quality layer transfer and processing temperature budget are the major challenges in M3D integration. This thesis involves an in-depth exploration of the application of germanium (Ge) in monolithic 3D integration.

Ge has been recognized as one of the most promising materials that can replace silicon (Si) as the channel material for p-type field-effect transistors (pFETs) because of its high hole mobility. Ge pFETs can be fabricated at substantially lower temperatures compared to Si devices which makes the former a good candidate for M3D integration. However, the fabrication of high-quality Ge-on-insulator (GOI) layers with superior thickness homogeneity, low residual doping, and a sufficiently good interface with buried oxide (BOX) has been challenging.

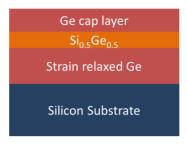

This thesis used low-temperature wafer bonding and etch-back techniques to fabricate the GOI substrate for M3D applications. For this purpose, a unique stack of epitaxial layers was designed and fabricated. The layer stack contains a Ge strain relaxed buffer (SRB) layer, a SiGe layer to be used as an etch stop, and a top Ge layer to be transferred to the handling wafer. The wafers were bonded at room temperature, and the sacrificial wafer was removed through multiple etching steps leaving 20 nm Ge on the insulator with excellent thickness homogeneity over the wafer. Ge pFET devices were fabricated on the GOI substrates and electrically characterized to evaluate the layer quality. Finally, the epitaxial growth of the highly doped SiGe and sub-nm Si cap layers have been investigated as alternatives for improved performance Ge pFETs.

The Ge buffer layer was developed through the two-step deposition technique resulting in defect density of  $10^7 cm^{-3}$  and surface roughness of 0.5 nm. The fully strained  $Si_{0.5}Ge_{0.5}$  film with high crystal quality was epitaxially grown at temperatures below 450°C. The layer was sandwiched between the Ge buffer and the top 20 nm Ge layer to be used as an etch-stop in the etch-

back process. A highly selective etching method was developed to remove the 3  $\mu m$  Ge buffer and 10nm SiGe film without damaging the 20 nm transferring Ge layer.

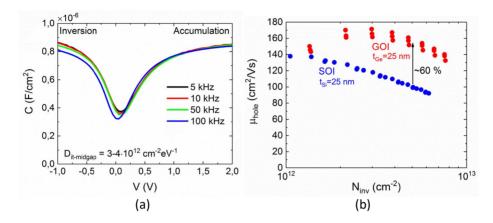

The Ge pFETs were fabricated at temperatures below 600°C so that they could be compatible with the M3D integration. The back interface of the devices depleted at  $V_{BG} = 0V$ , which confirmed the small density of fixed charges at the Ge/BOX interface along with a low level of residual doping in the Ge channel. The Ge pFETs with 70 % yield over the whole wafer showed 60 % higher carrier mobility than Si reference devices.

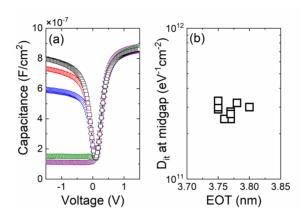

Low-temperature epitaxial growth of Si passivation layer on Ge was developed in this thesis. For electrical evaluation of the passivation layer, metal-oxide-semiconductor (MOS) capacitors were fabricated and characterized. The capacitors showed an interface trap density of  $3\times10^{11}eV^{-1}cm^{-2}$ , and hysteresis as low as 3 mV at Eox of 4MV/cm corresponding to oxide trap density of  $1.5\times10^{10}cm^{-2}$ . The results indicate that this Si passivation layer substantially improves the gate dielectric by reducing the subthreshold slope of Ge devices while increasing their reliability. The in-situ doped SiGe layer with a dopant concentration of  $2.5\times10^{19}cm^{-3}$  and resistivity of 3.5 m $\Omega$ cm was selectively grown on Ge to improve the junction formation.

The methods developed in this thesis are suitable for large-scale M3D integration of Ge pFET devices on the Si platform. The unique Ge layer transfer and etch-back techniques resulted in the fabrication of GOI substrates with high thickness homogeneity, low residual doping, and sufficiently good Ge/BOX interface. The process temperatures for Ge transfer and pFETs fabrication are kept within the range of the M3D budget. Integration of the Si cap for gate dielectric formation and SiGe layers in the source/drain region may increase device performance and reliability.

**Keywords:** Monolithic, sequential, 3D, silicon, germanium, wafer bonding, etch back, germanium on insulator, GOI, Ge pFET, low temperature, Si passivation, pn junction

Ahmad Abedin, aabedin@kth.se

Department of Electronics

School of Electrical Engineering and Computer Science

KTH Royal Institute of Technology, SE-164 40 Kista, Sweden

#### Sammanfattning

Sakernas internet (eng. Internet of Things, IoT) driver halvledarindustrin mot tillverkning av högprestanda komponenter och kretsar med flertal funktionaliteter. Å ena sidan skalas komponenter ned till storlekar där ytterligare nedskalning blir teknologiskt svårt och ekonomiskt utmanande. Å andra sidan är dagens elektronik inte längre begränsad till kretsar för databehandling. För att sakernas internet ska fungera behöver sensorer, processorer, styrdon, datorminne och även energilagringsenheter integreras på ett effektivt sätt i gemensamma chip. Monolitisk 3-dimensionell integration (M3D) baseras på att stapla olika komponentnivåer på varandra. Detta tillvägagångssätt är en av dem mest lovande metoderna för att förbättra kretsarnas prestanda. Prestandan förbättras genom att förkorta elektriska ledare och minska fördröjningen i ledarna. Att ha flera komponentnivåer möjliggör integration av komponenter, som kan använda sig av olika material med högkvalitetsegenskaper för olika tillämpningar och funktioner, i ett enda chip. De stora utmaningarna för M3D är högkvalitétsöverföring av skikt och begränsad processtemperatursbudget. Germanium (Ge) anses vara det bästa materialet för att ersätta kisel (Si) som kanalmaterial i p-typs fälteffektstransistorer (pFET) tack vare dess höga hålmobilitet. Vidare anses germanium lovande för M3D-integration tack germaniumtransistorernas jämförelsevisa låga processtemperatur mot motsvarande kiseltransistorer. Dock har tillverkning av germanium-på-isolator (eng. germanium on insulator, GOI) flera utmaningar: tjockleken på germaniumskiktet måste vara jämnt över skivan, dopningen måste vara låg och gränssnittet mot den begravda oxiden (eng. buried oxide, BOX) måste vara tillräckligt god. I denna avhandling används skivbondning vid låg temperatur och tillbaka-ets för att tillverka GOI-substrat för M3D-tillämpningar. En unik stapling av epitaxiellt växta skikt har designats och tillverkats för detta ändamål. Skiktstaplingen innehåller ett relaxerad bufferskikt av germanium, ett etsstoppsskikt av kiselgermanium (SiGe) och ett toppskikt av germanium som i slutändan överförs till en hanteringsskiva. Skivorna direktbondas vid rumstemperatur, och offerskivan togs bort genom flera etssteg som lämnar 20 nm germanium på isolator med utmärkt tjockleksjämnhet över skivan. Germaniumtransistorer tillverkades på GOI-substrat och mättes elektriskt för att utvärdera skiktkvalitén. Epitaxiellt växt av högdopat SiGe och sub-nanometer kiseltäckeskikt (eng. silicon cap layer) utforskades som alternativ för germaniumtransistorer med förbättrad prestanda.

Bufferskikt av germanium togs fram med två-stegs deponeringsteknik vilket gav resultatet att defekttätheten var  $10^7cm^{-3}$  och ytruffighet var 0,5 nm. Töjt  $Si_{0,5}Ge_{0,5}$ -skikt med hög kristallkvalité växtes epitaxiellt vid temperaturer lägre än 450°C. Skiktet, som infogades mellan bufferskiktet av germanium och toppskiktet av 20-nm tjockt germanium, användes som etsstopp i tillbaka-etsprocessen. En mycket selektiv etsmetod utvecklades för att ta bort den 3-µm tjocka bufferskiktet av germanium och den 10-nm tjocka  $Si_{0,5}Ge_{0,5}$ -skiktet utan att skada den 20-nm tjocka germaniumtoppskiktet. För att tillverkningen av germaniumtransistorerna ska var kompatibla med M3D-integration så tillverkades dem vid en temperatur lägre än 600°C. Kom-

ponentens baksidesgränsnitt (Ge/BOX-gränssnittet) var utarmat vid  $V_{BG}$  = 0V, vilket bekräftar att både den fixa laddningstätheten vid gränssnittet och dopningen var lågt. Germaniumtransistorerna hade 70 % avkastning över hela skivan och uppvisade 60 % högre kanalmobilitet än motsvarande komponenter i kisel. In-situ dopat SiGe-skikt med dopningskoncentration på  $2.5\times 10^{19}cm^{-3}$ och resistivitet på 3.5 mcm växtes selektivt på germanium för att förbättra käll- och dräneringsövergångsbildningen. Den unika staplingen av grinddielektrika  $Ge/Si/TmSiO/Tm_2O_3/HfO_2/TiN$  som togs fram i denna avhandling uppvisade en gränssnittsfälltäthet på  $3 \times 10^{11} eV^{-1} cm^{-2}$  och en hysteres på låga 3 mV vid ett pålagt elektriskt fält över grinddielektrikastapeln på 4 MV/cm, vilket motsvarar en oxidfälltäthet på  $1.5 \times 10^{10} cm^{-2}$ . Dessa resultat visar att denna grinddielektrikastapel kan potentiellt minska germaniumtransistorernas undertröskelsving samtidigt som den förbättrar tillförlitligheten. Metoderna som har tagits fram i denna avhandling är lämpliga för storskalig M3D-integration av germaniumtransistorer på en kiselplattform. Den unika skiktöverföringmetoden av germanium och tillbaka-ets tekniken resulterade i tillverkningen av GOI-substrat med god tjockleksjämnhet, låg dopning och tillräckligt god Ge/BOX-gränssnitt. Processtemperaturerna för germanium-överföring och transistortillverkning hålls inom ramarna för M3Dintegrationens temperaturbudget. Integration av SiGe-skikt i käll/dräneringsområden och kiseltäcket för grinddielektrikumbildning kan öka komponentprestanda och tillförlitlighet.

**Nyckelord:** Kisel, germanium, epitaxi, selektiv, pn-övergång, germanium på isolator, GOI, Ge PFET, bonding, monolitisk, sekventiell, tre dimensionell, 3D, lågtemperarad

Ahmad Abedin, aabedin@kth.se Avdelningen för Elektronik Skolan för Elektroteknik och Datavetenskap Kungliga Tekniska Högskolan, SE-164 40 Kista, Sverige

## Contents

| C  | onter                     | nts                                                                                  | i                |

|----|---------------------------|--------------------------------------------------------------------------------------|------------------|

| Li | st of                     | Publications                                                                         | iii              |

| Li | st of                     | Figures                                                                              | vi               |

| Li | st of                     | Tables                                                                               | viii             |

| Li | st of                     | Acronyms                                                                             | ix               |

| 1  | Intr<br>1.1<br>1.2<br>1.3 | Motivation                                                                           | 1<br>1<br>3<br>6 |

| 2  |                           | Organization of the thesis                                                           | 7<br>7           |

| 3  | Epit                      | taxial growth of Ge and SiGe                                                         | 11               |

|    | 3.1                       | Epitaxy                                                                              | 11               |

|    | 3.2                       | ASM Epsilon 2000 Reactor                                                             | 14               |

|    | 3.3                       | Epitaxial growth of Germanium SRB on Si(001)                                         | 15               |

|    |                           | 3.3.1 Germanium growth using germane                                                 | 18               |

|    | 0.4                       | 3.3.2 Ge growth using digermane                                                      | 20               |

|    | 3.4                       | SiGe epitaxial growth on Si and Ge                                                   | 23               |

|    |                           | 3.4.1 SiGe epitaxial growth using silane-germane                                     |                  |

|    |                           | 3.4.2 SiGe epitaxial growth using disilane-digermane $Si_{0.5}Ge_{0.5}$ growth on Ge | $\frac{25}{27}$  |

|    | 3.5                       | The full stack growth                                                                | 28               |

| 4  | Fab                       | rication of Germanium on insulator                                                   | 31               |

|    | 4.1                       | Wafer bonding and layer transfer                                                     |                  |

|    |                           | 4.1.1 Direct wafer bonding                                                           | 32               |

ii CONTENTS

|              | 4.2    | Removing the sacrificial wafer                          | 34 |

|--------------|--------|---------------------------------------------------------|----|

|              |        | 4.2.1 Smart-Cut and grinding                            | 34 |

|              |        | 4.2.2 Etch-back                                         | 35 |

|              | 4.3    | Methods for evaluating wafer bonding                    | 35 |

|              |        | 4.3.1 Bonding strength measurement                      | 35 |

|              |        | 4.3.2 Post-bonding process resilience                   | 35 |

|              |        | 4.3.3 Voids density measurement                         | 36 |

|              | 4.4    | GoI fabrication process in this research                | 37 |

|              |        | 4.4.1 ALD Oxide Deposition                              | 37 |

|              |        | 4.4.2 Wafer Bonding                                     | 38 |

|              |        | 4.4.3 Baking                                            | 39 |

|              |        | 4.4.4 Si etching                                        | 39 |

|              |        | 4.4.5 Ge and SiGe etching                               | 40 |

| 5            | Ge     | pFET fabrication                                        | 43 |

|              | 5.1    | Fabrication of Ge pFETs                                 | 43 |

|              | 5.2    | Fabrication of SoI pFETs                                | 44 |

|              | 5.3    | Characterizations of Ge pFETs                           | 45 |

| 6            | Imr    | provement of Ge transistors performance                 | 49 |

|              | 6.1    | <u>-</u>                                                | 49 |

|              |        | 6.1.1 Si passivation layer deposition                   | 50 |

|              |        | 6.1.2 Ge MOS capacitor fabrication using Si passivation | 52 |

|              | 6.2    | Selective epitaxy for source and drain                  | 56 |

|              |        | 6.2.1 In-situ doped SiGe growth                         | 56 |

| 7            | Con    | nclusions and outlook                                   | 59 |

|              | 7.1    | Summary                                                 | 59 |

|              | 7.2    | Outlook                                                 | 62 |

| $\mathbf{A}$ | cknov  | wledgements                                             | 63 |

| B            | ihlion | graphy                                                  | 65 |

|              |        |                                                         |    |

| $\mathbf{A}$ | ppen   | ded papers                                              | 77 |

## List of Publications

This thesis is based on the following papers in peer-reviewed international journals and reviewed conference proceedings:

I. "Epitaxial Growth of Ge Strain Relaxed Buffer on Si with Low Threading Dislocation Density"

**A. Abedin**, A. Asadollahi, K. Garidis, P.-E. Hellström, M. Östling *ECS Transactions*, vol.75, pp.615. (2016)

DOI: 10.1149/07508.0615ecst

II. "Growth of epitaxial SiGe alloys as etch-stop layers in germanium-on-insulator fabrication"

**A. Abedin\***, K. Garidis\*, A. Asadollahi, P.-E. Hellström, M. Östling *Under review*.

III. "Germanium on Insulator Fabrication for Monolithic 3-D Integration"

**A. Abedin**, L. Zurauskaite, A. Asadollahi, K. Garidis, G. Jayakumar, B. G. Malm, P.-E. Hellström, M. Östling

IEEE Journal of the Electron Devices Society, vol.6, pp.588. (2018)

DOI: 10.1109/JEDS.2018.2801335

IV. "Si-passivated Ge Gate Stacks with Low Interface State and Oxide Trap Densities Using Thulium Silicate"

L. Žurauskaitė, A. Abedin, P.-E. Hellström, and M. Östling

ECS Transactions, vol.98, pp.387. (2020) DOI: 10.1149/09805.0387ecst

V. "Selective epitaxial growth of in situ doped SiGe on bulk Ge substrates for p+/n junction formation"

K. Garidis, A. Abedin, A. Asadollahi, P.-E. Hellström, M. Östling *Electronics*, vol.9, pp.578. (2020)

DOI: 10.3390/electronics9040578

\*: Equal Contributions

| The contribution of Ahmad                            | Abedin | to each | publication, | major | $(\bullet \bullet \bullet),$ |

|------------------------------------------------------|--------|---------|--------------|-------|------------------------------|

| partial $(\bullet \bullet)$ , or minor $(\bullet)$ : |        |         |              |       |                              |

|      | Design | Fabrication | Characterization | Analysis | Writing |

|------|--------|-------------|------------------|----------|---------|

| I.   | • •    | •••         | • •              | • • •    | •••     |

| II.  | •••    | ••          | •••              | ••       | •••     |

| III. | • • •  | ••          | ••               | ••       | •••     |

| IV.  | •••    | • •         | ••               | •        | •       |

| V.   | •      | ••          | • •              | ••       | •       |

The work has also been presented at the following *Publications and international conferences*:

- VI. "Semiconductor devices for lasing application and methods of manufacturing such devices

- **A. Abedin**, M. Östling *United States Patent Application*, US2021/0104871A1, (2021)

- VII. "Sensitivity of the crystal quality of SiGe layers grown at low temperatures by trisilane and germane"

- **A. Abedin**, M.Moeen, C. Cappetta, M. Östling, H.H. Radamson *Thin Solid Films*, vol.38, pp.613. (2016)

- VIII. "GOI fabrication for monolithic 3D integration"

- **A. Abedin**, L. Zurauskaite, A. Asadollahi, K. Garidis, G. Jayakumar, B. G. Malm, P.-E. Hellström, M. Östling

IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), pp.81-84, Oral Presentation. (2017)

- IX. "IR-Photodetector Fabrication on Suspended Gesn Thin Layers"

A. Abedin, K. Garidis, P.-E. Hellström, M. Ostling

ECS Meeting, MA2018-02 1023, Oral Presentation. (2018)

- X. "Integration of highly-strained SiGe materials in 14 nm and beyond nodes FinFET technology"

G Wang, **A. Abedin**, M Moeen, M Kolahdouz, J Luo, Y Guo, T Chen, H Yin, H.H. Radamson

Solid-State Electronics, vol.103, pp.222-228. (2015)

XI. "Optimization of SiGe selective epitaxy for source/drain engineering in 22nm node complementary metal-oxide semiconductor (CMOS)"

GL Wang, M Moeen, **A. Abedin**, M Kolahdouz, J Luo, CL Qin, HL Zhu, H.H. Radamson

Journal of Applied Physics, vol.114, 123511. (2013)

- XII. "Impact of pattern dependency of SiGe layers grown selectively in source/drain on the performance of 22 nm node pMOSFETs"

- G Wang, M Moeen,  ${\bf A.~Abedin},~{\rm Y}$ Xu, J Luo, Y Guo, C Qin, Z Tang, H Yin, H.H. Radamson

- Solid-State Electronics, vol.114, pp.43-48. (2015)

- XIII. "Formation of nickel germanides from Ni layers with thickness below 10 nm" L Jablonka, T Kubart, D Primetzhofer, A. Abedin, PE Hellström, M Östling J. Vac. Sci. Technol., vol.35, 020602. (2017)

- XIV. "Improved designs of Si-based quantum wells and Schottky diodes for IR detection"

- M Moeen, M Kolahdouz, A Salemi, **A. Abedin**, M Östling, HH Radamson *Thin Solid Films*, vol.613, pp.19-23. (2016)

- XV. "Scalability Study of Nickel Germanides"

L. Jablonka, T. Kubart, F. Gustavsson, D. Primetzhofer, A. Abedin, P.E. Hellström, Z. Zhang

Paper presented at Materials for Advanced Metallization (MAM), Brussels, March. (2016)

- XVI. "Effect of strain on Ni-(GeSn)x contact formation to GeSn nanowires" M. Noroozi, M. Moeen, A. Abedin, M.S. Toprak H.H. Radamson MRS Online Proceedings Library, vol.1707, pp.7-12. (2015)

ECS Transactors, vol.64, pp.703. (2016)

XVII. "CVD Growth of GeSnSiC Alloys Using Disilane, Digermane, Tin Tetrachloride and Methylsilane"

M Noroozi, **A. Abedin**, M Moeen, M Östling, HH Radamson

# List of Figures

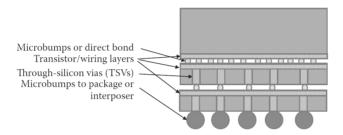

| 2.1  | Schematic of 3D stacking by using interposer                                                                                                  | 8     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.1  | Schematic of the epitaxial stack for wafer bonding and Ge layer transfer on insulator                                                         | 14    |

| 3.2  | Photo of the quartz chamber of ASM Epsilon 2000                                                                                               | 15    |

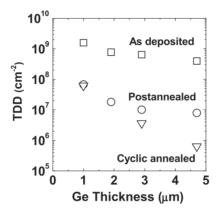

| 3.3  | TDD vs Ge thickness [30]                                                                                                                      | 17    |

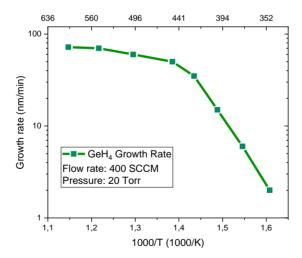

| 3.4  | Ge growth rate versus temperature with germane flow of 400 SCCM at 20 Torr                                                                    | 18    |

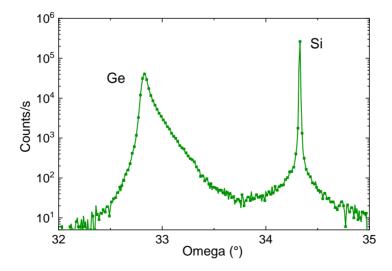

| 3.5  | XRD Omega/2Tetha scan around (004) direction of Ge buffer layer on Si                                                                         | 19    |

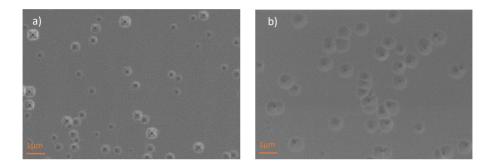

| 3.6  | Etch pit density of Ge SRB revealed by a) Iodine solution and b) Secco                                                                        |       |

|      | solution                                                                                                                                      | 20    |

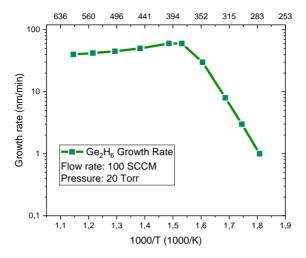

| 3.7  | Growth rate of Ge layer on Si substrate at temperatures ranging from 280°C to 600°C with digermane flow of 100 SCCM at 20 Torr                | 21    |

| 3.8  | EPD revealed by a) Secco solution and b) Iodine solution                                                                                      | 22    |

| 3.9  | XRD Omega/2Tetha scan around (004) direction of SiGe layers grown                                                                             |       |

|      | on Si substrates using silane and germane                                                                                                     | 24    |

| 3.10 | Ge content and growth rates of the SiGe layers versus temperature at                                                                          |       |

|      | $P(GeH_4)/P(SiH_4) = 0.24. \dots \dots$ | 24    |

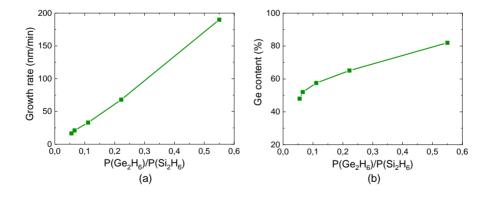

| 3.11 | Growth rate and Ge contents of SiGe layers versus PPR of germane to silane                                                                    | 25    |

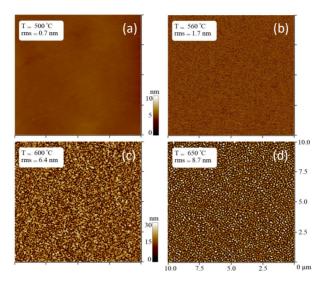

| 3.12 | 10 μm×10 μm atomic force microscopy (AFM) images of the SiGe surfaces grown at $P(GeH_4)/P(SiH_4) = 0.24$ in a temperature range of (a)       |       |

|      | $500^{\circ}$ C, (b) $560^{\circ}$ C, (c) $600^{\circ}$ C, and (d) $650^{\circ}$ C                                                            | 26    |

| 3.13 | Ge content and growth rate of SiGe layers as a function of $P(Ge_2H_6)/P(Si_2.6)$                                                             | $H_6$ |

|      | at 450°C and $P_{tot}$ =20 Torr                                                                                                               | 26    |

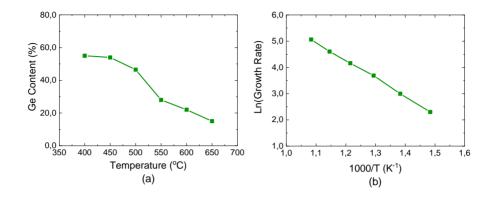

| 3.14 | The Ge content and growth rate of SiGe layers versus temperature at                                                                           |       |

|      | $P(Ge_2H_6)/P(Si_2H_6)=0.067$ and $P_{tot}=20$ Torr                                                                                           | 27    |

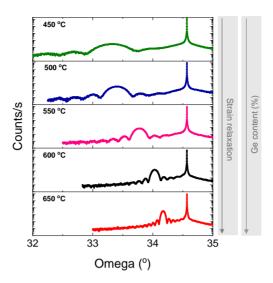

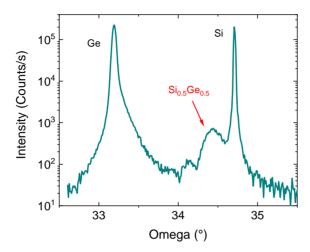

| 3.15 | XRD rocking curve of SiGe layers grown by digermane and disilane at                                                                           |       |

|      | different temperatures at $P(Ge_2H_6)/P(Si_2H_6)=0.067$ and $P_{tot}=20$ Torr.                                                                | 28    |

| 3.16 | XRD rocking curve acquired by -2 scan around (004) direction. The                                                                             |       |

|      | $Si_{0.5}Ge_{0.5}$ peak position at 34.4° and the thickness fringe to the left                                                                |       |

|      | shows that the layer is under tensile strain with a sufficiently flat inter-                                                                  |       |

|      | face with Ge SRB                                                                                                                              | 29    |

|      |                                                                                                                                               |       |

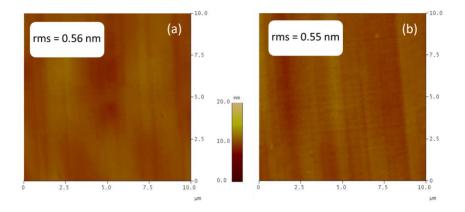

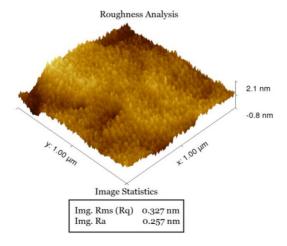

LIST OF FIGURES vii

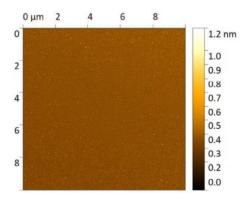

| 3.17<br>3.18 | AFM image of $Si_{0.5}Ge_{0.5}$ layer grown on Ge strain relaxed buffer. The RMS surface roughness does not change with the deposition of $Si_{0.5}Ge_{0.5}$ on top of the Ge SRB                                                                                                | 30       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0.10         | of 0.3 nm                                                                                                                                                                                                                                                                        | 30       |

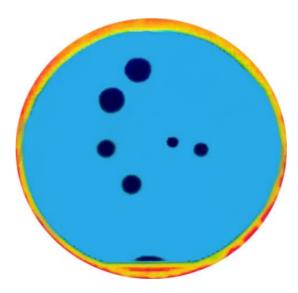

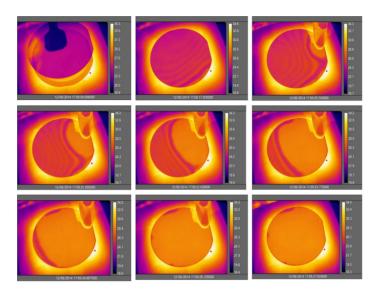

| $4.1 \\ 4.2$ | IR image of the bonded $SiO_2 - SiO_2$                                                                                                                                                                                                                                           | 36       |

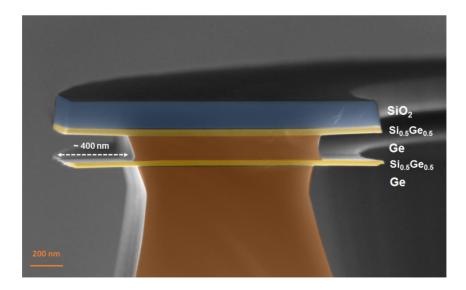

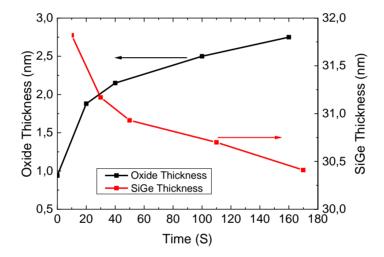

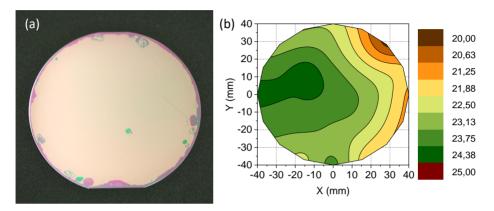

| $4.3 \\ 4.4$ | wafer                                                                                                                                                                                                                                                                            | 38<br>40 |

| 4.5          | etching                                                                                                                                                                                                                                                                          | 41       |

| 4.6          | fabricated GoI wafer with 20 nm Ge on top                                                                                                                                                                                                                                        | 42       |

|              | showing RMS below 0.5 nm                                                                                                                                                                                                                                                         | 42       |

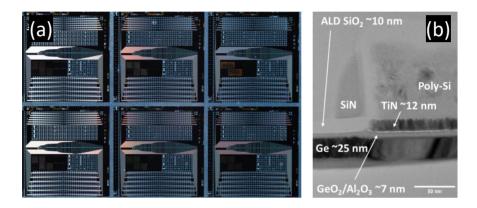

| 5.1          | Optical image of six chips fabricated on GoI substrate, b) TEM image of 0.8 µm pFET device fabricated on GoI substrate                                                                                                                                                           | 45       |

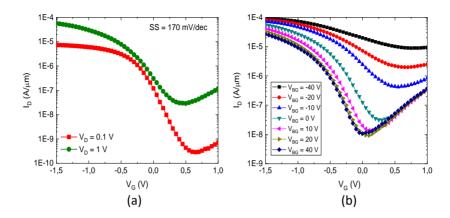

| 5.2          | a) $I_D - V_G$ characteristics of a Ge MOSFET with 0.8 µm gate length,<br>b) $I_D - V_G$ behavior under back-bias voltage of -40V to 40V                                                                                                                                         | 46       |

| 5.3 $5.4$    | a) CV curves of $Ge/Al_2O_3$ MOS capacitors, b) Carrier mobility in GoI and SoI pFET devices                                                                                                                                                                                     | 47<br>47 |

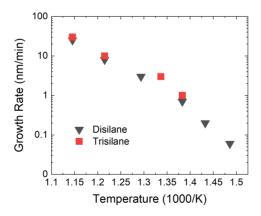

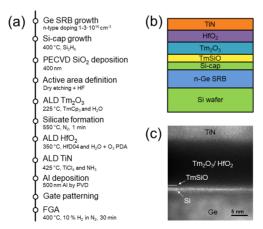

| 6.1<br>6.2   | Growth rate of Si versus temperature using silane, disilane, and trisilane a) Process flow for fabrication of MOS capacitors, b) Schematic cross-section of gate stack, and c) TEM cross-section image of fabricated gate                                                        | 51       |

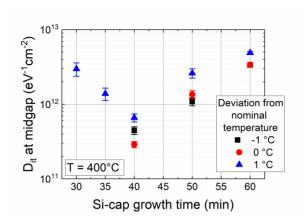

| 6.3          | stack                                                                                                                                                                                                                                                                            | 52       |

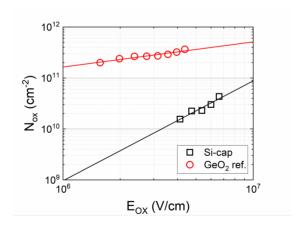

| 6.4          | of 3.75-3.8 nm                                                                                                                                                                                                                                                                   | 53       |

| 6.5          | a function of Si-cap growth time. Average over 10 measuring devices is displayed. Standard deviation is indicated with error bars Oxide trap density $N_{ox}$ extracted from CV hysteresis as function of oxide field Eox. Si-cap devices exhibit more than 20 times lower oxide | 54       |

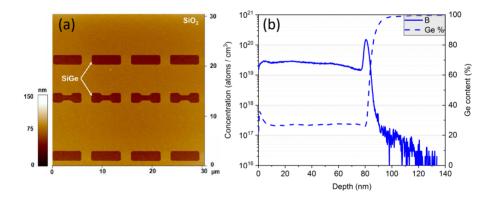

| 6.6          | trap density than reference GeOx devices                                                                                                                                                                                                                                         | 54       |

| 6.7          | selectively on Ge                                                                                                                                                                                                                                                                | 57       |

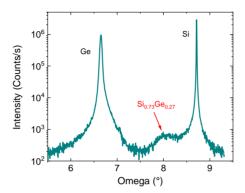

|              | Si substrate acquired by scanning omega/2tetha around (224) direction                                                                                                                                                                                                            | 58       |

## List of Tables

| 1.1 | Bulk properties of Si, Ge, and III-V semiconductors |  | • |  | • | • |  |    |

|-----|-----------------------------------------------------|--|---|--|---|---|--|----|

| 5.1 | SS comparison with literature                       |  |   |  |   |   |  | 46 |

## List of Acronyms

3D three dimensional ALD atomic layer deposition

BOX buried oxide

CDE cyclic deposition-etch

CMOS complementary metal oxide semiconductor

CV capacitance-voltage

CVD chemical vapor deposition

CVE chemical vapor etch

DCS Dichlorosilane

FET field effect transistor

FDSOI fully depleted silicon on insulator

IV current-voltage

LPCVD low pressure chemical vapor deposition M3D monolithic three dimensional (integration)

MOS metal oxide semiconductor

MOSFET metal oxide semiconductor field effect transistor

NW nanowire

PECVD plasma enhanced chemical vapor deposition

PVD physical vapor deposition RIE reactive ion etching

RPCVD reduced pressure chemical vapor deposition

RTA rapid thermal anneal

SEG selective epitaxial growth

SEM scanning electron microscope

SIMS secondary ion mass spectroscopy

SOI silicon on insulator SS subthreshold slope

STL sidewall transfer lithography

TEM transmission electron microscope

TMAH tetra-methyl-ammonium-hydroxide

## Chapter 1

## Introduction

#### 1.1 Motivation

Electronic circuits dramatically changed in the 1960s as they moved from being conventional discrete devices to be the integrated components on a single chip [1]. Integrated electronics improved the reliability and performance of these circuits even as they reduced the cost of design and fabrication. Since then, the dimensions of MOS devices have been continuously downscaled allowing for a larger number of devices per area and faster switching speed [2]. Such downscaling has increased the performance of these circuits while reducing fabrication costs. Today, however, the field of electronics is facing new challenges.

On the one hand, the scaling of devices is reaching critical dimensions in the order of several atoms. This makes further downscaling technologically difficult and economically not beneficial [3]. In turn, it makes 3D integration involving stacking different layers of devices on each other, one of the most promising methods for improving circuits' performance while keeping the costs down and avoiding atomic-scale challenges [4]. On the other hand, today, the field of electronics is no longer limited to circuits with only data processing applications [4]. IoT systems are emerging, and they require multiple functionalities on a single chip. Sensors, processors, actuators, memories, and even power storage units need to be efficiently integrated to make IoT work [5]. Stacking different device layers on top of each other is one of the most promising methods to overcome these challenges.

One of the advantages of 3D integration over 2D integration is the possibility of using different materials as the active layer in the circuit. As pFETs (p-type field effect transistors) and nFETs (n-type field effect transistors) are fabricated

on different tiers, they can be processed sequentially using different materials and techniques [4]. However, their sequential processing imposes a temperature limit on the process. The processing of the top-tier devices must be tuned such that it minimizes the damages to the bottom tier and maintains the performance of already fabricated devices in the first layer. Therefore, it is important to choose the right material for the top tier which would have high carrier mobility and low processing temperature and be compatible with Si CMOS technology.

### Ge as top tier material

Ge is one of the most promising candidates for 3D integration with Si devices. It has high carrier mobility compared to Si and a natural lower processing temperature. The first transistor invented in 1947 at the Bell Telephone Laboratories was made on a Ge block [6]. However, it was replaced by Si in the 1960s due to the many advantages of Si. High purity Si substrates were easier to produce, and Si could stand much higher temperatures. However, the main reason for replacing Ge with Si was the high stability of silicon dioxide. Ge oxide is water-soluble, which made it quite difficult to process. The formation of multiple sub oxides GexOy degraded the surface passivation capabilities and limited its application as a high K dielectric [7]. SiO2, on the other hand, could be thermally grown in a well-controlled manner and used as an efficient passivation layer for transistor fabrication. The high stability of SiO2 made Si the best material for the mass production of transistors, and that has remained so until today [8].

Recently, however, advanced gate dielectric materials have been developed using the atomic layer deposition technique. Therefore, there has been growing interest in Ge as the material for future electronics [4]. Ge has a much smaller effective mass in the heave hole (mhh) and light hole (mlh) bands compared to Si. This small effective mass leads to its potentially higher carrier mobility compared to Si. A comparison of the bulk mobilities of Si, Ge, and III-V semiconductor materials is presented in table 1. It can be seen from table 1 that Ge has considerably higher hole mobility than the other semiconductors, which enables enhancing the drive currents in Ge pFETs. By just considering the mobility values, III-V for NMOS (n-type metal oxide semiconductor) and Ge for PMOS (p-type metal oxide semiconductor) seems to be the best combination. However, the fabrication of nanoscale III-V transistors on Si platform suffers from cost and process compatibility issues.

Besides the higher carrier mobility advantage of Ge, its low-temperature processing also makes it a good candidate for M3D integration. Since Ge is a group IV material, it is compatible with Si technology and does not add any cross-contamination issues. SiGe has been already used in CMOS fabrication. Therefore, integration of Ge as the active material in the existing CMOS technology will be straightforward.

| Material/property              | Si   | Ge   | GaAs  | InAs  | InSb  |

|--------------------------------|------|------|-------|-------|-------|

| Electron Mobility $cm^2/(V.s)$ | 1600 | 3900 | 9200  | 40000 | 77000 |

| Hole Mobility $cm^2/(V.s)$ )   | 430  | 1900 | 400   | 500   | 850   |

| Bandgap (eV)                   | 1.12 | 0.66 | 1.424 | 0.36  | 0.17  |

| Dielectric Constant            | 11.8 | 16   | 12.4  | 14.8  | 17.7  |

Table 1.1: Bulk properties of Si, Ge, and III-V semiconductors

Although using Ge has many advantages for CMOS applications, its 4% lattice mismatch with Si makes it difficult to grow high-quality layers directly on Si. The low bandgap of Ge and its higher dielectric constant causes the short channel effect and high leakage current, which can be improved by using GoI substrates instead of bulk Ge. Electronic and photonic devices based on GoI have been shown to be promising solutions for addressing the current difficulties that the electronics industry is facing. However, the fabrication of large-scale thin GoI (top Ge layer <40 nm) wafers with high thickness homogeneity, low defect density, low doping level, and good interface quality is challenging.

## 1.2 Scope, objectives and achievements

This research aims to develop and investigate new methods to use Ge in the sequential fabrication of 3D integrated electronics. Fabrication of high-quality ultra-thin GoI substrate with high thickness homogeneity has been investigated in this research to expand the applications of Ge in M3D integrated circuits fabrication.

Five main objectives were defined for this thesis to address the difficulties in Ge M3D integration. These objectives constitute the main contribution of the thesis. The research objectives and the achievements are the following:

Development of Ge SRB to be used as a virtual substrate for transferring the top tier device layer on an insulator. Since the Ge layer is required to be single crystalline material with a sufficiently low density of defects, a strain relaxed Ge layer is desired to be epitaxially grown on Si substrate. The layer should have ultra-smooth surface morphology (root mean square (RMS) < 1 nm) to be bondable to the insulator layer. The threading dislocation density should be kept low for better device yield over the wafer. By using the two-step method, Ge layers with threading dislocation density (TDD) of  $10^7\ cm^{-3}$  were epitaxially grown on Si substrates. Hydrogen thermal annealing was carried out to reduce the surface roughness to values below 1 nm. These contributions are discussed in section 3.3 and paper I (listed earlier in the "List of Publications").

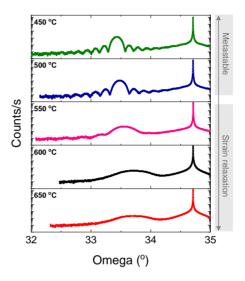

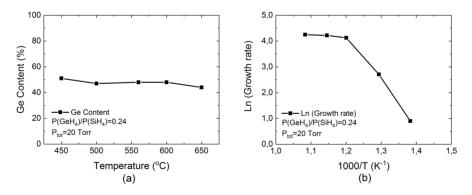

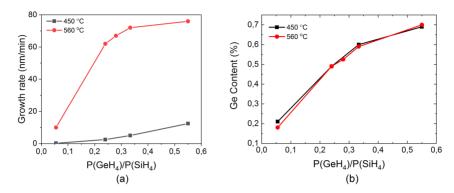

Development of epitaxial growth of fully strained SiGe thin films to be used as etch-stop layers in GoI fabrication process. To transfer the ultra-thin Ge layer to another wafer coated with an insulating material, an etch-stop layer is required, which does not add any defects or roughness to the surface. For this purpose, SiGe layers were epitaxially grown at different temperatures using silane-germane and disilane-digermane gas chemistries. As a result, a SiGe layer containing 50% Ge atoms was developed at temperatures below 450°C, which was fully strained toward Ge SRB. A highly selective etching process was developed that successfully removed microns of Ge while keeping the 20 nm transferring layer intact. The contributions are discussed in section 3.4 and paper II (listed earlier in the "List of Publications").

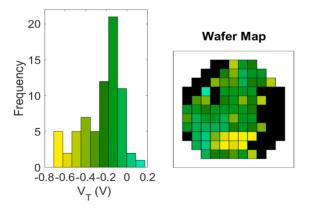

Wafer bonding and etch-back process development to be adopted for the fabrication of ultra-thin Ge on the Insulator. A wafer bonding technique and an etch-back process were required for transferring the desired Ge layer to another wafer that would be compatible with 3D integration. This process was developed through room temperature wafer bonding, a combination of wet and dry etching of Si wafer, Ge buffer, and SiGe etch-stop layers. The fabricated GoI wafers exhibited 5% thickness inhomogeneity over the whole wafer. To our knowledge, such a high thickness homogeneity was not reported in any other studies. Since no ion implantation was performed for the GoI fabrication, the residual dopant concentration was in the range of  $10^{16}cm^{-3}$  which is much lower than the range referred to in the previous reports on GoI fabrication methods. The contributions are discussed in section 4.4 and paper III (listed earlier in the "List of Publications").

Ge pFETs' fabrication process compatible with M3D. The advantages of using Ge as the top-tier device material has been discussed in section 1.1. However, the pFETs' fabrication process needs to be carried out at temperatures below 600°C for it to be compatible with M3D integration. In the course of this research, Ge pFETs' fabrication process was developed on GoI wafers. The maximum processing temperature and duration were 600°C for 60 s respectively during the dopantactivation step. Therefore, this process is fully compatible with M3D integration. The 70% yield over the wafer indicated that the wafer bonding and the etch-back process are sufficiently reliable for large-scale Ge device fabrication. Ge devices have shown 60% higher carrier mobility compared to the reference Si devices. The back-gate bias characterizations showed that the Ge/Box interface is depleted at 0 V which can be interpreted as a low-charge density at the interface and low level of residual dopants in the Ge channel. The SS of 170 mV/dec was extracted from the  $I_D - V_G$  characteristics of the GoI devices. This SS value was in the same range as it was in the other studies. The contributions are discussed in chapter 5 and paper III (listed earlier in the "List of Publications").

Development of Si passivation for improvements in Ge devices. Ge MOS field-effect transistors (MOSFETs) suffer from high oxide trap density  $(N_{ox})$ and interface trap density  $(D_{it})$  at the interface of the Ge layer and the high-K stack, which increases the SS significantly and degrades the reliability. In this thesis, the epitaxial growth of an ultra-thin Si cap layer on Ge is developed to passivate the surface and minimize the high-K dielectric degradation. The sub-nm Si cap layer is deposited at temperatures as low as 400°C and reduced pressure by using disilane precursor. The low-temperature deposition reduces the chance of strain relaxation and minimizes the interdiffusion of Si and Ge atoms at the Si/Ge interface. MOS capacitor devices were fabricated and characterized by the collaborators to electrically evaluate the Si passivation layer. The capacitors fabricated on Si passivated Ge layers shown similar behavior as the capacitors fabricated directly on Si substrate. The characterization results shown interface trap density of  $3\times10^{11}eV^{-1}cm^{-2}$ , and hysteresis as low as 3 mV at  $E_{ox}$  of 4 MV/cm corresponding to oxide trap density of  $1.5 \times 10^{10} cm^{-2}$ . The results indicate that this Si passivation layer substantially improves the gate dielectric quality and potentially reduces the SS of Ge devices while increasing their reliability. The contributions are discussed in section 6.1 and paper IV (listed earlier in the "List of Publications").

Improving the junction formation in Ge devices. High contact resistance is one of the major issues that Ge devices face. The low doping concentration levels in ion-implanted Ge and high-temperature annealing requirements make it difficult to drive a high current through Ge transistors. To address this issue, we have investigated the selective epitaxial growth (SEG) of highly doped SiGe layers in source and drain areas. The in-situ doped SiGe layer with a dopant concentration of  $2.5 \times 10^{19} cm^{-3}$  and resistivity of 3.5 m $\Omega$ cm was selectively grown on Ge to improve junction formation. PN diodes are fabricated on the heterojunction and characterized to evaluate the layers. The contributions are discussed in section 6.2 and paper V (listed earlier in the "List of Publications").

The following research milestones were achieved while carrying out the work presented in this thesis:

- Process design for fabrication of ultra-thin GoI substrate with superior thickness homogeneity.

- Epitaxial growth of Ge SRB layer on Si substrate with low TDD and smooth surface.

- Epitaxial growth of fully strained SiGe layers on Ge at low temperatures.

- Room temperature wafer bonding and low-temperature post-bonding baking to fabricate large-scale GoI substrates within the M3D integration temperature budget.

- Highly selective etching method to remove the microns of Ge without affecting the 20 nm transferring Ge layer.

- Fabrication of Ge pFETs at temperatures below 600°C with excellent electrical characteristics.

- Development of highly reliable Si passivation layer on Ge resulting in a gate stack with low  $D_{it}$  and oxide trap density.

- SEG of highly doped SiGe on Ge to form junctions in the source and drain regions.

### 1.3 Organization of the thesis

This thesis comprises seven chapters as follows:

**Chapter 1** presents the motivations behind this research. This chapter includes the scope, aims, and achievements of this research.

Chapter 2 briefly introduces 3D integration applications and methods and state-of-the-art circuits and devices.

**Chapter 3** summarizes the theoretical principles behind the epitaxial growth of Si-Ge alloys. The initial results of the epitaxial growth of Ge SRB and SiGe layers too have been presented in this chapter.

**Chapter 4** details the single-crystal Ge layer transfer and GoI substrate fabrication process during this research.

**Chapter 5** provides an analysis of the fabrication process and the electrical characterization results of Ge pFET devices fabricated on our GoI wafers.

Chapter 6 focuses on the optimization of Ge devices through Si surface passivation for better high-K material development, and SEG of highly doped SiGe to improve junction formation in the source/drain region.

Chapter 7 the concluding chapter, provides the highlights of this research and an outlook on the application of developed processes for monolithic 3D integration.

## Chapter 2

## 3D Integration

This chapter briefly introduces 3D integration and state of the art. 3D integration that is now seen as the solution for IoT device fabrication along with a discussion on the different methods for achieving 3D integrated circuits.

### 2.1 3D Integration

3D integration, as an idea, got introduced in 1964 by Texas Instruments [4]. Fujitsu demonstrated the first 3D CMOS integrated circuit in 1983, which included the stack of one type of transistor above a transistor of the opposite type [4]. However, the fabrication costs per transistor in 3D integration were much higher than in 2D miniaturization, which limited the industrial application of this method. The increase in the required investments for further 2D scaling, the need for shorter interconnects to get benefit from high-performance devices, and the introduction of new materials and technologies made 3D integrated circuits interesting again. Nowadays, applications of 3D integration technology are expanding rapidly. Some of the driving forces for 3D integrations are miniaturization, cost reduction, multifunctionality, and performance enhancement. There are three major categories of 3D stacking technologies today: using interposer, parallel through-Si-vias (TSV) integration, and monolithic sequential integration.

## 3D stacking with interposer (2.5D integration)

In this method, circuits are fabricated separately and attached to an interposer. The interposer provides interconnections between the circuits and acts as a supporting platform for multi-chip solutions. This technique permits high metal thickness but

not high density. Therefore, it is most useful for biosensing and photonic applications with low-density interconnections [9]. Typical thicknesses of interposers are in the 100  $\mu$ m range with TSV width and space of 1–10  $\mu$ m. Bumps used for connecting different chips are usually in the range of 40  $\mu$ m, while the bumps for joining the interposer are typically in 150+  $\mu$ m pitch. Figure 2.1 illustrates three chips stacked on each other of which two of the chips include TSVs. These two top chips are stacked face-to-face (F2F), while the bottom chips are joined face-to-back (F2B) [10].

Figure 2.1: Schematic of 3D stacking by using interposer

## 3D parallel integration TSVs

In this technique, circuits are fabricated on two wafers separately and planarized. Two mirror-polished wafers with metal pads (usually Cu) are aligned and put into contact with each other. Adhesive forces are usually applied at room temperature to form the necessary bonding. The circuits' electrical contacts are reached through TSVs from the backside of the wafer. This technique becomes more and more attractive because of its advantages such as no temperature limitations for separate circuits' processing and higher interconnection density compared to the flip-chip technology [10]. Nowadays, most image sensors are fabricated using this method [11]. Sony presented the first 3-layer stacked state-of-the-art CMOS image sensor at the IEEE International Electron Devices Meeting (IEDM) 2017. This chip includes pixel, memory, and image signal processor dies mounted on top of each other. They have shown that integrating memory with the logic enhanced the reading speed of the chip from 30 to 120 frame per second [12]. The interconnections pitch in this technique is 1 µm, which is limited by the wafer alignment accuracy. The misalignment between the top and the bottom pads would increase the contact resistivity and reduce the yield. Some other challenges in this technique are choosing the right materials, surface preparation, bonding strength, and metal atoms diffusion.

#### Sequential M3D

The first 2D integrated circuit introduced by Jack Kilby in 1958 was not monolithic [1]. The components were fabricated on a single piece of semiconductor, but the interconnections were made using hand soldering. In 1961, the first monolithic 2D circuit was presented by Robert Noyce in which both components and interconnections were monolithically integrated on a single piece of semiconductor [13]. The same story has got repeated in the case of 3D integration 50 years hence. The first 3D integrated circuits are separately made circuits, which are connected to each other by wires or TSVs. However, for higher interconnect density, M3D is required.

Sequential M3D is an ideal alternative to parallel stacking to increase the density of interconnections and reach few tens of nanometer pitches. In this method, the tiers are fabricated on top of each other in a sequential manner. Thus, the M3D process has the following five main steps:

- Step 1: The first-tier transistors are fabricated on a Si or SoI substrate followed by metallization and contact formation. The first-tier transistors are fabricated on a Si or SoI substrate followed by metallization and contact formation.

- Step 2: The surface is passivated with an insulator material and planarized using chemical mechanical polishing (CMP).

- Step 3: The wafer is bonded to another wafer for active layer transfer. The second wafer is called a sacrificial wafer. It contains the active layer of the second-tier devices.

- Step 4: The active layer is transferred to the insulating material, and the sacrificial wafer is removed.

- **Step 5:** The second-tier devices are fabricated directly on top of the first-tier devices, and the circuits are interconnected through conventional photolithography, etching, and metallization.

This process can be continued with several tiers to add higher devices and functionalities to the 3D integrated chip. Since the same alignment marks can be used for the fabrication of different tiers, lithography alignment precisions of a few nm can be achieved. This high alignment accuracy range enables via densities of more than 100 million/mm2 between different tiers. Since the nFETs and pFETs are fabricated separately, it is possible to use several materials and technologies for the transistors' performance improvements. For instance, channel materials with higher carrier mobility can be used. Substrate orientation and strain level

can be different, and various technologies such as FinFET, fully depleted siliconon-insulator (FDSoI), and nanowire transistors can be built on top of each other. However, some benefits do not come without attendant troubles.

The major limitation of sequential 3D integration is the thermal budget of top tiers' fabrication. A reasonable max process temperature is determined to be around 500°C for 2 hours, which can be increased to 600°C if the duration would be lesser [14]. Thermal stability of silicide and metal gate function are the bottlenecks for high-temperature processing. Therefore, the top-tier materials and processing must be chosen correctly to prevent degradation of the bottom-tier transistors while achieving excellent top-tier transistor performance. Ge and III-V materials are considered good candidates for top-tier transistors channel material because of their considerably higher carrier mobility and lower processing temperature compared to Si [15]. Stacking InGaAs nFET on top of SiGeOI pFET is one of the best examples of high-performance CMOS circuits made through sequential 3D integration [16], [17]. In the case of using Si as the active layer of the top-tier transistors, new techniques such as laser annealing and solid phase epitaxy are required to keep the bottom tier circuits intact [18], [19].

One of the main challenges in sequential 3D integration is the formation of top-tier channel material. This layer can be achieved by either polycrystalline material deposition followed by recrystallization or direct wafer bonding and layer transfer. Layer transfer is usually more complicated compared to polycrystalline material deposition, and more processing steps are required. However, it has many advantages arising from the single crystallinity of the layer, which compensates for the difficulties.

In this thesis, Ge is investigated as one of the most promising candidates for M3D integration on the Si platform. The reason for choosing Ge is the higher carrier mobility compared to alternative semiconductor materials and the ability to process Ge devices at low temperatures. To monolithically integrate Ge on the already processed Si devices, a unique stack of Si/Ge/SiGe/Ge was epitaxially grown on Si substrates. Low-temperature processes are developed for wafer bonding, etch-back, Ge pFET fabrication, and device performance enhancements. The process steps are discussed in detail in the next chapters.

## Chapter 3

## Epitaxial growth of Ge and SiGe

Epitaxial growth of Ge, SiGe, and Si layers is discussed in this chapter. The basic concepts behind epitaxial growth are explained with a focus on growth kinetics, and strain relaxation. The layers developed at this step have been used later for the fabrication of Ge on the insulator layer and for Ge pFETs' performance improvements.

## 3.1 Epitaxy

The term epitaxy has a Greek root meaning "arranged on". It was first used by Royer in 1928. It is defined as oriented growth of a single crystal material arranged upon a single crystal substrate. The mechanism behind epitaxy is that of lowering the internal energy of the system by aligning the atoms of the guest crystal following the same crystal orientations as the host crystal. This enables the growth of exceptionally high-quality crystalline materials without increasing the defect density of the substrate.

Epitaxial growth can be either homoepitaxy if the layer and substrate are the same materials, or hetroepitaxy if the substrate and layer are different materials. Many different techniques have been developed for the epitaxial growth of high-quality materials. Among them, the two most used methods for the epitaxial growth of group IV semiconductors are molecular beam epitaxy (MBE) and chemical vapor deposition (CVD). In MBE, the source materials are evaporated from heated cells and collimated in a single beam before directing them toward the surface of the substrate. MBE is a flexible method as, in it, the growth parameters can be changed independently. However, this flexibility comes with other limitations such as a low deposition rate which limits MBE's application mainly to research purposes. CVD has a much higher throughput compared to MBE, which makes it a popular method for the deposition of a wide range of materials. Currently, it is the most used method

for epitaxial growth of semiconductor materials because it affords high thickness and composition homogeneity, and reproducibility concerning the wafer and over time (wafer-to-wafer).

In CVD, preheated substrates are exposed to precursors in the gas phase, and the desired layers are grown. Since the reactants are chemically stable at room temperature, the deposition is limited only to the heated zones. Chemical reactions determine the composition and the deposition rates of the layers. Therefore, many parameters such as pressure, temperature, and precursor flow control the layer quality, deposition rate, and compositions of CVD. There are many different CVD processes such as low-pressure CVD (LPCVD), reduced pressure CVD (RPCVD), plasma-enhanced CVD (PECVD), and ultra-high vacuum CVD (UHCVD).

There are two types of reactions that happen during epitaxial growth in a CVD process: gas-phase (homogeneous) and solid-surface (heterogeneous) reactions. A homogeneous reaction happens when the source gasses decompose before reaching the surface and produce solid products. The synthesized particles land on the substrate's surface after the reaction causing defects and poor uniformity. Therefore, in our CVD process, gas-phase reactions were not desirable. In a heterogeneous reaction, the reactant molecules are diffused to the surface where the reaction happens, and the desired materials are grown epitaxially. In our process, the layers grown in heterogeneous reactions were more uniform and desired.

The following are two main parameters in a simplified CVD process mechanism:

• Reactant molecules' diffusion to the surface in the gas phase.

$$J_1 = D\frac{dC}{dx} \approx \frac{D_g}{\delta}(C_g - C_s) = h_g(C_g - C_s)$$

(3.1)

Where  $J_1$  is the flux of the reactant molecules in gas phase to the substrate surface, D is the diffusion constant of the reactant gasses,  $C_g$  is the concentration of reactant molecules in the bulk gas,  $C_s$  is the concentration of reactant molecules on the surface,  $\delta$  is the thickness of the boundary layer, and  $h_g$  is the mass transfer coefficient.

• Adsorption of the reactant molecules on the surface.

$$J_2 = K_s C_s \tag{3.2}$$

Where  $J_2$  is the flux of reactant molecules in the reaction site,  $K_s$  is the reaction rate constant,  $C_s$  is the concentration of reactants on the surface.

The by-products need to be desorbed from the surface after the reaction and diffused from the surface to the gas-phase to be removed from the reactor. When

3.1. EPITAXY 13

the deposition rate is limited by the surface reaction, these two steps can be ignored, and a steady-state can be achieved. In the steady-state, the two fluxes are equal to the steady-state flux, which can be calculated as shown below:

$$J_{SS} = k_T C_q \tag{3.3}$$

Where  $k_T$  is the overall rate constant defined by the mass transfer coefficient  $(h_q)$  and the surface reaction rate constant  $(k_s)$ :

$$k_T = \frac{h_g k_S}{h_g + k_S} \tag{3.4}$$

At high temperatures  $k_s > h_g$  which results in  $k_T \approx h_g$  which means the reaction is in diffusion controlled regime. In the case of low-temperature processing, however,  $k_s < h_g$  which corresponds to  $k_T \approx K_s$  and the reaction will be in surface reaction controlled regime. This temperature effect is mainly due to exponential variation of surface reaction constant with temperature versus small variation of diffusivity by temperature ( $\alpha T^{3/2}$ ).

Therefore, the growth rate is highly temperature dependent in the reaction controlled regime. The deposition rate of a film with N number of atoms and the overall deposition rate can be calculated from 3.5 and 3.6.

$$G = \frac{J_{SS}}{N} \tag{3.5}$$

$$G_{tot} = \frac{k_T}{N} (\frac{1}{KT}) P_g \tag{3.6}$$

where  $P_g$  is the partial pressure of the reactant gasses, and K is the Boltzmann constant.

In this thesis, two different layers are epitaxially grown on Si substrate to be used for fabrication of ultra-thin Ge on insulator layer for 3D integration application. The first layer consists of a strain-relaxed Ge layer grown directly on the Si substrate. The second layer is a SiGe layer that is epitaxially grown on the Ge layer to be used as an etch-stop layer in the GoI fabrication process. There are two important parameters for the transferring layer to achieve a high process yield and sufficiently good quality material for device fabrication. These parameters are low surface roughness (below 1 nm) and low defect density. The epitaxial stack shown in figure 3.1 was designed to achieve high crystal quality with a defect density of  $1 \times 10^{17} cm^{-2}$  and surface roughness below 1 nm.

This chapter details reduced pressure chemical vapor deposition (RPCVD) of Ge buffer, SiGe etch-stop, doped SiGe contact, and Si cap layers. The epitaxial growth and effects of parameters such as precursors, deposition temperature, thermal annealing, and thickness have also been discussed in detail.

Figure 3.1: Schematic of the epitaxial stack for wafer bonding and Ge layer transfer on insulator

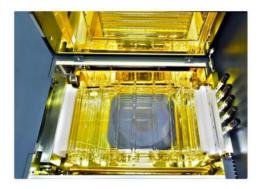

### 3.2 ASM Epsilon 2000 Reactor

ASM Epsilon 2000 is a single wafer RPCVD tool equipped with a load-lock and wafer handling unit. The wafer handling unit and the load-locks are purged with nitrogen (N) to minimize surface oxidation and oxygen contamination. The wafer handling uses a Bernoulli wand to transfer wafers from the loading cassette to the processing chamber and from the processing chamber to the unloading cassette. In the process chamber, which is made of quartz, the wafers are placed on a silicon carbide coated susceptor which is heated by using lamps from the top and the bottom. The process chamber of Epsilon is shown in figure 3.2.

The gas module handles two Ge sources, four Si sources, two dopant gasses, one tin source,  $HCl, H_2, andN_2$ . Silane, disilane, trisilane, and dichlorosilane (DCS) are the Si sources. Germane and digermane are the Ge sources. P-type and N-type doping are obtained by diborane and phosphine gasses respectively.  $H_2andN_2$  are used as charrier gasses. HCl can be used in high flow for cleaning the reactor or in low flow for SEG. Each gas line can go to the vent or the reactor separately, which offers the option of depositing different materials on top of each other in a single epitaxial growth step. The processes can be carried out either at reduced pressures (10–100 Torr) or at atmospheric pressure.

The susceptor is heated through radiation from Tungsten-halogen lamps. Therefore, the susceptor's temperature is much higher than the rest of the reactor, and a major part of the reaction happens on the wafer. The temperature is measured through five thermocouples placed in the center, sides, front, and end of the susceptor area. The thermocouples are connected to temperature-controlling units which adjust the power supplied to the lamps separately for each of them so that they

can reach the temperature set-point homogenously over the wafer. The process temperature can be precisely controlled between 200°C and 1,200°C.

Figure 3.2: Photo of the quartz chamber of ASM Epsilon 2000

### 3.3 Epitaxial growth of Germanium SRB on Si(001)

Heteroepitaxial growth can be classified into three distinct modes which have been detailed in the following paragraph. Growth mode mainly depends on two parameters, i.e., the lattice mismatch between the growing layer and the substrate and the balance between the free energy of substrate  $(\sigma_s)$ , layer  $(\sigma_L)$ , and the interface  $(\sigma_i)$ .

The Frank-Van der Merwe growth mode is the case where the free energy of the substrate is higher than the free energy of the layer and the interface. In this mode, the single crystalline film is grown layer-by-layer on top of the substrate. It is also called 2D growth. The Volmer-Weber growth mode is the one where the free energy of the substrate surface is lower than the layer and the interface. Therefore, the adatoms bond to themselves to have the minimum free energy and form 3D islands that cause rough surfaces. The third growth mode is the Stranski-Krastanov (SK) mode. It is a combination of both 2D and 3D growth modes. In this case, the growth begins with the 2D layer formation and continues with 3D growth and formation of islands due to gradual strain accumulation. SK is the main mode for epitaxial growth of Ge layers on Si substrate [20].

Ge, with a lattice constant of 5.530 Å, has a 4% lattice mismatch with Si having a lattice constant of 5.530 Å. This lattice mismatch makes it difficult to grow smooth single-crystalline layers having less defect density. The critical thickness of Ge on Si is reported to be less than 9 atomic monolayers and depends on the growth conditions. The first few monolayers of Ge on Si will be compressively strained since the layer's in-plane crystal lattice matches the substrate. However, by growing Ge

layers thicker than the critical thickness, the layer loses the strain gradually through defect formation. By continuing the growth, these defects penetrate through the film and generate threading dislocations that degrade the crystalline quality and electrical properties of the material. Besides the defect formations, the 3D island growth of Ge on Si increases the surface roughness that degrades device performance. Several different techniques have been proposed and developed to improve the surface roughness and lower the defect density. These techniques include graded SiGe buffer layers [21, 22, 23], two-step growth (low temperature and high temperature), and thermal annealing.

## Two step Ge epitaxial growth on Si

The two-step method was proposed in 1998 by Colace et al. [24] and further developed by Hartman et al. and Luan et al. [25, 26, 27]. In this method, first, a Ge seed layer is deposited at low temperature (LT) (below 400°C) and then a second Ge layer is grown on the seed layer at higher temperatures (HT) (above 550°C).

In the low temperature step, 50–100 nm Ge layer is grown on Si surface to gradually release the 4% misfit stress through misfit dislocations formation. The surface mobility of Ge atoms is substantially low at temperatures below  $400^{\circ}$ C. This lower atom mobility leads to 2D growth morphology instead of 3D and lowers surface roughness compared to high temperature growth [28]. The seed layers grown at this step have a high density of threading dislocations in the orders of  $10^{12} cm^{-2}$ . Therefore, they are not suitable for electronics applications at this stage.

In the second step, Ge layers are grown at temperatures above 600°C to achieve higher crystal quality and faster deposition rates. By growing thicker Ge layers, threading dislocations collide and eliminate each other. As a result, growing thicker layers reduces the level of TDD [29]. However, the thickness cannot be increased more than five microns as the Ge layer has a slight tensile strain and bends the Si wafer. Therefore, post-cycle thermal annealing has been proposed to improve the crystal quality and surface roughness [29]. During cycle thermal annealing, the temperature is increased up to 900°C and reduced to 100°C several times. Yamamoto et al. [29] have shown that by choosing the right temperatures and thickness, it is possible to reduce defect densities to  $7 \times 10^5 cm^{-2}$  while keeping the surface roughness below 1 nm (figure 3.3). However, thicknesses as high as 4.5 µm are required.

In this thesis research, a two-step process followed by thermal annealing was used for epitaxial growth of the Ge buffer layer with sufficiently high crystal quality. Two commercially available gas sources, germane and digermane, were used for the epitaxial growth of Ge layers. These layers were thermally annealed at 850°C

directly after growth to reduce the defect density to  $10^7 cm^{-2}$ . The results of the growth conditions and material characterizations have been presented in this chapter.

Figure 3.3: TDD vs Ge thickness [30].

## Pre-Epitaxy treatment

The surface of the wafers must be perfect and without any contaminations to achieve high-quality epitaxial growth. Basically, an epitaxy-ready surface needs to be free from oxide films, contaminations, and etched-surface damages. The best choice for surface preparation is performing both ex-situ and in-situ cleanings. Different processes for wafer cleaning have been presented in [30]. One of the most common choices for ex-situ cleaning is treatment in a "Piranha"  $(H_2SO_4:H_2O_2)$  solution to oxidize the surface and remove organic contaminations. The process is followed by hydrofluoric acid (HF) treatment to remove the native oxide and particles on the surface. The in-situ surface treatment can be performed at different temperatures and gas ambient conditions. Using hydrogen at elevated temperatures is the most common in situ treatment for group IV materials growth. This step can be skipped if cluster tools with in situ wet cleaning stations are being used [31].

For this research, the layers were grown on 100 mm Si wafers that were submerged in a "Piranha" bath for 15 min, rinsed in di-water, and dipped in an HF solution before loading to the nitrogen purged load-lock. Substrates were in-situ hydrogen baked at 1,050°C for 10 seconds. This prebaking step was enough to remove all oxygen and carbon contaminations that remained on the surface. In the case of Ge wafers and pre-processed wafers, 800°C and 950°C for 15 min were enough to prepare a clean surface for epitaxial growth. Ge buffer layers were grown by using

both germane and digermane sources for comparison. In paper 1, we have detailed our investigation of two Ge SRBs which were grown with a two-step method by varying the seed layer growth temperature.

#### 3.3.1 Germanium growth using germane

Germane is the most used gas for Ge and SiGe layer depositions. It is in the gas phase at room temperature and is usually diluted with either  $H_2$  or  $N_2$ . For this research, 10% germane in  $H_2$  was used for epitaxial growth of Ge buffers. During the growth and baking steps, the pressure was constantly kept at 20 Torr. Ge layers were grown in two-step processes with the first layer at 400°C and the second layer at 600°C followed by thermal annealing in a hydrogen ambient condition. Ge layers were grown directly on Si at temperatures ranging from 350°C to 600°C for the development of the seed layer. The flow of germane was kept constant at 400 SCCM during the growth step. Figure 3.4 shows the deposition rate versus temperature. The results show that by increasing the temperature from 350°C to 400°C, the growth rate sharply increased from 5 nm/min to 37 nm/min. This growth rate enhancement indicates that the process is controlled by the reaction at these temperatures. However, at a temperature higher than 425°C, the growth rate is not significantly changed by temperature. This shows that the process, at this point, is controlled by the gas flow at these temperatures.

**Figure 3.4:** Ge growth rate versus temperature with germane flow of 400 SCCM at 20 Torr

From the experimental data,  $400^{\circ}$ C was chosen for low temperature growth and  $600^{\circ}$ C was chosen for the high temperature growth. A 100 nm Ge seed layer was grown at  $400^{\circ}$ C followed by ramping up the temperature to  $600^{\circ}$ C in hydrogen ambient conditions with the rate of  $50^{\circ}$ C/min. The second Ge layer with a thickness of 2 µm was deposited at  $600^{\circ}$ C on top of the seed layer. After the growth, the temperature was increased gradually to  $850^{\circ}$ C, and the sample was hydrogen baked at this temperature for 10 min. Hydrogen baking smoothens the surface of the Ge layer and reduces its defect density. The layers were characterized by high-resolution X-ray diffraction (HRXRD) rocking curve and reciprocal space mapping to investigate the crystallinity and the residual strain level. Secco solution consisted of 1 part of  $K_2Cr_2O_7$  0.15 M, 2 parts of HF (49%), and 3 parts  $H_2O$  [32, 33], and the Iodine solution consisted of  $[CH_3COOH(65mL)|HNO_3(20mL)|HF(10mL)|I_2(30mg)]$  [34, 35]. These were used for the delineation of threading dislocations, and the defect density was measured from optical microscope and images from scanning electron microscope (SEM).

The XRD rocking curve of the Ge layer grown on Si can be seen in figure 3.5. It indicates that the layer is under 0.15% tensile strain. This amount of strain is due to the lower thermal expansion coefficient of Si  $(2.6 \times 10^{-6}C^{-1})$  compared to Ge  $(5.9 \times 10^{-6}C^{-1})$ . The Ge layer is grown strain relaxed on Si at high temperature, but during its cooling to room temperature, Ge shrinks faster than Si and becomes tensile strained. The right side of the Ge peak has some broadening. This is because of the interdiffusion of Si and Ge atoms at the interface, which results in a Ge-rich SiGe layer between Si and Ge.

Figure 3.5: XRD Omega/2Tetha scan around (004) direction of Ge buffer layer on Si

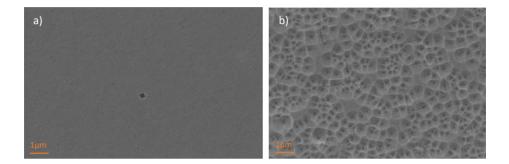

Similar TDD of  $2\times 10^7 cm^{-2}$  was delineated after the etching in Secco and Iodine solutions. Scanning electron microscope (SEM) images of the surface topography after defect selective etching are shown in figure 3.6. For further improvement of the crystal quality, the Ge buffer layers were grown on Si substrates by using digermane as the Ge precursor.

Figure 3.6: Etch pit density of Ge SRB revealed by a) Iodine solution and b) Secco solution

#### 3.3.2 Ge growth using digermane