# Sequential 3D Integration - Design Methodologies and Circuit Techniques

PANAGIOTIS CHAOURANI

Doctoral Thesis in Information and Communication Technology School of Electrical Engineering and Computer Science KTH Royal Institute of Technology Stockholm, Sweden, 2019

TRITA-EECS-AVL-2019:54 ISBN 978-91-7873-228-9 KTH School of Electrical Engineering and Computer Science (EECS) Division of Electronics Kistagången 16 SE-164 40 Kista SWEDEN

Akademisk avhandling som med tillstånd av Kungl Tekniska högskolan framlägges till offentlig granskning för avläggande av doktorsexamen i Informations- och Kommunikationsteknik fredagen den 30 augusti 2019 klockan 13.00 i Sal C, Kungl Tekniska högskolan, Kistagången 16, Kista, Stockholm.

© Panagiotis Chaourani, August 2019

Tryck: Universitetsservice US AB

To my family

#### Abstract

Sequential 3D (S3D) integration has been identified as a potential candidate for area efficient ICs. It entails the sequential processing of tiers of devices, one on top the other. The sequential nature of this processing allows the inter-tier vias to be processed like any other inter-metal vias, resulting in an unprecedented increase in the density of vertical interconnects. A lot of scientific attention has been directed towards the processing aspects of this 3-D integration approach, and in particular producing high-performance top-tier transistors without damaging the bottom tier devices and interconnects. As far as the applications of S3D integration are concerned, a lot of focus has been placed on digital circuits. However, the advent of Internet-of-Things applications has motivated the investigation of other circuits as well.

As a first step, two S3D design platforms for custom ICs have been developed, one to facilitate the development of the in-house S3D process and the other to enable the exploration of S3D applications. Both contain device models and physical verification scripts. A novel parasitic extraction flow for S3D ICs has been also developed for the study of tier-to-tier parasitic coupling.

The potential of S3D RF/AMS circuits has been explored and identified using these design platforms. A frequency-based partition scheme has been proposed, with high frequency blocks placed in the top-tier and low-frequency ones in the bottom. As a proof of concept, a receiver front-end for the ZigBee standard has been designed and a 35% area reduction with no performance trade-offs has been demonstrated.

To highlight the prospects of S3D RF/AMS circuits, a study of S3D inductors has been carried out. Planar coils have been identified as the most optimal configuration for S3D inductors and ways to improve their quality factors have been explored. Furthermore, a set of guidelines has been proposed to allow the placement of bottom tier blocks under top-tier inductors towards very compact S3D integration. These guidelines take into consideration the operating frequencies and type of components placed in the bottom tier.

Lastly, the prospects of S3D heterogeneous integration for circuit design have been analyzed with the focus lying on a Ge-over-Si approach. Based on the results of this analysis, track-and-hold circuits and digital cells have been identified as potential circuits that could benefit the most from a Ge-over-Si S3D integration scheme, thanks to the low on-resistance of Ge transistors in the triode region. To improve the performance of top-tier Ge transistors, a processing flow that enables the control of their back-gates has been also proposed, which allows controlling the threshold voltage of top-tier transistors at runtime.

**Keywords:** Sequential 3D integration, monolithic inter-tier vias, design platforms, parasitic extraction flows, RF/AMS circuits, inductors, heterogeneous integration, germanium transistors.

#### Sammanfattning

Sekventiell 3D (S3D) teknologi är en potentiell kandidat för att tillverka area effektiva integrerade kretsar (IC). Sekventiell 3D teknologi innebär sekventiell tillverkning av transistorer i lager ovanpå varandra. Den sekventiella tillverkningen möjliggör elektriska kontakter mellan transistorlagren på samma sätt som elektriska kontakter normalt tillverkas mellan metallager, vilket ger exceptionellt hög densitet av vertikala kontakter mellan transistorlagren. Forskningen har fokuserat på att utveckla processteknologin för S3D och i synnerhet etablera högpresterande transistorer i högre lager utan att degradera prestandan hos transistorer i de undre lagren. Vad gäller applikationerna för S3D-integration har mycket fokus varit inriktat på digitala kretsar. Med ökningen av Internet-of-Things applikationer så motiveras forskning på andra kretsar också.

Som ett första steg har två S3D designplattformar utvecklats, en för att stödja utvecklingen av KTH's egna S3D process och den andra för att utforska potentialen för olika S3D applikationer. Båda designplattformarna innehåller komponentmodeller och fysikaliska verifikationsverktyg. Ett nytt extraktionsflöde för parasit resistanser, kapacitanser och induktanser i S3D ICs har också utvecklats för att studera kopplingen mellan transistorlagren.

Potentialen för S3D RF/AMS kretsar har undersökts och identifierats med hjälp av dessa designplattformar. En frekvensbaserad uppdelning har föreslagits, med högfrekventa block placerade i topplagret och lågfrekvens block i bottenlagret. Som "proof-of-concept" designades en mottagare för ZigBee standarden och en 35% areareduktion erhölls utan att prestanda degraderade.

För att ytterligare utforska S3D RF/AMS-kretsar, så utfördes en studie av induktanser i S3D teknologin. Planara spolar identifierades som den mest optimal konfiguration för S3D-induktanser och olika sätt att förbättra deras prestanda undersöktes. Dessutom förslås en uppsättning riktlinjer för att kunna placera kretsblock i bottenlagret, under en induktor i topplagret, för att erhålla en kompakt S3D integration. Dessa riktlinjer tar hänsyn till frekvensen och typen av komponenter som placeras i botten lagret.

Slutligen har möjligheten för kretsdesign med heterogen S3D integration analyserats med fokus på Ge transistorer i ett övre lager och Si transistorer i ett undre lager. Baserat på resultaten av denna analys, så har "track-and-hold" kretsar och digitala celler identifieras som potentiella kretsar som kan få mest nytta av ett Ge över Si S3D-integrationflöde. Detta tack vare Getransistorernas låga resistans i triodregionen. För att förbättra prestanda hos Ge transistorerna i topplagret, så har ett processflöde föreslagits som möjliggör elektrisk kontroll av Ge kanalen från en elektrod under Ge kanalen, vilket tillåter att tröskelspänningen hos Ge transistorerna kan kontrolleras under drift.

**Nyckelord:** Sekventiell 3D integration, design plattformar, parasitiska extraktionsflöden, RF/AMS-kretsar, induktorer, heterogen integration, germanium transistorer

#### Acknowledgements

First and foremost, I would like to express my deepest gratitude for my main supervisor, Professor Ana Rusu, for entrusting me with a position at her research group at KTH. The past five years, it has been a real honor to collaborate with her. Her supervision has left a clear impact on the way I perceive things, not only in the academic world, but also in life. She has tirelessly provided me with her help and guidance, and inspired me to always strife for the best. I will be always indebted to her.

My gratitude extends also to my co-supervisor, Assistant Professor Saul Rodriguez. His advices on circuit-design aspects have been of great value to me. I am also grateful for his continuous positive attitude that has instilled to me the desire to never give up.

Special thanks to my other co-supervisor, Docent Per-Erik Hellström for his precious help in topics related to process integration and device physics. Everything I know on these two fields, I owe them to him. I am also grateful for our collaboration is setting up the design platform for the in-house process. My appreciation extends to Professor Mikael Östling for leading the Ge3D research project I was working for during my PhD studies. I am also thankful to Professor Gunnar Malm for his precious help in topics related to device physics and TCAD simulations.

This thesis would have been impossible without the financial support of the Swedish Foundation for Strategic Research (Stiftelsen för Strategisk Forskning, SSF).

My appreciation goes to Liviu Popa and Satyabrata Ghosh from Cadence® for their invaluable help in setting up a S3D parasitic extraction flow. I am also thankful to Lars Riekehr from Ångström Laboratory for the cross-section photos of the in-house vias and devices. Laura Žurauskaitė from KTH is acknowledged for providing me with the measurement data of the in-house devices, as well as for the top-view photos of them.

I am deeply thankful to Professor Spyridon Nikolaidis, from Aristotle University of Thessaloniki, Greece for the opportunities he provided me with during my Bachelor and Master studies, and his guidance during my master thesis. I would also like to thank Professors Stylianos Siskos and Theodore Laopoulos for introducing me to the world of electronics.

My gratitude extends to my colleagues from the Integrated Circuits group at KTH for the great moments we passed together. Dr Sha Tao, Dr Tingsu Chen, Dr Janko Katic, Dr Nikola Ivanisevic, Muhammad Waqar Hussain, Dagur Ingi Albertsson, I will be always grateful for our discussions and our joyful breaks from the everyday routine. Special thanks to Dr Raul Onet. His eagerness to help and assist others has been really inspiring for me.

I am also thankful to all my colleagues from the division of Electronics at KTH, Dr Ali Asadollahi (Pooria), Ahmad Abedin, Kostas Garidis, Laura Žurauskaitė, Dr Hossein Elahipanah, Dr Ganesh Jayakumar, Dr Shuoben Hou, Viktoriia Mishukova, Szymon Sollami Delekta, Mattias Ekström, Muhammad Shakir, Corrado Capriata,

Babak Taghavi, Dimitris Stathis and Yang Yu. I will always cherish the time we passed together.

It is a huge honor for me to have Professor Georges Gielen as the opponent at my defense. I am looking forward to discussing the results of my thesis with him. I am also grateful to Professor Christian Fager from Chalmers University, Associate Professor Adriana Serban from Linköping University, and Associate Professor Joachim Rodrigues from Lund University for accepting the invitation to participate in my grading committee. My gratitude extends to Professor Carl-Mikael Zetterling from KTH for reviewing my thesis. His feedback and constructive suggestions have contributed to the improvement of this work.

I could not stress more my gratitude to my family: my mother Maria, my father Ilias, my sister Adlida, my grandmother Alexandra, my aunt Sophia and my uncle Yiannis. They have been always there for me and they have provided me with their unconditional love and support. I am deeply grateful for the sacrifices they have endured to provide me with everything I needed. Of course, I would also like to thank my good friends Mezes, Oliver, Vito, Buddy, Daphne and Clara for always cheering me up.

Ultimately, I would like to thank my dear wife Pinelopi. Her support and love were crucial for me to complete this thesis. She has always helped me to overcome every obstacle I encountered, not only during my PhD studies, but at every other aspect of our common life. I cannot imagine my life without her.

Panagiotis Chaourani, Stockholm, August 2019

## Contents

| $\mathbf{C}$ | onter  | $_{ m nts}$ |                                                 | ix  |

|--------------|--------|-------------|-------------------------------------------------|-----|

| Li           | ist of | Figur       | es                                              | xii |

| Li           | ist of | Table       | ·s                                              | xvi |

| Li           | ist of | Acror       | nyms                                            | xix |

| 1            | Intr   | oduct       | ion                                             | 1   |

|              | 1.1    | New I       | Directions for Moore's Law                      | 1   |

|              | 1.2    | 3D In       | tegration Technologies                          | 4   |

|              | 1.3    | Motiv       | ration                                          | 6   |

|              | 1.4    | Resea       | rch Objectives                                  | 7   |

|              | 1.5    |             | rch Contributions                               | 8   |

|              | 1.6    | List o      | f Publications                                  | 9   |

|              | 1.7    | Thesis      | s Organization                                  | 10  |

| <b>2</b>     | Insi   | ghts i      | nto the processing of 3D ICs                    | 13  |

|              | 2.1    | TSV 1       | processing options                              | 13  |

|              |        | 2.1.1       | Via-first TSVs                                  | 13  |

|              |        | 2.1.2       | Via-last TSVs                                   | 14  |

|              |        | 2.1.3       | Via-middle TSVs                                 | 16  |

|              |        | 2.1.4       | Comparison between via-middle and via-last TSVs | 17  |

|              | 2.2    | Issues      | s with TSV processing                           | 18  |

|              |        | 2.2.1       | Copper contamination                            | 18  |

|              |        | 2.2.2       | Stress-related issues                           | 19  |

|              | 2.3    | Stacki      | ing Techniques with TSVs                        | 22  |

|              |        | 2.3.1       | Die-to-Die bonding                              | 23  |

|              |        | 2.3.2       | Direct Wafer bonding or Wafer-to-Wafer bonding  | 23  |

|              |        | 2.3.3       | Die-To-Wafer bonding                            | 24  |

|              | 2.4    | Seque       | ential 3D Integration                           | 25  |

|              |        | 2.4.1       | Si over Si                                      | 26  |

|              |        | 2 4 2       | Heterogeneous S3D Integration                   | 20  |

x CONTENTS

|   |                | 2.4.3 S3D integration of Ge FETs over Si-FETs                |

|---|----------------|--------------------------------------------------------------|

|   | 2.5            | Heat Dissipation in 3D ICs                                   |

|   | 2.6            | Summary                                                      |

| 3 | $\mathbf{Seq}$ | uential 3D Design Platform for Custom Integrated Circuits 37 |

|   | 3.1            | Sequential 3D Design Platforms                               |

|   |                | 3.1.1 Overview                                               |

|   |                | 3.1.2 Custom IC Design Platforms                             |

|   | 3.2            | KTH-S3D PDK                                                  |

|   |                | 3.2.1 KTH-S3D process stack                                  |

|   |                | 3.2.2 KTH-S3D PCELLs                                         |

|   |                | 3.2.3 KTH-S3D Device Models                                  |

|   |                | 3.2.4 KTH-S3D Physical Verification                          |

|   |                | 3.2.5 KTH-S3D parasitic extraction flow 47                   |

|   |                | 3.2.6 Digital Cells Library                                  |

|   | 3.3            | S3D Predictive PDK                                           |

|   |                | 3.3.1 S3D PPDK Process Stack                                 |

|   |                | 3.3.2 S3D-150 nm PPDK Devices and PCells 57                  |

|   |                | 3.3.3 S3D-150nm PPDK Device Models                           |

|   |                | 3.3.4 S3D PPDK Physical Verification 62                      |

|   |                | 3.3.5 S3D-150 nm PPDK parasitic extraction flow 62           |

|   | 3.4            | Summary                                                      |

| 4 | Seq            | uential 3D Receiver Front-End 65                             |

|   | 4.1            | Applications of S3D integration                              |

|   |                | 4.1.1 State-Of-The-Art                                       |

|   |                | 4.1.2 Motivation for S3D RF/AMS circuits 66                  |

|   | 4.2            | Design of the S3D receiver front-end                         |

|   |                | 4.2.1 High frequency blocks in the top tier 69               |

|   |                | 4.2.2 Baseband blocks in the bottom tier                     |

|   | 4.3            | S3D layout of the receiver front-end                         |

|   | 4.4            | Performance of the S3D receiver front-end                    |

|   | 4.5            | Summary                                                      |

| 5 | Ind            | uctors in a S3D process 81                                   |

|   | 5.1            | Inductor Topologies for S3D Integration 81                   |

|   | 5.2            | Impact of S3D Integration on Planar Inductors                |

|   | 5.3            | Impact of shields                                            |

|   | 5.4            | Multiple-Metal S3D Inductors                                 |

|   | 5.5            | Placement of bottom-tier blocks under top-tier inductors 93  |

|   |                | 5.5.1 Analog Blocks                                          |

|   |                | 5.5.2 Digital Blocks                                         |

|   | 5.6            | Summary                                                      |

| C' | ONTENTS | X1 |

|----|---------|----|

|    |         |    |

| 6  | $\mathbf{Het}$                                      | erogeneous S3D Integration: Ge over Si  | 105 |  |  |  |  |

|----|-----------------------------------------------------|-----------------------------------------|-----|--|--|--|--|

|    | 6.1 Current Status of Heterogeneous S3D Integration |                                         |     |  |  |  |  |

|    | 6.2                                                 | In-house Ge transistors                 | 107 |  |  |  |  |

|    | 6.3                                                 | Short-channel Ge transistors            | 108 |  |  |  |  |

|    | 6.4                                                 | Applications Ge-Over-Si S3D Integration | 113 |  |  |  |  |

|    | 6.4.1 Track-and-Hold Circuit                        |                                         |     |  |  |  |  |

|    | 6.4.2 Digital Cells                                 |                                         |     |  |  |  |  |

|    | 6.5                                                 | Back-gate control of top-tier FETs      | 116 |  |  |  |  |

|    | 6.6                                                 | Summary                                 | 118 |  |  |  |  |

| 7  | Con                                                 | clusions and Future Work                | 121 |  |  |  |  |

| Bi | Bibliography 1                                      |                                         |     |  |  |  |  |

# List of Figures

| 1.1<br>1.2<br>1.3 | Current trends in the semiconductor industry (adopted from [1]) Example of 3D integration with 3 stacked layers                                                                                                | 3  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                   | integration                                                                                                                                                                                                    | 4  |

| 1.4               | Interconnected devices for Internet Of Things (IoTs) applications                                                                                                                                              | 7  |

| 1.5               | Example of heterogeneous integration                                                                                                                                                                           | 8  |

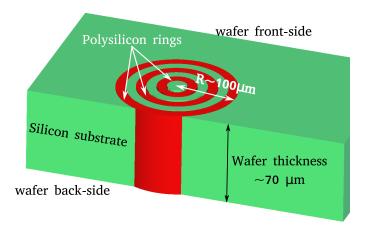

| 2.1               | Via-first TSV consisting of polysilicon rings                                                                                                                                                                  | 14 |

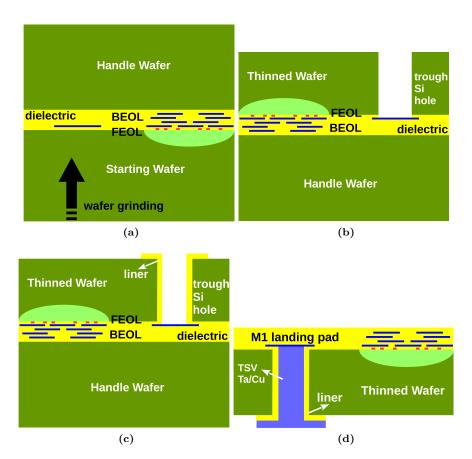

| 2.2               | (a) Wafer thinning (b) patterning of through-silicon holes (c) deposition of liner and its etching away from the M1 landing pad (d) TSV filling                                                                |    |

|                   | and planarization                                                                                                                                                                                              | 15 |

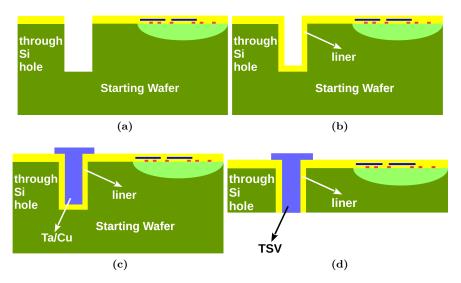

| 2.3               | (a) Wafer thinning (b) patterning of through-silicon holes (c) deposition of liner and its etching away from the M1 landing pad (d) TSV filling                                                                |    |

|                   | and planarization                                                                                                                                                                                              | 16 |

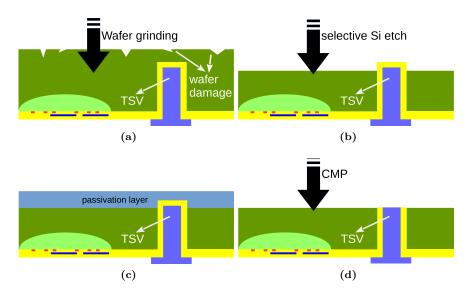

| 2.4               | TSV-reveal steps: (a) Wafer grinding (b) selective Si etch (c) deposition                                                                                                                                      |    |

|                   | of passivation layer to protect the Si substrate from copper contamination (d) TSV CMP to reveal the TSV                                                                                                       | 18 |

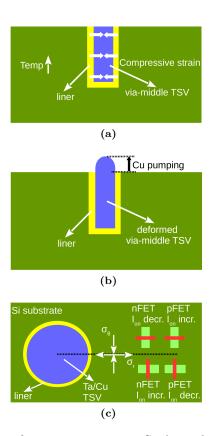

| 2.5               | (a) Build-up of compressive stress in Cu during heating (b) Cu pumping to relax compressive stress (c) impact of TSV-induced stress in Si on                                                                   |    |

|                   | neighboring FETs                                                                                                                                                                                               | 20 |

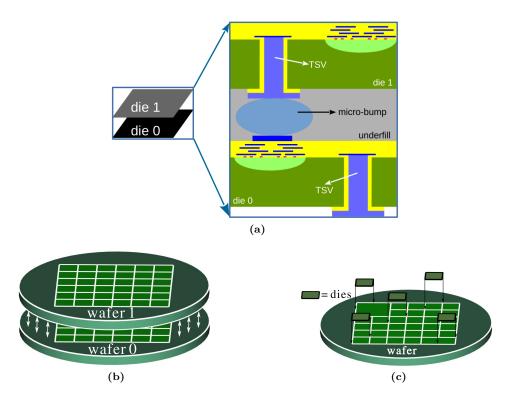

| 2.6               | (a) Die-to-Die (D2D) bonding (b) Wafer-to-Wafer (W2W) bonding (c) Die-to-Wafer (D2W) bonding                                                                                                                   | 22 |

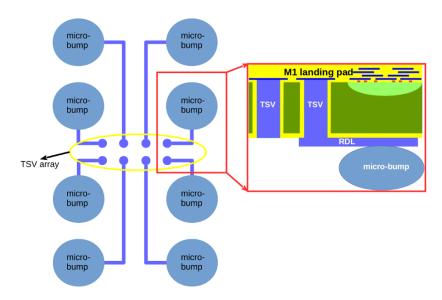

| 2.7               | High density of TSVs, enabled by the use of a RDL                                                                                                                                                              | 23 |

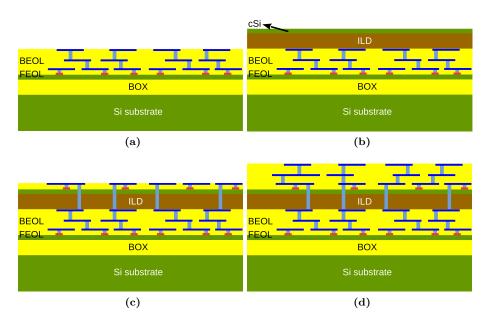

| 2.8               | CMOS over CMOS S3D integration process steps: (a) Bottom tier with tungsten metal lines (b) Deposition of the ILD and transfer of a thin crystalline Si layer (c) Top tier FEOL and patterning of MIVs (d) Top |    |

|                   | tier BEOL                                                                                                                                                                                                      | 26 |

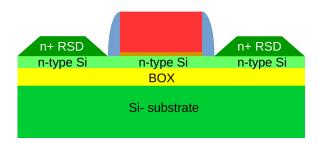

| 2.9               | Structure of a n-type junctionless FET                                                                                                                                                                         | 28 |

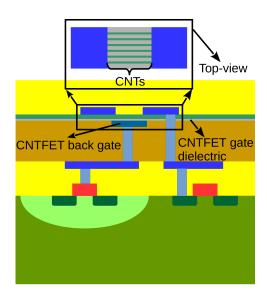

| 2.10              | S3D integration of CNTFETs over Si FETs. The inset shows the top-<br>view of a CNTFET                                                                                                                          | 30 |

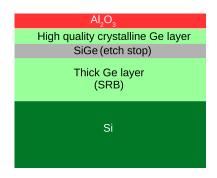

| 2.11              | Formation of a high quality, thin and crystalline Ge layer over a Si wafer, as proposed in [2]                                                                                                                 | 32 |

|                   | r r r r r r r r r r r r r r r r r r r                                                                                                                                                                          |    |

List of Figures xiii

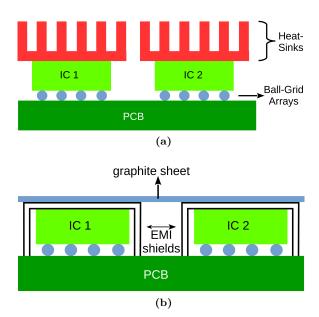

| 2.12              | (a) Classic packaging solution for high power applications (b) New packaging approach for mobile applications                                                                                                                                                                                             | 35       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

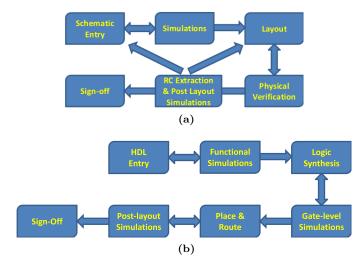

| 3.1<br>3.2<br>3.3 | (a) Custom IC design flow (b) Digital IC design flow                                                                                                                                                                                                                                                      | 38<br>40 |

|                   | L= 100 nm. The device consists of 10 nano-wires, each 20 nm wide. $$                                                                                                                                                                                                                                      | 42       |

| 3.4<br>3.5        | Layout of a KTH-S3D diode with $W = 2\mu m$                                                                                                                                                                                                                                                               | 43       |

| 3.6               | equal dimensions, W=L= 2 $\mu$ m                                                                                                                                                                                                                                                                          | 45       |

| 3.0               | tics of two diodes fabricated by the in-house process                                                                                                                                                                                                                                                     | 46       |

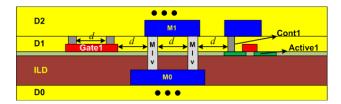

| 3.7               | MIVs parallel to top-tier contacts (Cont1), poly-silicon (Gate1) and active regions (Active1). The minimum distance between these layers is                                                                                                                                                               |          |

| 20                | $d=1 \ \mu \text{m}$                                                                                                                                                                                                                                                                                      | 47       |

| 3.8               | (a) TEM image of a via processed with the in-house process (b) Allowed stacking of non-successive vias (Via2 over MIV in this case)                                                                                                                                                                       | 47       |

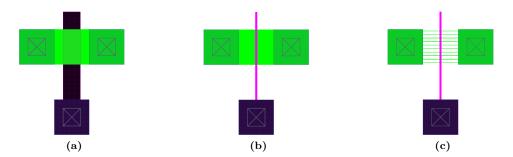

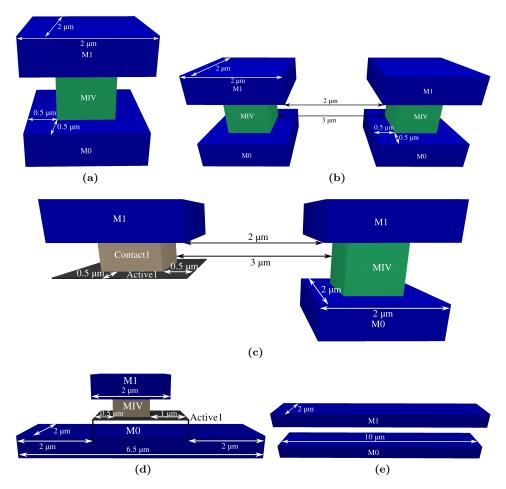

| 3.9               | Layout structures to extract the parasitics of: (a) a single MIV (b) the coupling between two neighboring MIVs (c) the coupling between a MIV and a top-tier contact (Contact1) (d) the coupling between a M0 line and a top tier active (Active1) region (e) the capacitance between a M0 and a M1 line. | 49       |

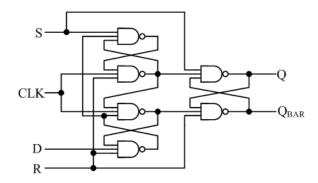

| 3.10              | Schematic of a 3-input NAND-based D flip-flop                                                                                                                                                                                                                                                             | 51       |

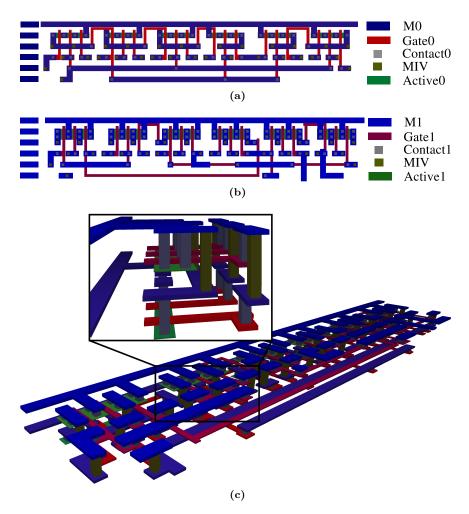

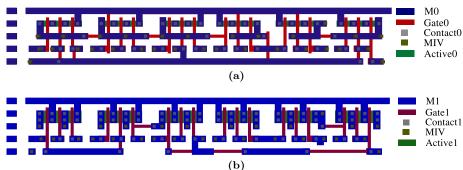

| 3.11              | Layout view of the KTH-S3D DFFSR cell in (a) the bottom tier and (b) the top tier. (c) 3D view of the KTH-S3D DFFSR. The NAND based module is shown in the inset                                                                                                                                          | 53       |

| 3.12              | Layout view of the ideal KTH-S3D DFFSR cell (with allowed stacking of successive vias) in (a) the bottom tier and (b) the top tier                                                                                                                                                                        | 54       |

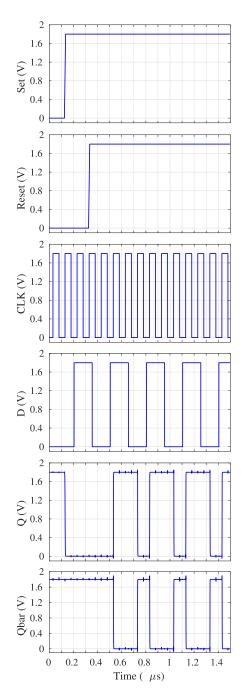

| 3.13              | Time-domain operation of a KTH-S3D DFFSR cell                                                                                                                                                                                                                                                             | 55       |

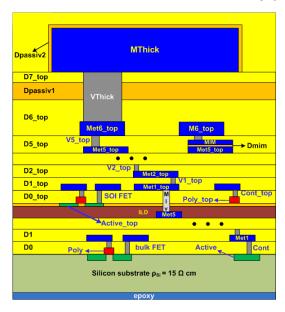

|                   | Process stack of the S3D PPDK                                                                                                                                                                                                                                                                             | 56       |

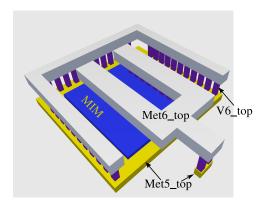

| 3.15              | 3-D layout view of a S3D PPDK MIM capacitor                                                                                                                                                                                                                                                               | 59       |

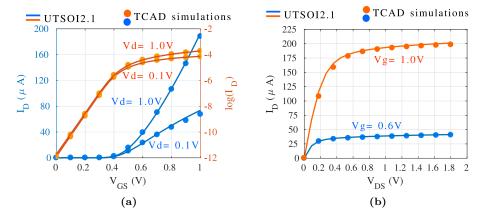

|                   | Calibrated UTSOI2.1 model and TCAD simulations for the transistor                                                                                                                                                                                                                                         |          |

|                   | (a) transfer and (b) output characteristics. The plots refer to a n-type FET with L= 250 nm and W= 1 $\mu$ m                                                                                                                                                                                              | 60       |

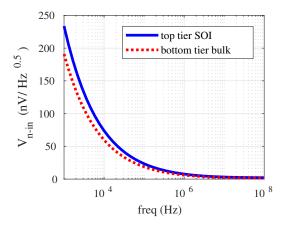

| 3.17              | Input referred noise voltage, $V_{n-in}$ of a nFET in the top and bottom tier. Both devices have the same dimensions and biasing: L= 150 nm,                                                                                                                                                              |          |

|                   | W= 10 $\mu$ m, I <sub>D</sub> =200 $\mu$ A and V <sub>DS</sub> = 0.5 V                                                                                                                                                                                                                                    | 61       |

xiv List of Figures

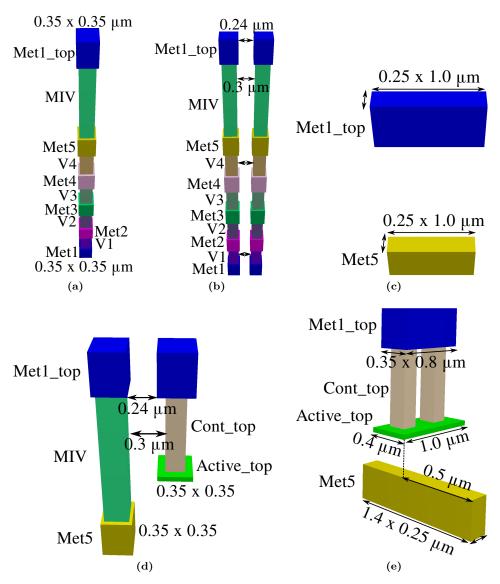

| 3.18 | Layout structures to extract the parasitics of: (a) a single Met5 -> Met1_top via stack (b) the coupling between two neighboring Met5 -> Met1_top via stacks (c) the coupling between a Met1_top and a Met5 line (d) the coupling between a MIV and Cont_top (e) the coupling between a Met5 line and an Active_top region | 63       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

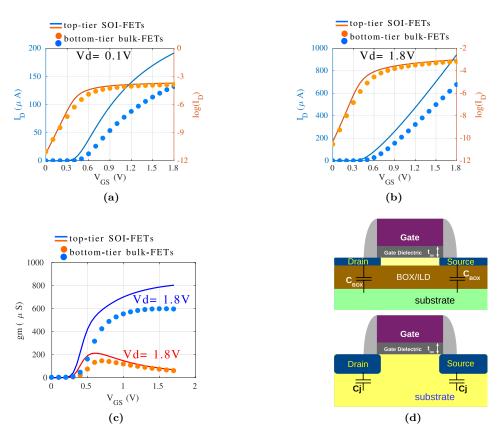

| 4.1  | Id versus Vgs for (a) $V_{DS}=0.1~V$ and (b) $V_{DS}=1.8~V$ . (c) Transconductan gm versus Vgs for $V_{DS}=0.1~V$ and 1.8 V. (d) Structures of the top-tier FDSOI (top structure) and bottom tier bulk (bottom structure) FETs. Note that for visual purposes, the dimensions of the various device re-                    |          |

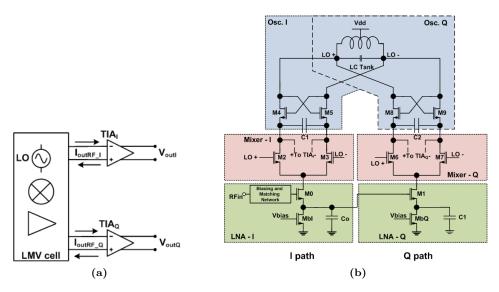

| 4.2  | gions are not scaled proportionally                                                                                                                                                                                                                                                                                        | 67<br>69 |

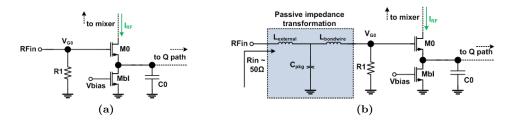

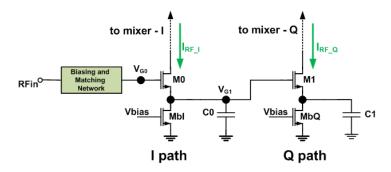

| 4.3  | (a) CS LNA with simple resistive input termination. (b) CS LNA with a passive impedance transformation network                                                                                                                                                                                                             | 70       |

| 4.4  | Quadrature generation through C0 and M1                                                                                                                                                                                                                                                                                    | 72       |

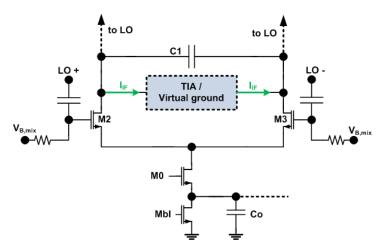

| 4.5  | Mixer sub-block in the LMV cell                                                                                                                                                                                                                                                                                            | 73       |

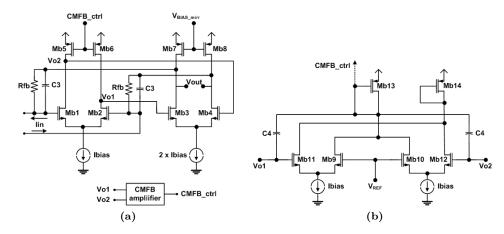

| 4.6  | (a) Schematic of the TIA. (b) Schematic of the CMFB circuit                                                                                                                                                                                                                                                                | 74       |

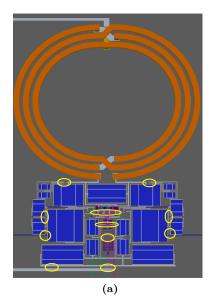

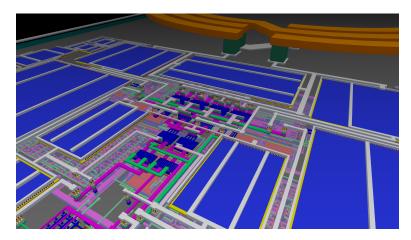

| 4.7  | (a) Layout of the designed S3D receiver in (a) the top and (b) the bottom                                                                                                                                                                                                                                                  | •        |

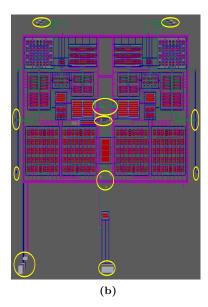

|      | tier. The location of MIVs are highlighted with yellow circles                                                                                                                                                                                                                                                             | 75       |

| 4.8  | 3-D view of the S3D receiver front-end. Top tier blocks are shown with                                                                                                                                                                                                                                                     |          |

|      | opaque colors and bottom tier with transparent. $\ \ldots \ \ldots \ \ldots \ \ldots$                                                                                                                                                                                                                                      | 76       |

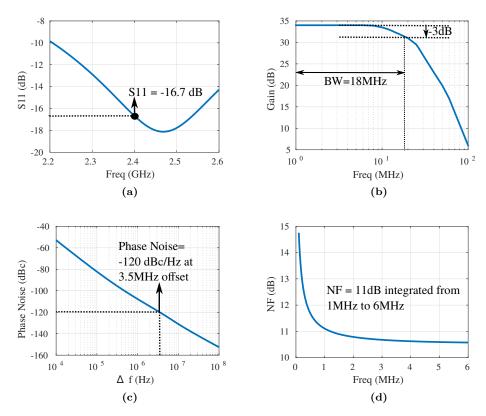

| 4.9  | (a) $S_{11}$ , (b) Gain of the receiver chain, (c) Phase Noise and (d) double-sideband NF versus frequency                                                                                                                                                                                                                 | 78       |

| 5.1  | 3D solenoid implemented with TSVs                                                                                                                                                                                                                                                                                          | 82       |

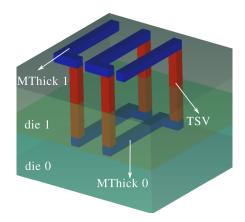

| 5.2  | (a) Structure of the S3D solenoid. (b) Inductance and (c) Quality factor                                                                                                                                                                                                                                                   |          |

|      | of the S3D solenoid                                                                                                                                                                                                                                                                                                        | 83       |

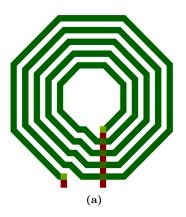

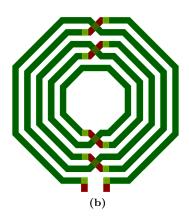

| 5.3  | (a) Asymmetric and (b) Symmetric inductor topology                                                                                                                                                                                                                                                                         | 84       |

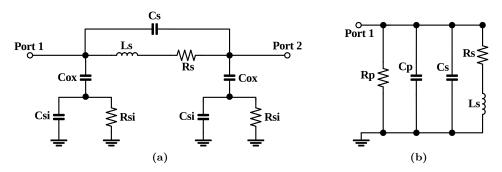

| 5.4  | (a) Lumped network employed for inductors. (b) Simplification of the                                                                                                                                                                                                                                                       |          |

|      | inductor lumped network, assuming Port 2 is grounded                                                                                                                                                                                                                                                                       | 85       |

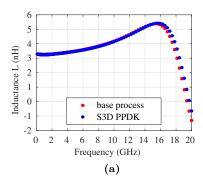

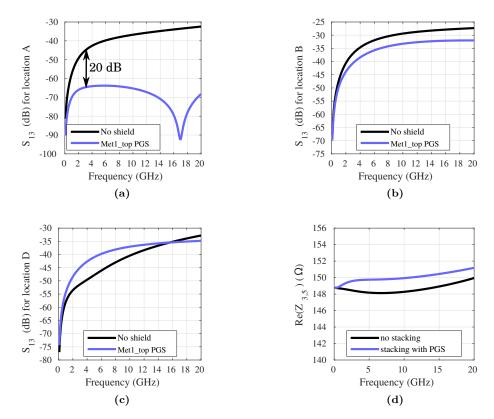

| 5.5  | (a) Inductance and (b) quality factor for an inductor built in the base                                                                                                                                                                                                                                                    |          |

|      | process and the same topology transferred to the S3D PPDK                                                                                                                                                                                                                                                                  | 87       |

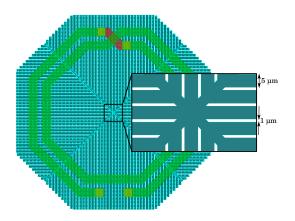

| 5.6  | Inductor with a PGS. The shield contains metal stripes, each 5 $\mu m$ wide.                                                                                                                                                                                                                                               |          |

|      | The spacing between adjacent stripes is $1 \mu m$                                                                                                                                                                                                                                                                          | 88       |

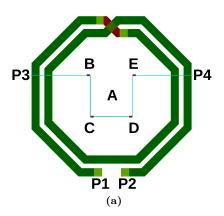

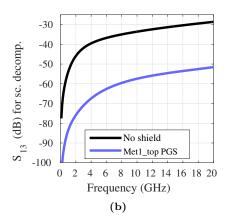

| 5.7  | (a) Considered structure to validate the effectiveness of the PGS in sup-                                                                                                                                                                                                                                                  |          |

|      | pressing substrate noise (b) Isolation between the inductor and the sub-                                                                                                                                                                                                                                                   |          |

|      | strate, quantified by the $S_{13}$ parameter                                                                                                                                                                                                                                                                               | 89       |

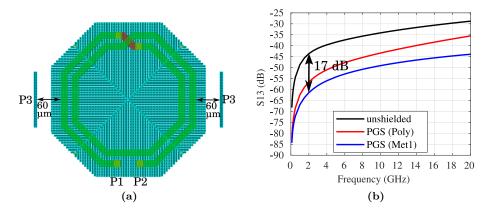

| 5.8  | (a) Base process inductor (b) S3D inductor formed by shunting together                                                                                                                                                                                                                                                     |          |

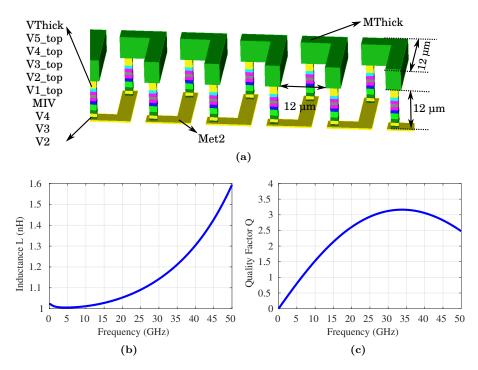

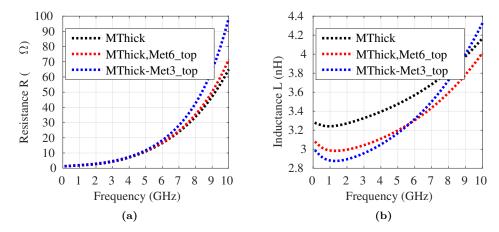

|      | the top tier metals MThick -> M3_top                                                                                                                                                                                                                                                                                       | 90       |

| 5.9  | (a) Multi-metal S3D inductor. The red rectangles are the vias that shunt                                                                                                                                                                                                                                                   |          |

|      | together the multiple metal layers (b) 3D view of the multi-metal S3D                                                                                                                                                                                                                                                      |          |

|      | inductor                                                                                                                                                                                                                                                                                                                   | 91       |

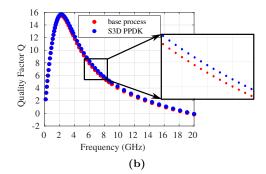

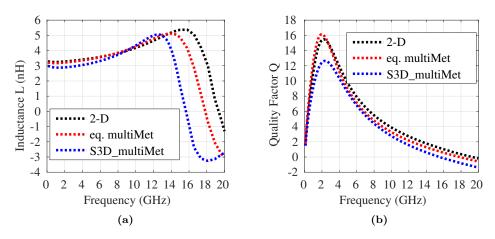

| 5.10 | (a) Inductance and (b) quality factor of the multi-metal S3D inductor                                                                                                                                                                                                                                                      | 92       |

List of Figures xv

| Ę | 5.11 | (a) Resistance and (b) low-frequency inductance of the multi-metal S3D inductor versus frequency                                                                                                                                                                                                                | 93  |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

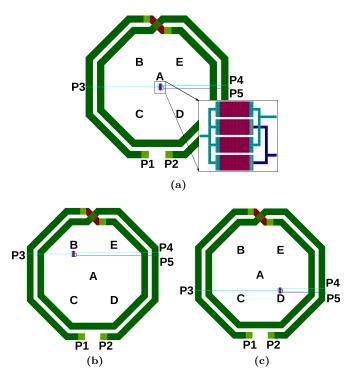

| Ę | 5.12 | Considered structure to study the impact of the location of bottom tier blocks under the inductor on the inter-tier EM isolation                                                                                                                                                                                | 94  |

| ŗ | 5.13 | Inter-tier EM isolation when the resistive network is placed under the inductor at position (a) A (b) B and (c) D. (d) Resistance between ports P3 and P5 before and after placing the resistive network under the inductor center (location A)                                                                 | 95  |

| Ę | 5.14 | (a) Studied topology to emulate larger blocks and (b) inter-tier EM isolation                                                                                                                                                                                                                                   | 96  |

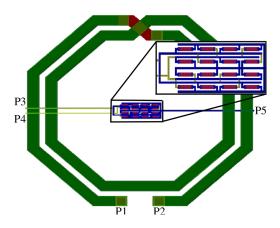

| Ę | 5.15 | 4x4 resistor array under a top-tier inductor                                                                                                                                                                                                                                                                    | 97  |

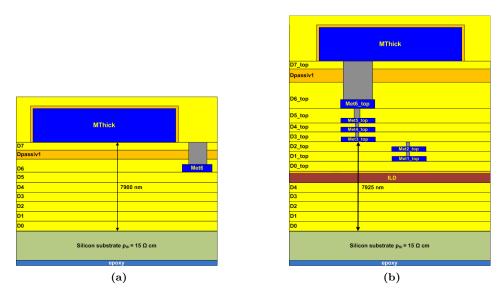

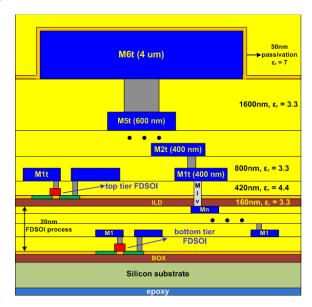

|   |      | S3D process stack used to study the EM coupling between bottom-tier digital blocks and top-tier inductors. The process data of the 20 nm FD-SOI process are provided on an "as is" basis through ASCENT, funded by the EU H2020 Infrastructure Programme (H2020-INFRAIA-2014-2015) under Grant Agreement 654384 | 99  |

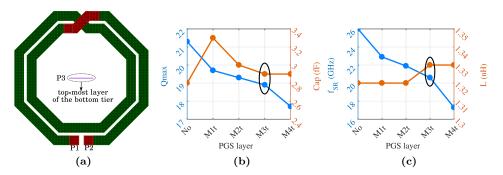

| Ę | 5.17 | (a) Studied topology to identify the most optimal PGS layer (b) Impact of the PGS on inductor's $Q_{max}$ and wire's $Cap$ . (c) Impact of PGS on $f_{SR}$ and $L_{diff}$                                                                                                                                       | 100 |

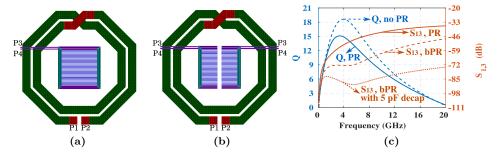

| ţ | 5.18 | (a) Top tier inductor and bottom tier power ring.(b) Proposed broken power ring to suppress eddy currents. (c) Inter-tier EM isolation between the inductor and the power ring, and quality factor for the inductor.                                                                                            | 101 |

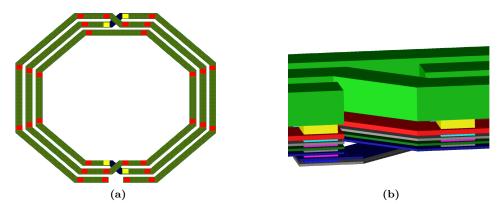

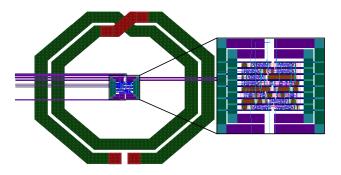

| Ę | 5.19 | A 3-bit adder is placed in the bottom tier under a top-tier inductor. Details of the adder implementation are shown in the inset                                                                                                                                                                                | 102 |

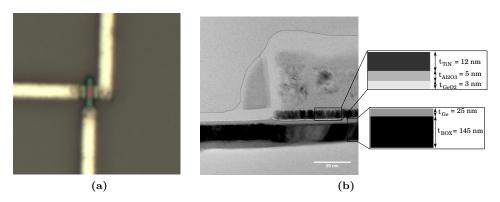

| ( | 3.1  | (a)<br>Top-view and (b) cross-section of a measured in-house Ge-pFET with<br>$L = 800~\rm{nm}$                                                                                                                                                                                                                  | 107 |

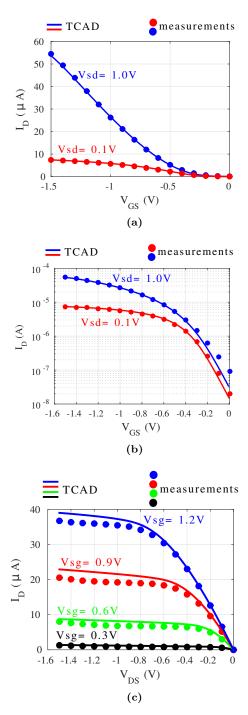

| ( | 3.2  | Measurement results for an in-house Ge transistor and corresponding TCAD simulations. $I_D$ versus $V_{GS}$ in (a) linear and (b) semi-logarithmic                                                                                                                                                              |     |

|   |      | axis and (c) $I_D$ versus $V_{DS}$                                                                                                                                                                                                                                                                              |     |

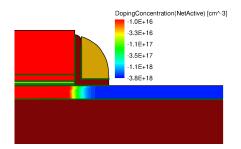

| ( | 3.3  | Net concentration of activated dopants in the channel $\dots \dots \dots$ .                                                                                                                                                                                                                                     | 110 |

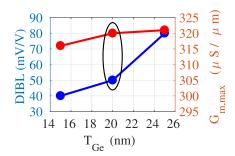

| ( | 6.4  | Dependence on DIBL and $G_{m,max}$ on the Ge layer's thickness, $T_{Ge}$                                                                                                                                                                                                                                        | 110 |

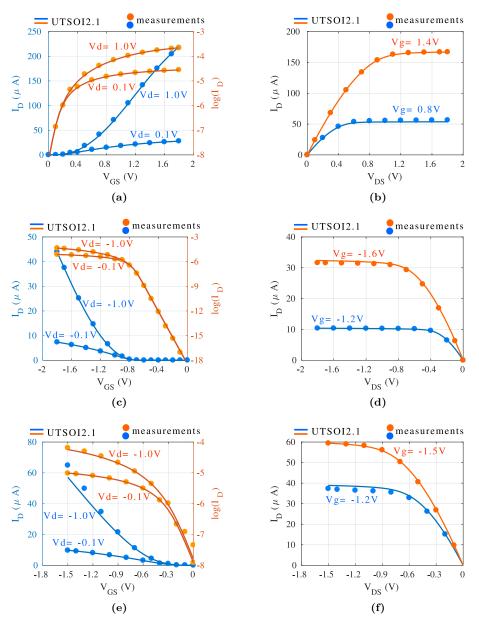

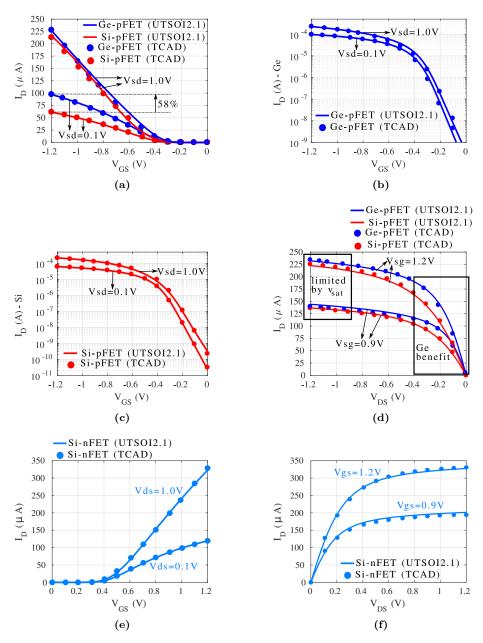

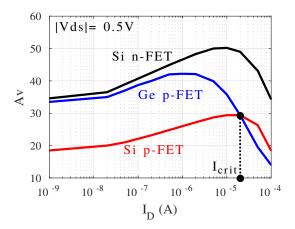

| ( | 3.5  | (a) Transfer characteristics of Ge and Si pFETs. TCAD and spice simulations for (b) Ge pFETs and (c) Si pFETs. (d) Output characteristics of the Ge and Si pFETs. (e) Transfer and (f) output characteristics of the Si pFET device.                                                                            | 111 |

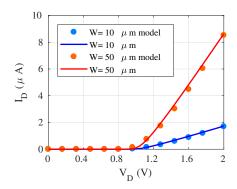

| ( | 6.6  | the Si nFET device                                                                                                                                                                                                                                                                                              |     |

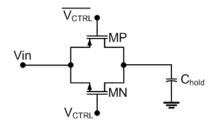

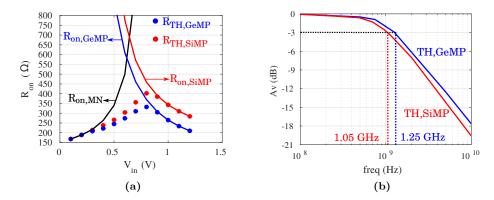

| f | 3.7  | CMOS TH circuit with $C_{hold} = 500$ ff                                                                                                                                                                                                                                                                        |     |

|   | 5.8  | (a) $R_{TH}$ for a Ge and a Si pFET (b) $BW_T$ for a Ge and Si pFET                                                                                                                                                                                                                                             |     |

|   |      |                                                                                                                                                                                                                                                                                                                 |     |

xvi List of Figures

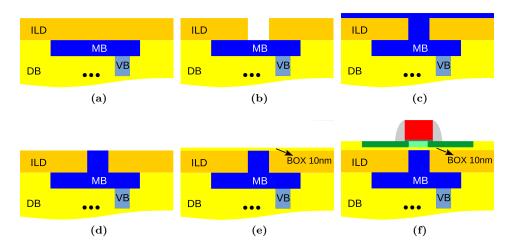

| 6.9  | (a) Deposition of ILD over the last bottom tier metal, MB. (b) Etching of |     |

|------|---------------------------------------------------------------------------|-----|

|      | the ILD to form back-gate contact-hole. (c) Metal Filling of the contact- |     |

|      | hole. (d) Etching and CMP of the metal from all the areas outside the     |     |

|      | contact-hole. (e) Formation of a 10 nm thick oxide, that will form the    |     |

|      | BOX of the top-tier FETs. (f) Processing of the top-tier FETs             | 118 |

| 6.10 | Transfer characteristics of a 150 nm Ge pFET for various back gate        |     |

|      | voltages $V_{BG}$ . The back-gate biasing has been enabled through the    |     |

|      | devised process flow.                                                     | 110 |

# List of Tables

| 2.1 | Heterogeneous S3D integration: Comparison between Ge and InGaAs top-tier FETs                                                         |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 | Characteristics of the in-house KTH-S3D process stack                                                                                 |

| 3.2 | Sheet resistance for the KTH-S3D resistors                                                                                            |

| 3.3 | Minimum width and spacing for the layers in the KTH-S3D PDK 40                                                                        |

| 3.4 | Comparison between the parasitic capacitance obtained with the KTH-S3D parasitic extraction flow and with Momentum EM simulations (by |

|     | Keysight®)                                                                                                                            |

| 3.5 | Truth Table for the KTH-S3D DFFSR cell                                                                                                |

| 3.6 | Performance comparison between the KTH-S3D inverter cell and its 2-D                                                                  |

|     | in-house implementation                                                                                                               |

| 3.7 | Characteristics of the S3D PPDK considered process stack 58                                                                           |

| 3.8 | Basic design rules for S3D-150nm PPDK layers 6                                                                                        |

| 3.9 | Comparison between the parasitic capacitance obtained with the S3D-150 nm PPDK's parasitic extraction flow and Momentum EM simula-    |

|     | tions (by Keysight®) 65                                                                                                               |

| 4.1 | Simulated performance of the S3D receiver front-end                                                                                   |

| 5.1 | Impact of the PGS on a S3D inductor                                                                                                   |

| 5.2 | Inter-tier EM isolation                                                                                                               |

| 5.3 | Characteristics of the passive devices before and after stacking 98                                                                   |

| 5.4 | Analysis of the placement of a 3-bit adder under a top-tier inductor 10:                                                              |

| 6.1 | Comparison between the Ge pFET, the Si pFET and the Si nFET 11:                                                                       |

| 6.2 | Performance comparison between a TH with a $Ge$ and with a $Si$ pFET . 110                                                            |

| 6.3 | Characteristics of the passive devices before and after stacking 11'                                                                  |

## List of Acronyms

ABB Adaptive Back-gate Biasing

ADC Analog-to-Digital Converter

AMS Analog/Mixed-Signal

AR Aspect Ratio

ASIC Application Specific Integrated Circuit

BEOL Back-End-Of-Line BOX Buried Oxide

BSIM Berkley Short-channel Independent gate field effect transistors

Model

**BSIM-IMG** BSIM Independent Multiple Gates

CMFB Common Mode FeedbackCMP Chemical Mechanical Polishing

CNTs Carbon Nano-Tubes

**CNTFETs** Carbon Nano-Tube Field Effect Transistors

CS Common Source

CTE Coefficient of Thermal-Expansion

CVD Chemical Vapor Deposition

D2D Die-To-Die bonding D2W Die-To-Wafer bonding

**DDR3** Double Data Rate Type Three

**DFF** D flip flop

DIBL Drain Induced Barrier Lowering

DRAM Dynamic Random-Access Memory

**DRC** Design Rule Checks

EBL Electron Beam Lithography

EDA Electronic Design Automation

**EM** Electromagnetic

EOT Equivalent Oxide Thickness

EUV Extreme Ultra-Violet

FET Field-Effect Transistor

FD-SOI Fully Depleted - Silicon On Insulator

**FEOL** Front-End-Of-Line

**HVM** High Volume Manufacturing

IC Integrated Circuit

IEOL Intermediate End Of Line

IF Intermediate Frequency

IO Input/Output

KGD Known Good DieKOZ Keep Out Zone

LED Light Emitting Diodes

LER Line Edge Roughness

$\mathbf{LMV} \qquad \qquad \text{Low noise amplifier - Mixer -}$

Voltage Controlled Oscillator

LNA Low Noise Amplifier

LVS Layout Versus Schematic

M3D Monolithic 3-D

MIM Metal-Insulator-Metal

MIV Monolithic Inter-tier Via

MOM Metal-Oxide-Metal

MOSCAP Metal-Oxide-Semiconductor Capacitor

**NF** Noise Figure

PCells Parameterized Cells

PDK Process Design Kit

PDN Pull Down Network

PGS Patterned Ground Shield

PiN diodes p+/intrinsic Si/n+ diode

PITN Passive Impedance Transformation Network

PoP Package-On-Package

PPDK Predictive PDK

PR Power Ring

PUN Pull Up Network

RF Radio Frequency

RAM Random Access Memory RDF Random Dopant Fluctuation

RSD Raised Source/Drain

RTA Rapid Thermal Annealing

RDL Redistribution Layer

**ReRAMs** Resistive Random Access Memories

S3D Sequential 3-D

**SADP** Self-Aligned Double Patterning

SCEShort Channel EffectsSiPSystem in PackageSoCSystem on ChipSPESolid-Phase Epitaxy

SR Slew Rate

$egin{array}{lll} \mathbf{SRB} & \mathbf{Strain} \ \mathbf{Relaxed} \ \mathbf{Buffer} \\ \mathbf{SS} & \mathbf{Sub\text{-}threshold} \ \mathbf{Slope} \\ \end{array}$

TCAD Technology Computer Aided Design

THC Track and Hold Circuits

UTBB Ultra Thin Body and BOX

VCO Voltage Controlled Oscillator VGA Variable Gain Amplifier

W2W Wafer-To-Wafer bonding

WPAN Wireless Personal Area Networks

### Chapter 1

### Introduction

#### 1.1 New Directions for Moore's Law

The observations and predictions made by Gordon Moore about the density of integrated components in a chip [4], which later came to be known as "Moore's Law", have driven the semiconductor industry since its first steps. Gains in the integration density of chips have been typically achieved through the continuous dimensional scaling of the integrated components, a path that became known as "More Moore". Although Moore's predictions were based on financial grounds and in particular on reducing the cost per components of integrated circuits (ICs), dimensional scaling has led also to a reduction in gate delays, and for the case of constant field scaling, in the total power consumption as well [5].

However, the continuous dimensional scaling has brought many challenges. As transistor lengths moved to the sub-100 nm regime, more complex processing has emerged to improve transistor performance and at the same time guarantee high production yields. For instance, strained silicon transistors were used by Intel® in their 90 nm node to improve carrier mobility [6]. High-k gate dielectrics and metal gates have been employed in Intel's 45 nm to reduce gate leakage [7]. Air-gapped interconnects were introduced in Intel's 14 nm node to reduce the coupling capacitance between adjacent metal lines, as well as self-aligned double patterning (SADP) for patterning critical layers [8]. SADP along with multiple patterning have been employed to pattern features like transistor gates, fins or metal wires, whose dimensions are smaller than the resolution of the lithography tools. They involve multiple cycles of lithography exposure and etching to pattern a single layer. In multiple patterning, all features of a layer are split into groups (colors) and each group is patterned by a different mask. Color-based patterning imposes additional design rules, further complicating both the physical implementation and physical verification flows. For instance, local color-density deviations can result in coupling capacitance variations, which in turn may require timing and power re-characterization [9].

Extreme Ultra-Violet (EUV) lithography could mitigate these issues since it offers higher resolution compared to today's 193 nm immersion lithography. Additionally, it negates the need for multiple-exposure patterning. However, current EUV sources lack enough power (larger than 250 W) for High Volume Manufacturing (HVM), while there is still room for improvements in the sources' lifetime [10]. Another critical issue that impedes the commercial adoption of EUV lithography is the absence of pellicles that could protect the mask from contamination during the exposure stage, which at the same time can withstand the source power levels required for HVM [11].

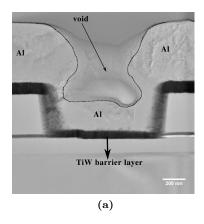

Apart from the increased process complexity, another issue that rises with the continuous scaling is the increased resistance of the routing resources. At each new node, the metal pitch is also scaled to allow an increase in the integration density. This causes the metal thickness to drop as well, which in turn, accentuates the impact of the highly resistive diffusion barrier material (i.e. TaN) and causes an exponential increase in the wires resistance [12]. Another important issue with scaled interconnects lies with the pronounced reliability issues, caused by the multiple processing during their patterning. Each of these steps induces variation in a design: Chemical-Mechanical Polishing (CMP), etching, overlay error for multiple patterning and for the case of SADP, core and spacer variations. All these variation sources have a negative impact on the performance and reliability of a design [13]. The phenomenon is further exacerbated by the small dimensions of the routing wires. All in all, the interconnect bottleneck has posed a major roadblock in the "More Moore" path.

As transistor dimensions kept dropping, the gate control over the channel has dropped, leading to severe short channel and Drain-Induced Barrier Lowering (DIBL) effects. As a result, FinFETs have been adopted for the Front-End-Of-Line (FEOL) in the Intel's 22 nm node [14], thanks to their superior gate control over the channel, as compared to planar transistors. Although this adoption has been beneficial for digital designs, it has placed an additional burden to Analog and Mixed-Signal (AMS) designers who have to cope also with an increased number of design rules with rather limited assistance from Electronic Design Automation (EDA) tools. FinFETs suffer from high gate, source and drain contact resistances because of the limited silicidation of the active regions [12]. Furthermore, the 3D structure of FinFETs cause higher device capacitances with respect to planar transistors, which in turn limit significantly the performance of these devices at high frequencies. Therefore, advanced process nodes hinder the design of high performance radio frequency (RF) and AMS circuits.

The aforementioned issues (i.e. complex and more expensive processing, interconnect bottleneck, performance degradation for RF/AMS circuits) have led to rising concerns that the dimensional scaling trend is reaching a dead-end. Recently, GlobalFoundries® has decided to drop out from the pursuit of the 7 nm node claiming financial reasons and reduced customer interest. Instead, the company will focus on adding further capabilities to their existing FinFET and FD-SOI processes. Most of the semiconductor industry appears to re-direct their business

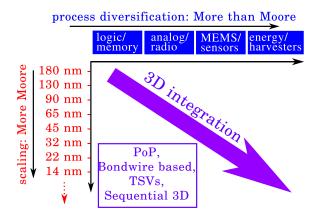

Figure 1.1: Current trends in the semiconductor industry (adopted from [1]).

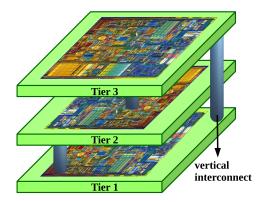

Figure 1.2: Example of 3D integration with 3 stacked layers

model from the traditional supply-driven approach to emphasizing diversification with optimized processes for specific applications (memories, logic, RF, sensors, etc), a path that became known as "More than Moore" [15] and which is shown in Fig. 1.1. This path employs new materials, as well as innovations in both the semiconductor processing and packaging. It also calls for a close synergy between process engineers and circuit designers to obtain optimal integration solutions.

3D integration, with the vertical stacking of tiers of devices, as it is shown in Fig. 1.2, could bridge the "More Moore" and the "More than Moore" paths. Vertical stacking increases the integration density by adding more functionality to an IC with no penalty on area. Moreover, the small distance between the stacked tiers enables short-distance and low-parasitics vertical interconnects, which in turn can reduce wirelength. Denser vertical interconnects result in more wirelength

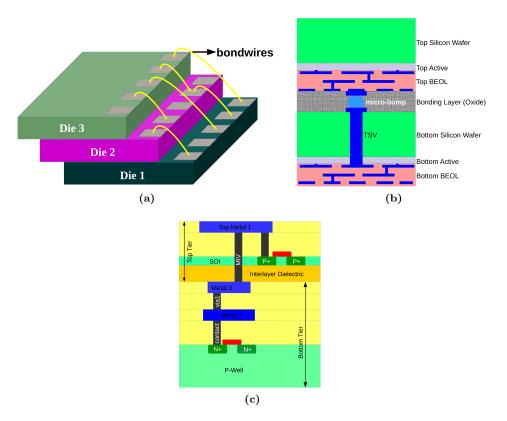

Figure 1.3: Examples of 3D ICs (a) bond-wire stacking (b) TSV based ICs (c) S3D integration

reduction and consequently in performance and power improvements, alleviating thus the interconnect bottleneck in advanced nodes. 3D integration enables also heterogeneous integration by stacking different types of device tiers, with each tier being optimized for a specific function. Thus, 3D integration could lead to the development of power and area efficient System-On-Chip (SoC) applications.

#### 1.2 3D Integration Technologies

The current 3D integration technologies can be divided into two types: package-on-package stacking (PoP) [16] and single package. For the single-package approach, three technologies have been developed: (a) bond-wire based die stacking, (b) Through-Silicon Vias (TSV) based 3D ICs and (c) Sequential 3D (S3D) integration (known also as Monolithic 3D - M3D).

Bond-wire based 3D die-stacking, as shown in Fig. 1.3(a), refers to the vertical

stacking of dies, such as processors, DRAMs and NAND flash memories, that are interconnected with bond-wires and form a System-In-Package (SiP). The stacking of sixteen dies, has been reported in [17]. Although this stacking approach is widely used in mobile devices for area-efficient solutions, it suffers from the lowest density of vertical (inter-die) interconnects among the other alternatives, which in turn leads to trivial, if any, wirelength improvements. Thus, when it comes to performance, the benefits of bond-wire based 3D stacking are insignificant. Instead, this integration approach has mainly financial benefits, thanks to the possibilities of cost reductions, enabled by the availability of multiple supply sources [18].

On the other hand, TSV-based 3D ICs feature a higher density of vertical interconnects than wire-bond based die stacking. Various implementation techniques have been proposed for TSV-based 3D ICs [19, 20]. Typically, they start with at least two patterned dies, with TSVs being etched and filled in at either one or both of them (back-to-back stacking). The two dies are then stacked and bonded together through micro-bumps, as shown in Fig. 1.3(b). TSV-based 3D ICs have already made their way to commercial products. For instance, a TSV-based 8 Gb 3D DDR3 (Double Data Rate Type 3) DRAM (Dynamic Random Access Memory) has been presented in [21], consisting of four stacked 2 Gb DRAM chips and interconnected through TSVs, each with a 30  $\mu$ m diameter. The TSV pitch equals  $80\mu m$  and each chip is fabricated in a 50 nm DRAM process resulting in a total footprint of 10.9 x 9 mm. The 8 Gb DRAM demonstrates power gains and improvement of the Input/Output (IO) speed compared to wire-bond based die-stacking implementations. Smaller TSVs with typical values of 5-10  $\mu$ m for their diameters and 50-100  $\mu$ m for their heights have been demonstrated for increasing the density of vertical interconnects [18]. Even with these improvements however, TSV-based approaches fall short from the required vertical interconnect pitch (smaller than  $5\mu$ m) for future 3D SoCs [18]. Further reduction of the TSV dimensions will not yield higher vertical interconnect densities, which are limited by the pitch of the microbumps [18].

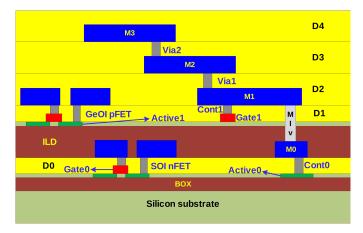

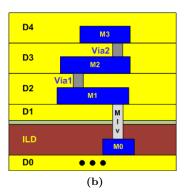

S3D integration, also described as monolithic 3D (M3D), offers the highest density of vertical interconnects. Unlike the other two options, S3D integration does not rely on the bonding of two pre-patterned device tiers; instead a second device tier is processed over a pre-patterned one. An example of a S3D process stack is shown in Fig. 1.3(c). More specifically, a thin active layer is transferred (typically through means of wafer bonding) over a patterned wafer and processed to form the top-tier's devices (Front-End-Of-Line, FEOL) [22–24]. The application of wafer bonding negates the use of microbumps, with their large area overhead. Following the top-tier's FEOL, inter-tier vias (Monolithic Inter-tier Vias, MIVs) are etched and filled to establish connectivity between the two tiers. Due to S3D's sequential processing, the alignment precision between stacked tiers depends solely on the lithography stepper. Thus, MIVs can be processed like any other metal-to-metal via, opening the path to ultra high density vertical interconnects [25]. Assuming that all tiers in a S3D implementation are processed in the 14 nm FinFET process from [8], the MIV pitch could be as low as 70 nm. Thanks to the small

MIV pitch, S3D designs are expected to offer smaller footprints and shorter wirelengths than TSV-based ones, with consequent improvements in speed and power [26]. Another area that could benefit from S3D integration is brain-inspired architectures for power efficient computing. S3D ICs, with their vertical interconnects, could better emulate brain-inspired architectures with thousands of synapses per neuron, as opposed to conventional planar implementations [27], becoming thus a key-enabling technology for future computing. Despite the fact that S3D processing technologies are still under development, an insight into potential applications of this technology, design methodologies and EDA tools is required. Based on the concepts of design-technology co-optimization, a close collaboration between designers, EDA tool developers and process engineers is necessary to ensure high production yields, preferably without sacrifices in "designability" and also to allow faster time to market [28].

So far, research on S3D design methodologies has led to three main approaches for the partitioning scheme between the stacked tiers: block-level, gate-level and transistor-level partitioning. In block-level partitioning, the functional blocks of a digital design are split between two or more tiers [29]. Clearly, this approach does not take full potential of the smaller MIV-pitch and consequently, it results in low vertical interconnect densities. Nonetheless, it can better cope with performance variations between the stacked tiers [29]. On the other hand, in gate-level partitioning, digital cells are placed one on top the other [30-33] leading to denser vertical interconnects. The highest density of vertical interconnects is achieved through the transistor-level partitioning scheme [34, 35]. In this approach, each cell of a digital library is split between two tiers, with the NMOS transistors placed in one and the PMOS in another. A hybrid S3D floorplanner that combines the benefits of these three approaches and specifies the optimal partitioning option for each block (no S3D partitioning, transistor-level and gate-level partitioning) has been presented in [36]. All these partitioning schemes aim at equal footprints between stacked tiers. Alternatively, limiting 3D stacking to only long nets would trade-off area reduction with improvements in both speed and power [37]. Memories, for instance SRAM designs, is another application that could benefit from the small pitch of MIVs [38–40]. S3D integration, however, does not limit to CMOS over CMOS applications only. The use of materials other than silicon for top tier devices enables a high-degree of heterogeneous integration. For instance, in [41], the integration of CMOS devices with tiers of resistive RAMs (RRAMs) and Carbon Nano-Tubes (CNTs) Field Effect Transistors (FETs) has led to very tight integration between logic and memory. Ge or III-V materials with their superior carrier mobilities can be also employed as channel materials for the top tier [42, 43].

#### 1.3 Motivation

Recently, a major paradigm shift has been observed from processing data at a central node to distributing data processing among various interconnected devices,

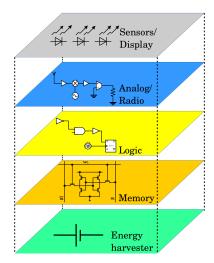

Figure 1.4: Interconnected devices for Internet Of Things (IoTs) applications

allowing thus Internet-Of-Things (IoTs) applications [27], as shown conceptually in Fig. 1.4. The need for distributed processing rises from the large count of such interconnected devices, which cause severe communication traffic between them and the central node, which in turn affects the performance [27]. Furthermore, central processing puts safety into question, owing to the increased probabilities of communication disruptions [27]. For the distributed processing paradigm, apart from logic and memory, radio circuits are also required to communicate data, in addition to AMS circuits for read-out operations. Co-integration of all these circuits with sensors would be also desirable to improve signal-to-noise performance. S3D integration, with its large density of vertical interconnects and its inherent heterogeneous features could prove beneficial for IoTs applications. A S3D IC could consist of various device tiers, each one optimized for a specific function, as shown in Fig. 1.5. Thus, S3D design methodologies for applications other than logic and memories need to be investigated and developed. Towards this, a S3D design platform for custom integrated circuits (ICs) is essential. The S3D design platforms proposed so far, are restricted only to digital circuits [44,45]. Furthermore, to take full advantage of the heterogeneous integration capabilities of S3D technology, the impact of Ge or III-V materials on the performance of S3D circuits needs also to be explored. For instance, the superior mobility of III-V materials or Ge could allow the downsizing of the top-tier devices, leading to further area gains.

#### 1.4 Research Objectives

The main goal of this thesis is to demonstrate the potential of S3D integration for future circuits and systems. More specifically, this thesis aims to investigate design

Figure 1.5: Example of heterogeneous integration

methodologies for high performance and area efficient S3D ICs. Towards this, and based on the motivations described previously, a set of research objectives has been set:

- Objective 1: Develop a S3D design methodology and flow for customs ICs.

- **Objective 2:** Investigate circuits and applications that could benefit from S3D integration.

- Objective 3: Propose solutions to counteract the impact of S3D processing on the circuit performance.

- Objective 4: Study the impact of materials other than silicon in the top tier, on the performance of S3D circuits and systems.

#### 1.5 Research Contributions

In relation to the objectives stated above, the research contributions of the present thesis are the following:

• Contribution 1: A S3D design platform has been developed through means of a Process Design Kit (PDK). The PDK is compatible with commercial CAD and EDA tools to facilitate migration to S3D technologies. Accurate transistor models are included for both bottom and top tier devices. To enable physical verification, sets of Design Rule Checks (DRC) and Layout Versus Schematic (LVS)

checks have been also included in the PDK. A parasitic extraction flow has been developed to analyze the inter-tier coupling. This S3D PDK is used to explore circuits that could benefit from S3D integration, develop design techniques and analyze the S3D circuits performance (Papers I and II). An additional S3D PDK has been also developed to facilitate the development of the KTH in-house S3D process.

- Contribution 2: Considering the main characteristics of S3D integration technology, the potential of S3D RF/AMS circuits and systems has been identified. A frequency-based partition scheme has been devised, in which high frequency blocks were placed in the top tier and low-frequency ones in the bottom tier. As a proof of concept, a S3D receiver front-end for Wireless Personal Area Network (WPAN) applications has been designed and simulated in the developed S3D PDK. (Paper II)

- Contribution 3: To further advance the previous study on S3D RF/AMS circuits and systems, the placement of inductors in a S3D technology has been explored (Paper III). It has been found that a planar coil in a top tier thick metal is the most optimal configuration for inductors in a S3D process. To further improve the area efficiency of S3D RF/AMS circuits and systems, guidelines have been proposed for the effective placement of bottom tier blocks underneath top tier inductors to ensure high electromagnetic isolation between them (Paper III and IV).

- Contribution 4: The design prospects of a S3D integration technology with Ge in the top-tier have been investigated. Circuits that do not operate continuously in the saturation region, such as track-and-hold and digital cells have been shown to benefit the most from such a Ge-over-Si S3D integration technology.

#### 1.6 List of Publications

• [Paper I] P. Chaourani, P.-E. Hellström, G. Malm, S. Rodriguez, A. Rusu "Towards Monolithic 3D Integration: A Design Flow," in CDNLive2016, Cadence User Conference EMEA, Munich, Germany, May 2-4, 2016, available: "http://kth.divaportal.org/smash/record.jsf?pid=diva2%3A1082029&dswid=8595".

Author's Contribution: The author developed the parameterized cells, physical verification rules, parasitic extraction flow and the device models based on TCAD simulations. He also wrote the manuscript.

• [Paper II] P. Chaourani, P. Hellström, S. Rodriguez, R. Onet and A. Rusu, "Enabling area efficient RF ICs through monolithic 3D integration," Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017, Lausanne, pp.

610-613.

Author's Contribution: The author performed the design-space exploration and devised the frequency-based partition scheme. He also designed the S3D receiver front-end and wrote the manuscript.

• [Paper III] P. Chaourani, S. Rodriguez, P. Hellström and A. Rusu, "Inductors in a Monolithic 3D Process: Performance Analysis and Design Guidelines," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 2, pp. 468-480, Feb. 2019.

Author's Contribution: The author analyzed the performance of S3D inductors and devised basic rules to allow the placement of bottom tier blocks under top-tier inductors in a S3D process. He also wrote the manuscript.

• [Paper IV] P. Chaourani, D. Stathis, S. Rodriguez, P. Hellström and A. Rusu, "A Study on Monolithic 3D RF/AMS ICs: Placing Digital Blocks Under Inductors," 2018 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 2018, pp. 1-3.

Author's Contribution: The author developed the design technology co-optimization flow to enable digital blocks under top-tier inductors and wrote the manuscript.

• [Paper V] P. Chaourani, P. Hellström, S. Rodriguez and A. Rusu, "A study on heterogeneous S3D integration: The impact of Ge transistors on S3D circuit design," in manuscript

Author's Contribution: The author has calibrated the TCAD models to match inhouse measurement results, and he has used TCAD to predict the performance of short-channel Ge transistors. He has also explored circuits that could benefit from a Ge-over-Si S3D integration and he has written the manuscript.

#### 1.7 Thesis Organization

The thesis is organized in seven chapters as follows:

- Chapter 1 provides a brief introduction to the topic of this thesis along with the state-of-the-art approaches in the field. The main motivations behind this work, as well as its main contributions are also presented.

- Chapter 2 introduces the main features of TSV-based and S3D ICs and a comparative study between them is carried out. It then discusses the processing

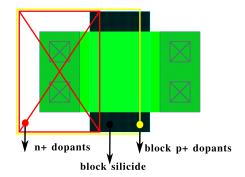

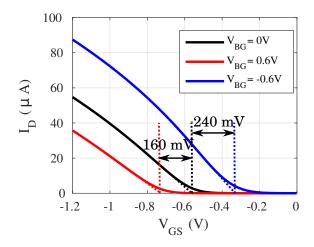

issues related to S3D integration and solutions to overcome them.